HyperLynx(三十一)高速串行总线仿真(三)

高速串行总线仿真(三)

1.从一个多层板工程中验证串行通道

2.在多层板中设置连接器模型

1.从一个多层板工程中验证串行通道

在本例练习中,将集中研究从芯片到插件形成的串行发射通道,并分析它的性能。

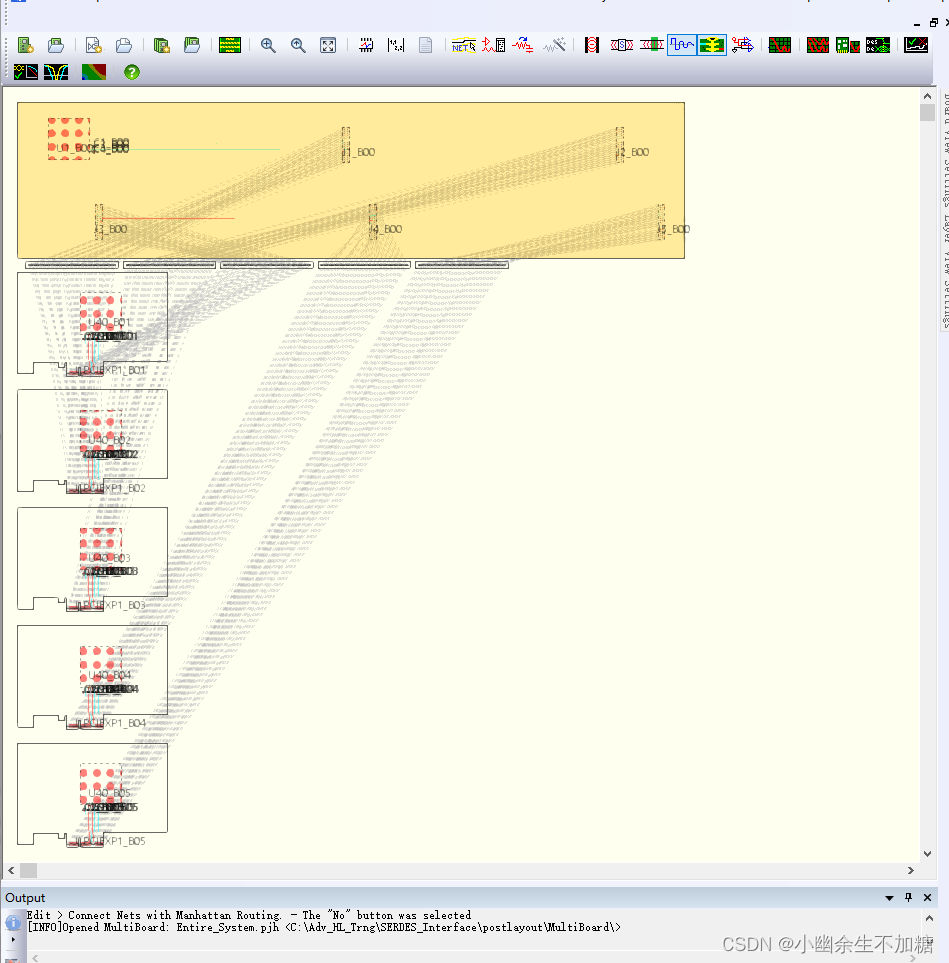

(1)打开 HyperLynx 软件,在软件主菜单单击“File”→ “Open MultiBoard project”

从以下路径打开 Entire_System.pjh 文件:C:\Adv_HL_Tmg \SERDES_Interface \postlayout \Multi-

Board,如图 所示。

(2)当打开设计遇到提示信息时,单击“No”按钮。

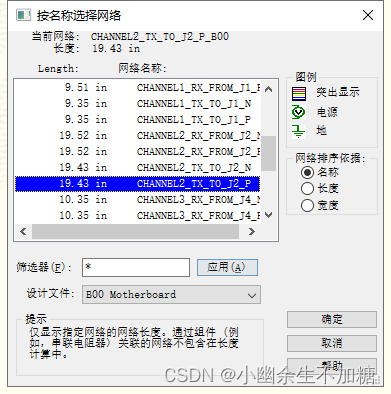

(3)选择网络“CHANNEL2_TX_TO_J2_P”,如图所示。

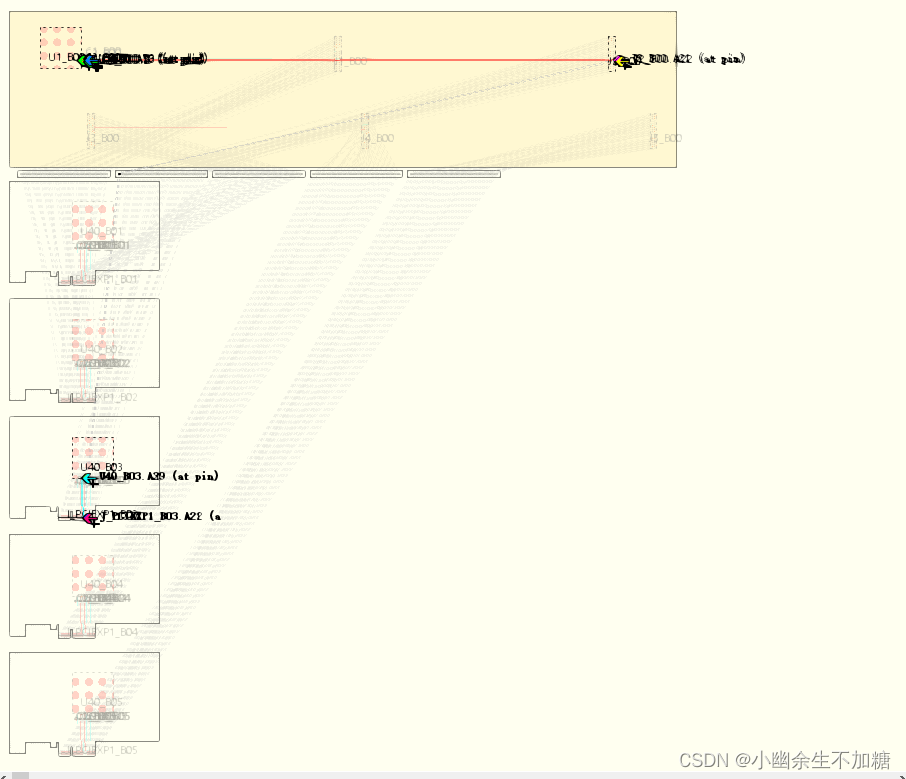

此时,一个IBIS模型已经分配好,接下来,将为主板上的缓冲器分配SPICE驱动模型。

(4)为U1.AT8/U1.AT9缓冲器分配 noDeE_trsnmtr.sp模型,如图所示。

浙公网安备 33010602011771号

浙公网安备 33010602011771号