ACE Bus

对于coherency transaction load操作,data来源:

1) 可以从其他cache master的cache line拿到,

2) 由interconnect中的buffer直接返回,或者interconnect发出的ReadNoSnoop transaction返回数据。

对于coherency transaction store操作,要求master:

1) 该数据所在的cache line的状态是unique;

2) 指定的transaction type,来保证第一点。

ACE所支持的coherency的协议是MOESI,也可以向下兼容MEI,MESI等,有的cpu处理器不支持SharedDirty(Owned),

Axaddr channel增加的信号:

AxBar[1:0], 01------Memory Barrier,对DMB指令的翻译。

10-------Sync Barrier,对DSB指令的翻译。

Axdomain[1:0],对于coherent trans,该信号,来指定snoop filter寻找cache copy的范围;

inner-shareable一般是同一个cpu cluster之间的cache coherent查询。

outer-shareable一般是所有的支持coherent的master,两个cpu cluster之间的cache coherent查询(如果只有一个outer-shareable domain)。

system,包括所有的master,但是对coherent的查询,与outer-shareable相同。

对于barrier trans,该信号,来决定barrier trans,经过interconnect需要propagate的范围,指定observer。

inner-shareable,表示该domain的所有master到interconnect的slave port都需要observe。

outer-shareable,表示所有cache-master到interconnect的slave port都需要observe。(如果只有一个outer-shareable domain)。

由于目前都是cpu cluster内一个interconnect,锁哥cpu cluster之间还有一个interconnect。

所以inner-shareable是cluster内部的trans,outer-shareable包括所有的cache master。

Axsnoop[3:0],指定snoop trans的类型。

RESP channel增加的信号:

RRESP[2],PassDirty,表示需要initial master来写入main memory,当前的master的cache line必须是Dirty state。

RRESP[3],IsShared,值为1,表示当前master的cache line的状态必须是在Shared state。

值为0,表示当前master的cache line的状态可以在unique state。

这两bit,在所有的rdata beat中都必须保持相同。

针对unique类的操作和cache maintainance的操作,IsShared为0。

ReadUnique,CleanUnique,MakeUnique。CleanInvalid,MakeInvalid.

针对read类操作,unique类操作,cache maintainance的操作,PassDirty为0。

ReadOnce,ReadClean。CleanUnique,MakeUnique。CleanShared,CleanInvalid,MakeInvalid。

不是coherent类型的操作,NoSnoop,Barrier,DVM,这俩bit必须为0。

ReadClean,ReadNotSharedDirty,ReadShared,返回的PassDirty,Isshared,可以根据情况toggle。

Read Ack signal:在RLAST之后,由master发出,表示该笔coherency 操作已经结束。

Write Resp signal,没有变化。

Write Ack signal:在Bvalid和Bready之后,由master发出。

1----coherency transaction:

coherency transaction可以分为几个transaction group:

1) NoSnoop----------Write/Read

2) Coherent----------Write/Read

Read,分为两大类,ReadOnce(No alloc),ReadShared / ReadClean / ReadNotSharedDirty(alloc)

Unique类的trans,ReadUnique(PE没有该cache line,partial cache line store),CleanUnique(PE有该cache line,partial),

MakeUnique(full cache line)。

Write,WriteUnique(partial store),WriteLineUnique(full cache store)

3) cache mantenance--------Read,Clean类型的trans,CleanShared,CleanInvalid,MakeInvalid

cache clean,表示将dirty cache data写入main memory;

cache invalid,表示将cache copy,invalid掉,之后的读写只能从main memory来拿数据。

4) Barrier-------------Write/Read,

5) Memory update-------Write,WriteClean(alloc),WriteBack(No alloc),WriteEvict,都是no snoop的trans。

对于read类型的snoop操作,主要是区分是否alloc,可以读取何种类型的cache line来区分。

对于write类型的snoop操作,主要分为unique类型的trans和write coherent类型的trans。

1) unique类型的trans,只是将该master下的cache line state置为UniqueDirty,使之满足store的条件。之后会通过memory update操作来更新memory。

ReadUnique,CleanUnique,MakeUnique,只是invalid其他master中的cache line。这个过程可以由cache master实现,也可以由interconnect来实现。

2) Write coherent类型的trans,相当于执行了CleanUnique以及WriteBack等操作。

WriteUnique = ReadUnique+writeBack。

各个操作过程中对initial master和其他cache master的影响。

memory update类型的前后cache state变化,WriteBack,state从Dirty-------Invalid;

WriteClean,state从Dirty--------Clean;

cache maintanance前后的cache state变化,CleanShared,initial master的state不变,其他master中的该cache变为invalid或者clean。

CleanInvalid,initial master的state不变,其他master中的该cache变为invalid。一般initial master的state也是invalid。

MakeInvalid,initial master的state不变,其他master中的该cache变为invalid。dirty不会更新main memory

Read类型的snoop trans,ReadClean,ReadNotShareDirty,ReadShared,initial master的state一般是invalid----UC/UD/SC等。

具体的state变化,主要看其他master的处理,interconnect的处理,以及interconnect返回给initial master的resp。

ReadOnce,initial master的state一般是invalid------invalid,一般是intiial master本身没有cache,拿过来之后也不会alloc新的cache。

Unique类型的snoop trans, ReadUnique,initial state一般从Invalid------UC/UD,其他master的该cache line变为invalid、

CleanUnique,initial state一般从SC/SD------UC/UD,其他master的该cache line变为invalid、 这两种unique,通常与partitial store配合使用。

MakeUnique,总是与full cache line store一起使用。两个操作之后,initial state一般从Invalid/SC/CD------UD,其他master的该cache line变为invalid、

Write类型的snoop trans,WriteUnique,initial master的state从Invalid/UC/SC-----Invalid/SC/SC,其他cache master中的cache line的state变为invalid。

在收到transaction的resp之后,cache line中的值必须变为新的值。进行partitial的store。

WriteLineUnique,initial master的state从invalid/UC/SC------Invalid/SC/SC,其他cache master中的cache line的state变为invalid。

在收到transaction的resp之后,cache line中的值必须变为新的值,进行full cache line store。

no snoop的操作,WriteBack,UD/SD-------Invalid。

WriteClean,UD/SD---------UC/SC,这两个操作都是在cache line已经dirty的情况下做的操作。

WriteEvict,UC/UD--------Invalid,只有在支持snoop filter的cache master中才支持。

ReadNoSnoop/WriteNoSnoop,表示更新一段non-shareable的main memory,cache state,可以是Invalid/UC/UD-------Invalid/UC/UD

2----snoop transaction:针对shareable-cacheable-memory属性的memory访问。

snoop transaction是指从interconnect到cache master的一组transaction的统称:cache master包括(拥有cache或者支持做DVM的master)

address channel:

interconnect的输出信号有:ACVALID,ACADDR,ACSNOOP,ACPROT。

cache master的输出信号有:ACREADY。

address channel中并没有size,length,id这些信号。因为snoop transaction的size与CDDATA size相同。

一个snoop的length必须是一个cache line的大小。最后一个beat的数据通过last来表征。

ACPROT[1]信号用来表征secure,non_secure world,cache coherent是区分secure与non_secure world。

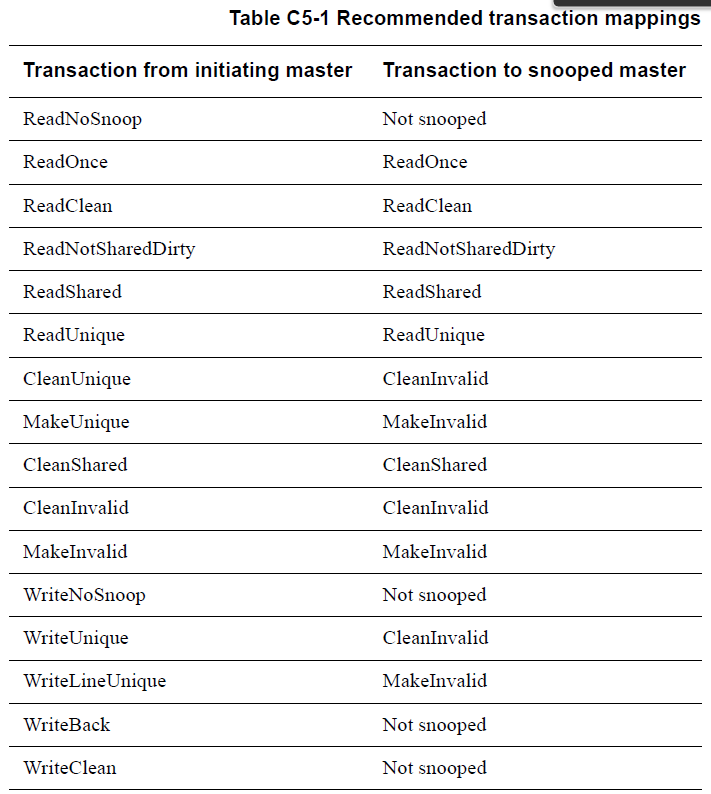

ACSNOOP信号的值,从coherency transaction到snoop transaction也有约束:

1),首先不支持no-snoop的trans,如ReadNoSnoop,WriteNoSnoop,WriteBack,WriteClean,Evict,是不会进行snoop的。

2),WriteUnique,被映射为其他cache master的CleanInvalid。(推荐)

WriteLineUnique,被映射为其他cache master的MakeInvalid。(推荐)

MakeUnique,被映射为其他cache master的MakeInvalid。(推荐)

CleanUnique,被映射为其他cache master的CleanInvalid。(推荐)

3),像ReadOnce,WriteUnique的操作,interconnect需要内部将不是cache line size的操作进行转换组装。

snoop resp channel:

interconnect的输出信号,CRREADY。

Master的输出信号,CRRESP,CRVALID。

CRRESP,共有5bit:

[0]:是否传输data,一般的原则是

1:Read snoop trans,必须传输data,ReadOnce,ReadClean,ReadNotShareDirty,ReadShared,ReadUnique.

2:对于一些非read操作,如果cache 为dirty,传输data。cache state为clean时,可传可不传。

[1]:Error bit,表征当前cache master内部的cache line数据是错误的。

[2]:PassDirty bit,除了MakeInvalid,所有cache state为dirty的cache master都必须在resp中将该位置1。

表征,写入main memory必须由interconnect或者RN cache master来完成。

ReadNotSharedDirty,ReadShared,ReadUnique,写入main memory可以传给RN cache master。

ReadClean,必须由interconnect来完成写入main memory。

其他的snoop trans,可以implement defined。

[3]:is shared bit,表示RN cache master获得一个cache line的copy。

[4]:is unique bit,表示cache line在snoop访问之前的state是unique状态。

snoop data channel:

interconnect的输出信号,CDREADY。

cache master的输出信号,CDVALID,CDDATA,CDLAST。

CDDATA不支持byte strobe的功能,只能由interconnect返回需要的正确的data个数。

snoop channel中的ready和valid的依赖关系与AXI中的相同。

arm建议的coherency transaction到snoop transaction的mapping 关系:

一个coherency transaction可以被mapping为多种snoop trans(如ReadUnique),但是还是建议,保留多种,这样简便

master处理。

3-----snoop transaction于coherency transaction之间的关系:

1) non-blocking,同一个master在自己的coherency trans和interconnect发过来的snoop trans之间的前后关系:

1, master必须完成所有的snoop trans,在AR channel的操作和AWchannel的WriteUnqiue,WriteLineUnique,之前。

2. 在完成port上的snoop trans之前,master可以在等待WriteNoSnoop,WriteBack,WriteClean,Evict等操作。

不能等aw channel的WriteUnique,WriteLineUnique完成。

总结起来,AR channel的trans可以等AC channel的trans,AC channel的trans可以等AW channel的trans(除了写Unique)。

2) overlapping write,在一个shareable memory中,两个master同时相同一个cache line进行store操作。

由interconnect来保证Write操作的sequence order。

WriteUnique,WriteLineUnique,一般都用在master是non-cache的情况下,如果用在cache master中,必须保证此时可以处理所有的snoop transaction。

而且,WriteBack,WriteClean,必须和WriteUnique,WriteLineUnique完全隔离开来,一组完成之后,另一组才可以开始执行。

WriteClean,WriteBack,过程中收到snoop trans,会挂住该snoop,直到自己的trans结束,snoop response必须PassDirty deassert,IsShared assert。

主要涉及的三个snoop transaction是ReadUnique,CleanInvalid,MakeInvalid。

当前发出snoop trans,但仍未完成的master称为Master2,由interconnect发到Master2的snoop trans的发送者,称为Master1。

Master2,发出ReadUnique,Master1经Interconnect发出的是三个中的任何一个:

在自己的snoop port收到snoop trans的Master2,必须先完成该snoop trans;自己有cache copy必须invalid。

之后interconnect将最新的data返回给Master2,Master2完成自己的partitial/full store。

Master2,发出MakeUnique,Master1经Interconnect发出的是三个中的任何一个:

在自己的snoop port收到snoop trans的Master2,必须先完成该snoop trans;自己有cache copy必须invalid。

之后interconnect将最新的data返回给Master2,Master2完成自己的partitial store。

Master2,发出CleanUnique,Master1经Interconnect发出的是三个中的任何一个:

在自己的snoop port收到snoop trans的Master2,必须先完成该snoop trans;自己有cache copy必须invalid。

之后interconnect返回resp(unique操作并没有完成,因为Master2本身没有alloc 该cache line),

Master2重新发送ReadUnique,之后Master2完成自己的full cache line store。

4------CCI的interconnect的几部分主要工作:

1) sequenceing自己收到的coherency trans和snoop trans,

每个cache master可以发送多个outstanding req,并同时接受多个snoop transaction,其中对于

同一个cache line的顺序由interconnect决定,arb method需要自己实现。

其中arm 规定的rule:

1. master发出coherent trans但是还没有收到resp,此时收到针对该cache line的snoop trans的访问,snoop trans规定为ordered first。

2. master发出coherent trans并且已经收到resp,之后在收到该line的snoop trans,coherent trans规定为ordered first。

对于同一个cache line,coherent trans必须等到ACK信号给出之后,interconnect才能发snoop trans。

snoop trans必须等到CRRESP信号给出之后,interconnect才能给coherent trans的resp。

2) 自己根据initial master的trans,发送snoop trans,并正确返回resp给initial master。

interconnect发出snoop trans,是根据自己内部的directory,加coherent trans的类型来定义自己发出的snoop trans类型和个数。

多个snoop trans之间一般是顺序的。

1. ReadNoSnoop,WriteNoSnoop,WriteBack,WriteClean,Evict是不会让interconnect发出snoop trans的。

2. ReadOnce,ReadClean,ReadNotSharedDirty,ReadShared对directory中有cache copy的master发送snoop trans。

(1) 有一个master的CRRESP返回CRRESP[4],wasunique,则所有master的snoop trans结束。

(2) 拿到一个cache copy。

(3) 所有的cache copy被遍历。

3. Unique trans, cache maintance, Write trans对directory中有cache copy的master发送snoop trans。

(1) 有一个master返回CRRESP[4],wasunique,则所有master的snoop trans结束。

(2) 所有的cache copy被遍历。

(3) 针对CleanShared trans,如果CRRESP[2]返回PassDirty,所有master的snoop trans结束。

针对Unique和cache maintance的trans,如果CRRESP返回PassDirty,interconnect对其他的cache master可以发送MakeInvalid snoop trans。

interconnect回给initial master的resp:

ARchannel的IsShared:

1. snoop trans的IsShared置位,一般给initial master的IsShared 置位。

2. 如果snoop trans的Data Transfer assert,一般给initial master的IsShared不会置位。

3. snoop trans的WasUnique被置位,1不满足的情况下,IsShared不会置位。

ARchannel的PassDirty:

1. 置位的coherent trans,主要是ReadNotSharedDirty,ReadShared,ReadUNique。

如果snoop trans的CRRESP中的PassDirty置位,则需要interconnent更新main memory或者返回PassDirty给initial master。

3) interconnect跟main memory之间的读写:

Read:在Read coherent trans在shared cache master中没有找到data的情况下,interconnect需要发出main memory read。

main memory read可以等所有的snoop trans完成之后在发出,也可以与snoop trans一起发出。

如果read trans在snoop trans没完成之前就发出:

1. snoop trans给出data,main memory中的数据丢弃。

对同一地址cache line的read和WriteBack,WriteClean的coherent trans必须是有序的。

Write:interconnect必须保证所有的写操作都是有序的,无论cache line是否重叠。通过返回PassDirty的顺序来控制。

1. 对于partitial cache line write,如果snoop trans返回dirty data,需要interconnect进行merge。

2. 对于ReadOnce/Clean/Shared/NotSharedDirty CleanUnique/Shared/Invalid,需要interconnect自己进行main memory更新。

如果interconnect没有收到PassDirty的CRRESP,一定不可以写main memory。

arm建议interconnect尽量不进行write操作,尽量传递PassDirty。

4) interconnect还需要实现对不同cache line size的转换。

5------cache maintenance trans的应用:

只有在所有outstanding trans都结束之后,才能发送cache maintenance trans,而且还有两点state要求。

1. 对于CleanShared,CleanInvalid,在发出trans之前,该cache line的状态必须是clean的,

如果dirty,必须先发WriteBack,WriteClean操作。在两个操作之前,需要发Unique trans。

2. 对于CleanInvalid,MakeInvalid,在发出trans之前,该cache line的状态必须是invalid的,

cache maintenance trans一般穿插在coherent domain和non-coherent agents access之间。

因为coherent与non-coherent的交织,可能导致cache中的新的数据,non-coherent的agent读不到。

这样的访问的sequence:

non-coherent之前采用cache clean操作来更新main memory。

non-coherent之后采用cache invalid来使得之后的读写直接读取main memory。

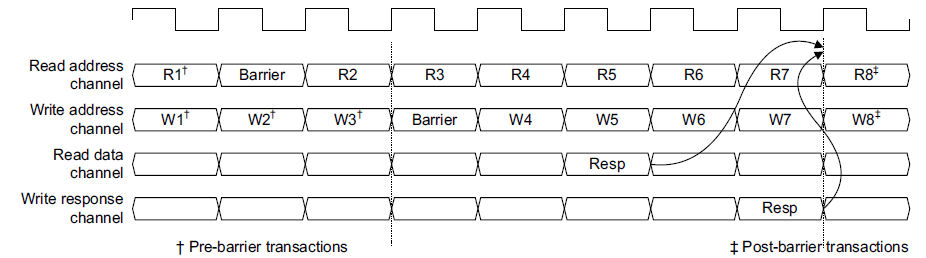

6------Barrier trans的应用:

Barrier主要针对domain之间的memory-base communicate,可以分为Read Barrier,Write Barrier。

1. 任何address channel中比Barrier先issue的trans,都称为Before Barrier trans(比某个address channel的Barrier先issue就可以),

在Read Barrier,Write Barrier两个resp之后issue的trans,都称为After Barrier trans。

Barrier trans必须在两个channel中都issue,没有data传输,resp必须是0。

2. AxBar信号,一共两bit,低位表示区分memory Barrier,Sync Barrier。

高位表示该trans是否受到Barrier trans的影响。

3. AxDomain信号,区分inner shareable domain,outer shareable domain。

一个system,一般包括domain boundariers和bi-section boundaries(不清楚不做介绍)。

domain boundary是domain中的所有master公用的一个downstream的interface。即同一个inner domain中访问一个地址,多个master也只能用这一个interface。

domain boundary与interconnect能返回barrier resp有关:

memory barrier与non-system的Sync barrier,可以在domain boundary上或者更加downstrream的地方返回resp。

针对system的Sync barrier,必须等到end point才能返回resp。

4. Barrier trans的resp,由interconnect返回,与system中interconnect的位置有关,interconnect的实现方式有:

(1) interconnect block掉其他所有的trans,然后不断向下发送Barrier trans,最后将所有barrier的resp merge在一起,

之后,返回给initial master barrier resp,并去掉所有的block。

(2) interconnect block掉所有的trans,并等待所有的trans,都返回resp之后,在给initial master返回Barrier resp,并移除block。

(3) interconnect block掉所有的与Barrier地址有重叠部分的trans,之后给initial master提供barrier resp

5. memory barrier,由dmb指令来实现,

memory sync barrier,由dsb指令来实现,

ARM中的ISB指令,并不直接映射到某一个bus trans中,只是将处理器流水线停掉,来保证之后的指令从cache或者memory中读取。

6. 发送barrier的master需要保证,barrier的id与其他正常trans的id不同,这样方便区分返回的resp。

Barrier trans发送出去,但是resp回来之前的trans,是不保证顺序的,不受Barrier影响。这些trans都是当前domain之外的trans。

由于Barrier trans发出之后,之后的trans就会被interconnect block住,所以当Read,Write有前后的约束的时候,必须最后才发相应的barrier。

比如需要mmu进行table walk,那就不能在之前发Read barrier。否则总线会被锁死。

对于有cache的master,如果load必须在barrier之后,则master不能发出coherent trans从Valid cache中读取,必须等到barrier的resp。

如果store必须在barrier之后,则master不能发出coherent trans向Unique cache中写入,必须等到barrier的resp

7------Exclusive trans的应用:

用来实现多核之间的同步,类似于软件实现mutex和semaphore。

多核之间cache coherence可以保证一部分的多核同步,bus上根本不会出现exclude trans。

每个master内部实现一个local monitor来snoop其他master的exclude trans,保证一个core exclude load之后,另一个core不能exclude store。

但是在存在non-cached master时,bus上会出现exclusive trans。

通过interconnect上的PoS的monitor,来保证同一memory,对多个exclusive store trans的同步。

Exclusive的实现都是通过Exclusive sequence的形式来实现的,先进行LDREX指令,在执行STREX指令。

Exclusive Load,根据cache状态来分:

Invalid,必须通过ReadClean,ReadShared,先拿到cache中的数据,不能使用ReadUnique,ReadNotSharedDirty,这样会invalid掉其他的cache中的数据。

with ARLOCK asserted。

SharedClean,Unique state,master的exclusive load可以不需要。

浙公网安备 33010602011771号

浙公网安备 33010602011771号