3.1 介绍

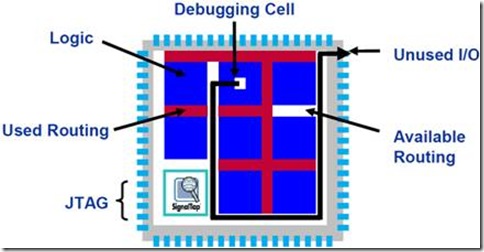

SignalProbe是唯一不需要使用JTAG的调试工具。由下图可以看出,相比于直接在工程中引出一个测试引脚,SignalProbe不改变原有设计。同时SignalProbe使用多余的IO引脚来输出信号。

一般在以下几种情况使用SignalProbe:

(1)有外部测试设备的存在;

(2)目标设计器件为FPGA或者CPLD;

(3)器件内部资源剩很少或者根本没有剩余;

(4)有剩余的IO引脚;

(5)无需等待过长的编译时间,很容易将内部信号布线到调试端口;

(6)无需JTAG。

以前的设计一般都保留有测试引脚,调试阶段这些调试引脚成为了设计的一部分,而使用SignalProbe可以尽量使测试和设计分离。

使用SignalProbe好处有:

(1)简单易用;

(2)Fitter来处理SignalProbe的信号布线,所以设计者只需指定源节点(sourece node)和目标引脚即可,编译报告会报告从内部节点到引脚的延迟时间。

(3)加入SignalProbe后不会影响已编译的设计的布局,被测试的信号的Fmax不会改变,布线可能会有些许更改。

(4)可以结合增量编译,节省编译时间。

总的来说,SignalProbe进行调试是设计没有留JTAG的无奈之举,但是有些场合不支持SignalTapII的CPLD则只能选择SignalProbe。而且当器件的资源利用率很高,即已经没有足够的资源在设计中加入SignalTapII的时候也只能选择SignalProbe。当然SignalProbe有个最大的好处除了占用很少的资源外就是设计无需重新编译,适配器会完成探测源和目标引脚之间的布线,而且重新全编译之后原来加入的SignalProbe会自动消失。

SignalProbe的主要使用步骤如下:

1)保留足够的测试引脚;

2)编译设计(可选),如果设计已经全编译,则无需编译;

3)分配SignalProbe source;

4)如果需要加入流水线寄存和时钟;

5)执行SignalProbe编译;

6)Program device;

3.2 设计流程

(1)全编译

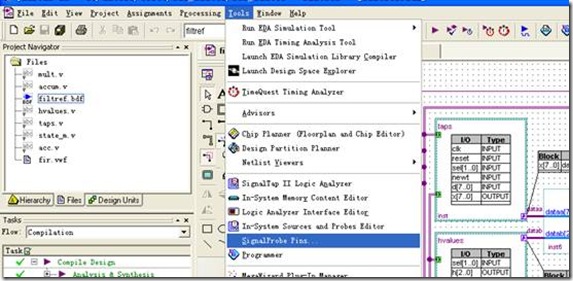

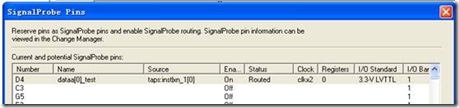

使用SignalProbe之前需要全编译工程。打开SignalProbe Pins,如图。

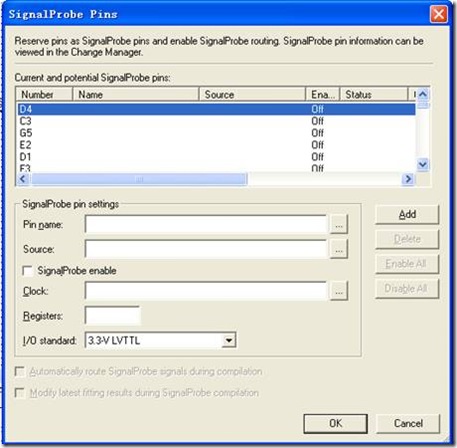

下图为SignalProbe Pins的界面。【Current and potential SignalProbe pins】栏中Number列出的为未使用的引脚,选择合适的引脚作为探针输出。

(2)分配SignalProbe source

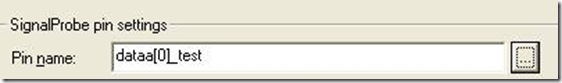

本节主要论述【SignalProbe pin settings】栏的【Pin name】和【Source】。

【Pin name】:

Pin name是所设置的输出引脚的名字,Node Finder里的Filter选Design Entity(默认)。选择好以后注意改名,因为他和被选择信号的名字重复会导致出错;也可以不用Node Finder而直接命名。

【Source】:

Source node name—Specifies the signal name that you want to route to the SignalProbe output pin in the Current and potential SignalProbe pins list.

Source可以是组合逻辑的节点(node)、寄存器、LEs 、 Memory block、 DSP block outputs或者后适配网表的引脚(pin)。有些内部节点可能无法找到,因为该节点可能在综合时被优化掉,或者该节点无法布线到SignalProbe的引脚。在Source栏的Node Finder里的Filter选SignalProbe(默认)。

(3)增加流水线寄存器

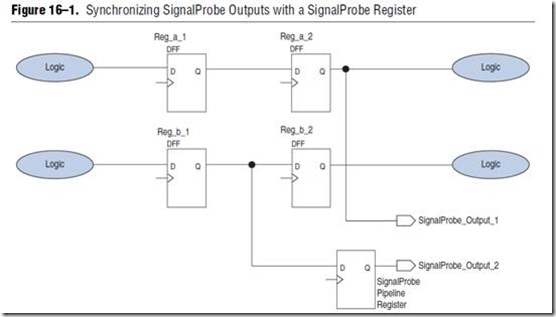

可以手动设置从SignalProbe Source到SignalProbe Pin的寄存器个数来同步数据和控制SignalProbe输出的恢复时间(latency)。SignalProbe自动把他们插入其布线路径中。

当添加了寄存器后,SignalProbe会尝试对寄存器进行布局来满足时序:把寄存器放置在靠近SignalProbe Source的地方来满足Fmax的要求,放置在靠近IO的地方来满足Tco的要求。如下图所示。

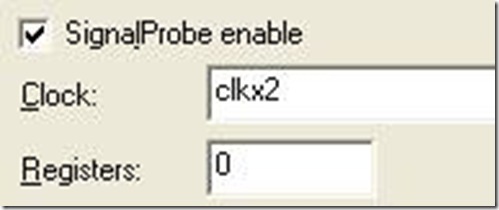

如需要设置上述寄存器,在SignalProbe Pins里勾选【SignalProbe enable】。

参数说明:

Clock—Specifies the clock signal name to use as a clock to register the output of the SignalProbe node. You must specify a clock signal name and the number of registers to use if you want to register the output of the SignalProbe node.

Registers—Specifies the number of registers to insert before the output of the SignalProbe pin. You must specify the number of registers to use and a clock signal name if you want to register the output of the SignalProbe node.

(4)确认

3.3 执行SignalProbe编译

(1)SignalProbe编译

通过SignalProbe编译来对设置好的SignalProbe引脚进行布线。当前设计的布局布线仍保留。SignalProbe编译完成如下功能:

选择Processing -> Start -> Start SignalProbe Compilation ![]()

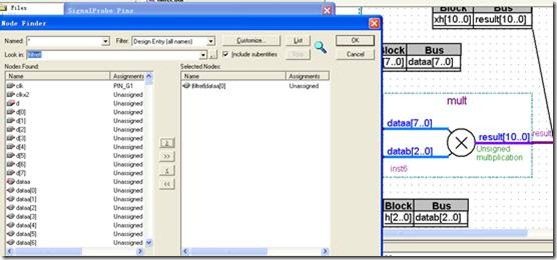

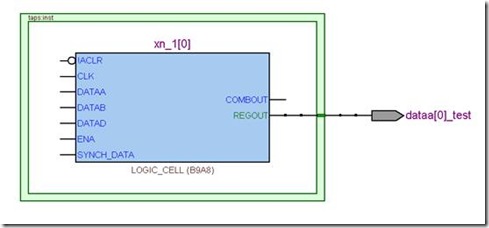

查看Tecnology Map Viewer。选中dataa[0]_test,右键->filter,选source。如下图所示,探针已经加入。

(2)分析SignalProbe布线错误

下面提到的问题可能导致编译出错:

(1)SignalProbe source到SignalProbe引脚之间因布线拥挤(routing congestion)而无法布线。

(2)添加的SignalProbe source不存在或无效。

(3)输出引脚不可用。

如果布线拥挤导致无法编译成功,可以在SignalProbe Pins里勾选“Modify latest fitting results during SignalProbe compilation”。不过此设置会改变原设计。

(3)理解SignalProbe编译结果

涉及到SignalProbe的编译报告有两处:

(1)The fitting results and status

(2)The timing results

浙公网安备 33010602011771号

浙公网安备 33010602011771号