EDA 学习笔记之 lef 文档笔记1:基础介绍

@

lef 文件介绍

LEF(Library Exchange Format)是对标准单元版图进行抽象描述的文件,用于自动布局布线(P&R)工具。LEF 文件具有可读的 ASCII 格式,包括用于互联的详细的 Pin 信息,以及 layer、via、placement site type、macro cell 定义,但不包括 poly、diffusion 这些底层 layer。

格式的通用规则

● 标识符如 net name 、cell name 都限制在2048字符以内。

● 距离定义单位为微米。

● 距离精度由 UNITS 语句控制。

● LEF 语句以分号(;)结。

● 语句的最后一个字符与分号之间必须有一个空格。

LEF文件包括两部分:1. 工艺描述部分 和 2. 单元(cell)描述部分。

所以可以将库信息分成两个文件,一个是 “technology” LEF 文件,另一个是 “cell library” LEF 文件。

technology LEF file:工艺 LEF 文件包含设计的所有工艺信息,例如布局布线设计规则以及层的处理信息。一个 technology LEF 文件可以包括以下任何一个LEF语句:

[VERSION statement]

[BUSBITCHARS statement]

[DIVIDERCHAR statement]

[UNITS statement]

[MANUFACTURINGGRID statement]

[USEMINSPACING statement]

[CLEARANCEMEASURE statement ;]

[PROPERTYDEFINITIONS statement]

[FIXEDMASK ;]

[LAYER (Nonrouting) statement

| LAYER (Routing) statement] ...

[MAXVIASTACK statement]

[VIA statement] ...

[VIARULE statement] ...

[VIARULE GENERATE statement] ...

[NONDEFAULTRULE statement] ...

[SITE statement] ...

[BEGINEXT statement] ...

[END LIBRARY]

**cell library LEF file **:单元库 LEF 文件包含设计所需的宏和标准单元信息。 库LEF文件可以包含以下任何LEF语句:

[VERSION statement]

[BUSBITCHARS statement]

[DIVIDERCHAR statement]

[VIA statement] ...

[SITE statement]

[MACRO statement

[PIN statement] ...

[OBS statement ...] ] ...

[BEGINEXT statement] ...

[END LIBRARY]

工艺描述

technology lef 包含以下内容:

- 工艺中可用的层(Layer),只包含在 P&R 过程中用到的层。

- 影响 P&R 操作的部分设计规则,例如金属最小线宽和间距。

- 库设计者自定义的布线规则,如选择的布线间距值、金属布线的首选方向或所用通孔的几何描述(这里的“通孔”还包括连接到切割层(cut layer)的两层金属中所需的金属延伸(extension))。

- (可选的)库中各层的电气特性,例如最大电流、所用金属层的方块电阻。

示例:

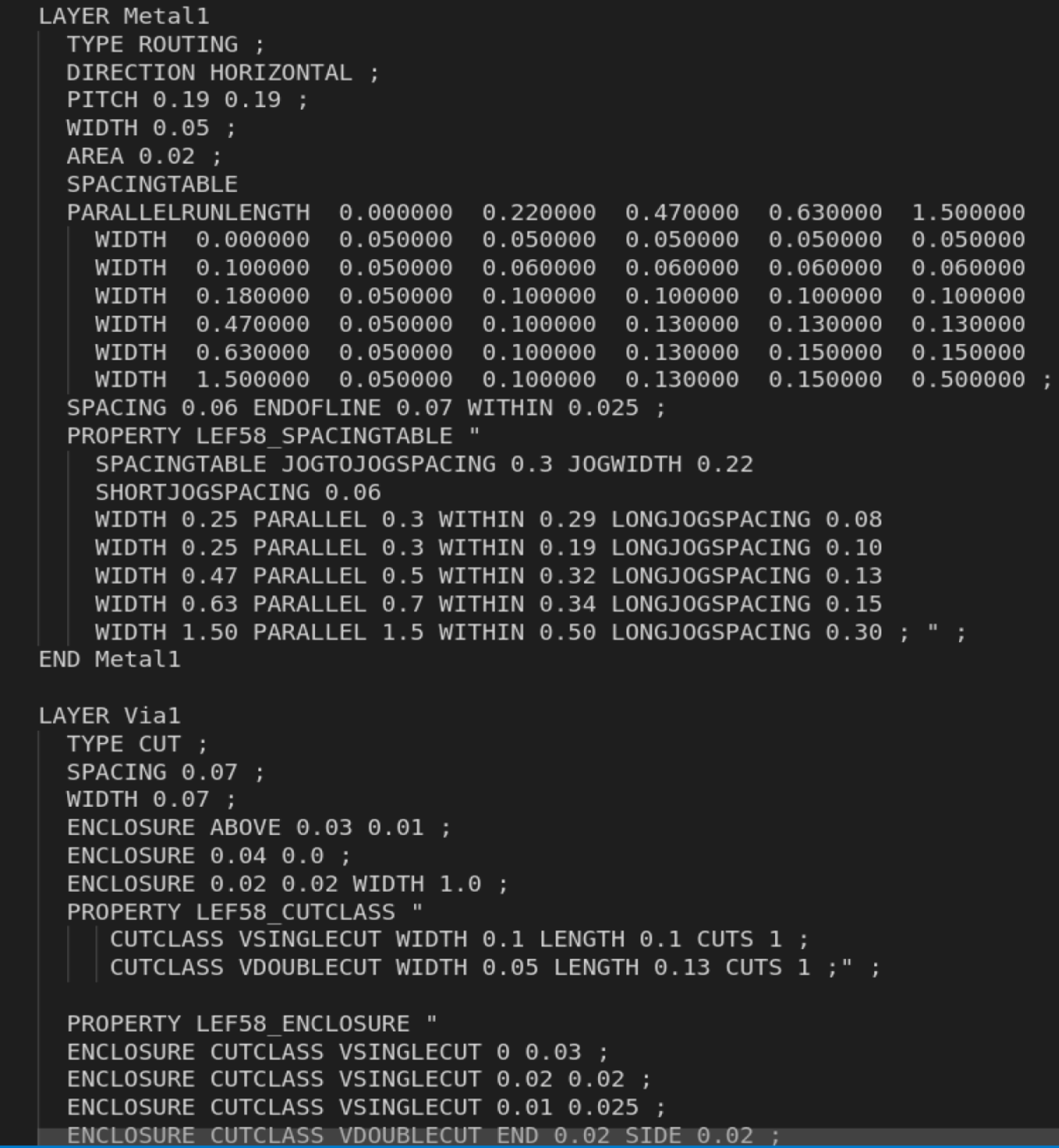

layer 定义

// 版本说明

VERSION 5.5 ;

// LEF 区分格式大小写。

NAMESCASESITIVE ON ;

// 设置定义bus标志符,端口名称为X<1>,X<2>,...X<n> 将看作bus

BUSBITCHARS "< >" ;

UNITS

// 设置定义 1 微米分成100个unit, 即为单位长度的值。

DATABASE MICRONS 100 ;

END UNITS

// 设置定义层为金属1层,同时下面是对定义的金属1层的具体细节设置。

LAYER metal1

// 定义 metal1 用于 routing

TYPE ROUTING ;

// 定义金属1层在作为布线金属时,默认线宽为 0.1 um

WIDTH 0.10 ;

// 定义金属1层的走线间距为 0.3 um

SPACING 0.30 ;

// 定义金属1层到通孔的距离为1.2 ; PITCH 1.2 1.2 ; // 定义x 和 y 的距离

PITCH 1.2 ;

// 金属1层走线方向为水平走线。

DIRECTION HORIZONTAL ;

// 该设置定义每一个方块(1x1um)的电容大小。

CAPACITANCE CPERSQDIST 0.000140 ;

// 设置每一个金属的方块电阻。

RESISTANCE RPERSQ 0.04 ;

END metal1

LAYER via1

// 定义via为布局布线下的CUT类型,即Metal1 和 Metal2 的通孔

TYPE CUT ;

END via

// 该设置定义金属2,与上面的金属1设置类似。

LAYER metal2

TYPE ROUTING ;

WIDTH 0.30 ;

SPACING 0.30 ;

PITCH 1.20 ;

// 该设置与金属1层有区别,走线方向为垂直。

DIRECTION VERTICAL ;

CAPACITANCE CPERSQDIST 0.000120 ;

RESISTANCE RPERSQ 0.020000 ;

END metal2

via 定义

// 该设置定义怎样产生通孔,这里生成默认情况下metal 与poly1 之间的通孔。

// 这里产生的通孔在上下两层都是default width时产生的,

// 当上下两层不是默认宽度时; 有另外的规则定义。

VIA M1_POLY1 DEFAULE

LAYER poly1 ;

// 设置定义Poly1(多晶) 的形状。

RECT -0.30 -0.30 0.3 0.3 ;

LAYER cont ;

// 设置定义cont(接触孔)的形状。

RECT -0.15 -0.15 0.15 0.15 ;

LAYER metal1;

// 设置定义metal1的形状

RECT -0.3 -0.3 -0.3 0.3 ;

END M1_POLY1

// 该设置定义默认情况下metal1 与 metal2 之间的通孔。与上面通孔设置类似。

VIA M2_M1 DEFAULT

LAYER metal1 ;

RECT -0.30 -0.30 0.30 0.30 ;

LAYER via ;

RECT -0.15 -0.15 0.15 0.15 ;

LAYER metal2 ;

RECT -0.30 -0.30 0.30 0.30 ;

END M2_M1

// 该设置定义metal2 与 metal3 之间的通孔。

VIA M3_M2 DEFAULT

LAYER metal2 ;

RECT -0.30 -0.30 0.30 0.30 ;

LAYER via2 ;

RECT -0.15 -0.15 0.15 0.15 ;

LAYER metal3 ;

RECT -0.30 -0.30 0.30 0.30 ;

END M3_M2

// 与前面通孔设置不同,该设置定义在非默认情况时通孔的生成规则。

VIARULE VIAGEN21 GENERATE

LAYER metal1 ;

DIRECTION HORIZONTAL ;

OVERHANG 0.3 ;

metaloverhang 0.0 ;

LAYER metal2 ;

DIRECTION VERTICAL ;

OVERHANG 0.3 ;

metaloverhang 0.0 ;

LAYER via ;

RECT -0.15 -0.15 0.15 0.15 ;

SPACING 0.6 BY 0.6 ;

END VIAGEN21

VIARULE 定义通孔生成规则,表示的是实际使用的通孔的模板。布线时,不同层的线连接时需要打通孔,不同的情况需要不同的通孔生成,生成什么样的通孔由 LEF 内的通孔生成规则决定。

site 定义

site 是布局布线工具识别单元中最小的几何单位,一个设计中可能有几种site,site standard 指标准单元的site,site IO 指 IO pad 的site。

一般说来,cell 的高度是一定的,等 于site 的高度,cell 的宽度是site 的整数倍。

// 该设置定义各种site,此处定义标准单元的site。

SITE standard

SYMMETRY y ;

CLASS core ;

SIZE 1.20 BY 10.80 ;

END standard

// 该设置定义IO 单元的site。

SITE IO

SYMMETRY y ;

CLASS pad ;

SIZE 21.05 BY 70.80 ;

END IO

// 该设置定义芯片四个拐角上的pad 的site。

SITE corner

CLASS pad ;

SIZE 70.80 BY 70.80 ;

SYMMETRY y r90 ;

END corner

// 该设置定义硬核单元block 的site,用于block,如RAM/ROM, HardIP。

SITE SBlockSite

CLASS core ;

SIZE 1.00 BY 1.00 ;

END SBlockSite

cell 描述

非工艺 lef 的文件通常包含:

- 单元的形状和大小,由其各自的边界定义。

- 管脚(pins)的位置、管脚所在的层,以及同一节点中其他形状的几何描述。

- 障碍物(obstruction)的详细描述,即互联层中不属于任何特定引脚的形状,但禁止同一层中的布线轨道通过。

// 该设置定义单元 AOI21_B 的LEF信息。

MACRO AOI21_B

// 该设置定义原点坐标。

ORIGIN 0.00 0.00 ;

// 该设置定义单元大小,单位为um

SIZE 6.00 BY 10.80 ;

// 该设置定义工具可以在x y 方向旋转摆放该单元。

SYMMETRY x y ;

// 该设置定义standard site, 该设置说明该单元类型为标准单元,

// 其他类型还有IO,则是SITE为IO。

SITE standard ;

// 该设置定义该单元是在芯片内核中使用而不是可以放置在IO的位置。

CLASS CORE ;

// 该设置定义电源的名称 pin vdd。

PIN vdd

// 该设置定义vdd 是用于power。

USE POWER ;

// 该设置定义vdd 是输入PIN脚。

DIRECTION INPUT ;

SHAPE FEEDTHRU ;

PORT

// 该设置定义该单元的 vdd 的形状。

LAYER metal1 ; // 该设置定义 vdd 的金属1层RECT 矩形形状参数。

RECT 0.00 9.15 6.00 10.65 ;

END

END vdd

// 该设置定义地线名称 pin gnd。

PIN gnd

// 该设置定义 gnd 用于地。

USE GROUND ;

// 该设置定义 gnd 是输入PIN脚。

DIRECTION INPUT ;

SHAPE ABUTMENT ;

PORT

LAYER metal1 ; // 该设置定义 gnd 的金属1层RECT 矩形形状参数。

RECT 0.00 0.15 6.00 1.65 ;

END

END gnd

// 该设置定义PIN脚Y。

PIN Y

// 该设置定义Y 是输出端。

DIRECTION OUTPUT ;

PORT

LAYER metal1 ;

// 该设置定义Y 在金属1层的形状。

RECT 4.12 2.32 4.28 2.48 ;

RECT 5.32 8.32 5.48 8.48 ;

RECT 5.32 7.12 5.48 7.28 ;

RECT 5.29 5.89 5.51 6.11 ;

RECT 5.29 4.69 5.51 4.91 ;

RECT 5.29 3.49 5.51 3.71 ;

LAYER cont ;

RECT 4.05 3.15 4.35 3.45 ;

RECT 4.05 2.25 4.35 2.55 ;

RECT 5.25 8.10 5.55 8.40 ;

RECT 5.25 7.20 5.55 7.50 ;

END

END Y

OBS

// 该设置定义OBStruct阻塞的参数, 即下面定义的区域不可以布线(这里是metal1)。

LAYER metal1 ;

RECT 5.09 1.95 5.85 2.71 ;

RECT 5.09 3.29 5.85 3.91 ;

RECT 5.09 4.49 5.85 5.11 ;

RECT 5.09 5.69 5.85 6.31 ;

RECT 5.09 6.89 5.85 7.51 ;

// 该设置定义布局布线工具不可打孔的地方。

LAYER via ;

RECT 5.28 7.08 5.52 7.32 ;

RECT 5.28 8.28 5.52 8.52 ;

RECT 4.08 2.28 4.32 2.52 ;

END

END AOI21_B

END LIBRARY

Layer (Cut)

通过分配名称和设计规则来定义每个 cut 层。每个 cut 层都必须分开定义。由低而上的顺序中定义图层。例如:

poly masterslice

cut01 cut

metal1 routing

cut12 cut

metal2 routing

cut23 cut

metal3 routing

......

就是 poly + via + metal1 + via1 + metal2 + via2 +...多层叠加,cut 层实际上就是用来定义 vias的。

语法

LAYER layerName

TYPE CUT ;

[MASK maskNum ;]

[SPACING cutSpacing

[CENTERTOCENTER]

[SAMENET]

[ LAYER secondLayerName [STACK]

| ADJACENTCUTS {2 | 3 | 4} WITHIN cutWithin [EXCEPTSAMEPGNET]

| PARALLELOVERLAP

| AREA cutArea

]

;] ...

[SPACINGTABLE ORTHOGONAL

{WITHIN cutWithin SPACING orthoSpacing} ... ;]

[ARRAYSPACING [LONGARRAY] [WIDTH viaWidth] CUTSPACING cutSpacing

{ARRAYCUTS arrayCuts SPACING arraySpacing} ... ;]

[WIDTH minWidth ;]

[ENCLOSURE [ABOVE | BELOW] overhang1 overhang2

[ WIDTH minWidth [EXCEPTEXTRACUT cutWithin]

| LENGTH minLength]

;] ...

[PREFERENCLOSURE [ABOVE | BELOW] overhang1 overhang2 [WIDTH minWidth] ;] ...

[RESISTANCE resistancePerCut ;]

[PROPERTY propName propVal ;] ...

[ACCURRENTDENSITY {PEAK | AVERAGE | RMS}

{ value

| FREQUENCY freq_1 freq_2 ... ;

[CUTAREA cutArea_1 cutArea_2 ... ;]

TABLEENTRIES

v_freq_1_cutArea_1 v_freq_1_cutArea_2 ...

v_freq_2_cutArea_1 v_freq_2_cutArea_2 ...

...

} ;]

[DCCURRENTDENSITY AVERAGE

{ value

| CUTAREA cutArea_1 cutArea_2 ... ;

TABLEENTRIES value_1 value_2 ...

} ;]

[ANTENNAMODEL {OXIDE1 | OXIDE2 | OXIDE3 | OXIDE4} ;] ...

[ANTENNAAREARATIO value ;] ...

[ANTENNADIFFAREARATIO {value | PWL ( ( d1 r1 ) ( d2 r2 ) ...)} ;] ...

[ANTENNACUMAREARATIO value ;] ...

[ANTENNACUMDIFFAREARATIO {value | PWL ( ( d1 r1 ) ( d2 r2 ) ...)} ;] ...

[ANTENNAAREAFACTOR value [DIFFUSEONLY] ;] ...

[ANTENNACUMROUTINGPLUSCUT ;]

[ANTENNAGATEPLUSDIFF plusDiffFactor ;]

[ANTENNAAREAMINUSDIFF minusDiffFactor ;]

[ANTENNAAREADIFFREDUCEPWL

( ( diffArea1 diffAreaFactor1 ) ( diffArea2 diffAreaFactor2 ) ...) ; ]

END layerName

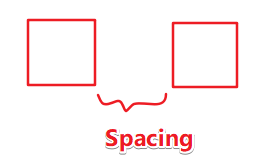

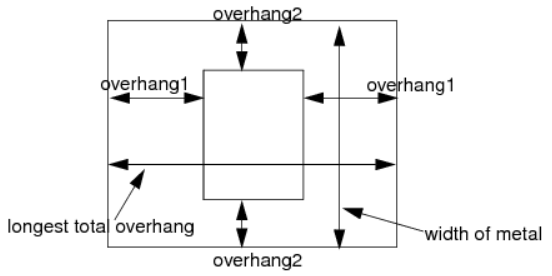

其中,width 用于定义通孔宽度,spacing 相关语句定义各种情况下,通孔之间的间距,enclosure 用于定义通孔边界与上(above)下(below)方相邻金属层边界的最小间距。

Layer(Masterslice or Overlap)

在设计中定义 MasterSlice(非布线)或 overlap layers。 Masterslice layers 通常是多晶硅层,只有在宏单元在多晶硅层上有 pins 时才会定义。

LAYER layerName

TYPE {MASTERSLICE | OVERLAP} ;

[MASK maskNum ;]

[PROPERTY propName propVal ;] ...

[PROPERTY LEF58_TYPE

"TYPE [NWELL | PWELL | ABOVEDIEEDGE | BELOWDIEEDGE | DIFFUSION | TRIMPOLY | TRIMMETAL | REGION]

];" ;

[PROPERTY LEF58_TRIMMEDMETAL

"TRIMMEDMETAL metalLayer [MASK maskNum]

]; " ;

END layerName

浙公网安备 33010602011771号

浙公网安备 33010602011771号