EDA 学习笔记之相关概念一: EM效应、via pillar/ladder、NDR

@

新手,有些资料中的英文翻译不太清楚准确通用的中文表示,保持原文

EM (electro-migration effect)

EM 是指金属导线中的电子在大电流的作用下,产生的电子迁移现象;随着电子的迁移,金属线可能会出现中间断裂断路,两端变粗和其他金属线接触短路,导致芯片失效的情况。

断路和短路原因:

当电子流过金属线时,将同金属线的原子发生碰撞,碰撞导致金属的电阻增大,并且会发热。在一定时间内如果有大量的电子同金属原子发生碰撞,金属原子就会沿着电子的方向进行流动。

这将会导致两个问题:第一,移动后的原子将在金属上留下一个空位,如果大量的原子被移动,则连线断开;第二,被移动的原子必须停在某一个地方,在电流方向的末端形成大量堆积。以铜导线为例,电流的趋肤效应导致电子都是在铜导线表面移动。

当发生碰撞后,表面的原子不断被撞击的向导线末端移动。原子离开的地方铜线不断变细甚至断开,原子堆积的地方铜线不断变粗甚至有可能和周围铜线接触导致短路。

影响材料电迁移效应的原因很多:导线长度,导线半径,电流大小,温度以及电流持续时间等。因此比较 EM 效应,必须要在相同各种条件下进行。

促进电迁移效应的情况有:

- 导线长度越长,原子数量越多

- 导线半径越小,电子分布区域越小,电子越集中

- 电流密度越大,电子数量越多

- 温度越高,电子能量越大,原子越活跃

- 电流持续时间越长,碰撞发生次数越多

修复 EM Violation

- 加宽金属线:使用 NDR 或者 打 patch 加宽金属线,提高载流能力

- 插入 Buffer,使用 buffer 打断长线的产生,降低金属线的电阻

- 降低 Cell 的驱动,减少大电流的产生

- 减少 fanout,减少大电流的产生

- 使用高层金属走线:高层金属具有更小的电阻和更强的载流能力

via pillar/ladder

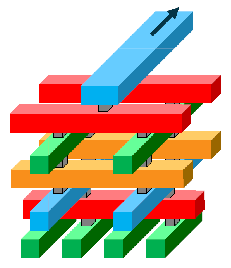

Pillar,柱子,ladder,梯子。via pillar/ladder 指的是一种特殊布线结构:当需要把金属从低层连到高层时,比如从 M1 到 M5,每一层都多添加一些 shape,这些 shape 与上下层通过 VIA 相连,最终连到 M5 再合并为一个 shape 出来,中间的 M2 到 M4 就像一个个井字或者田字,类似抽木块游戏。

例子:比如 clock cell 在 M1 有一个 pin,希望能在 M5 层绕线。传统的方法就是直接一摞 via 直接叠上去,电流路线只有一个。用了 via pillar/ladder,可以在 pin 上打三个 via,然后 M2 接 3 个 shape;然后 M2 上每个 shape 打 2 个 via,M3 接 2 个 shape,每个 shape 都接到 M2 的 3 个 shape 上。这 2 个还是 3 个还是更多都是可以指定的。如此一来,每层金属不再是单一的一个 via,而是相当于增加了多个 shape,有多条电流通路。

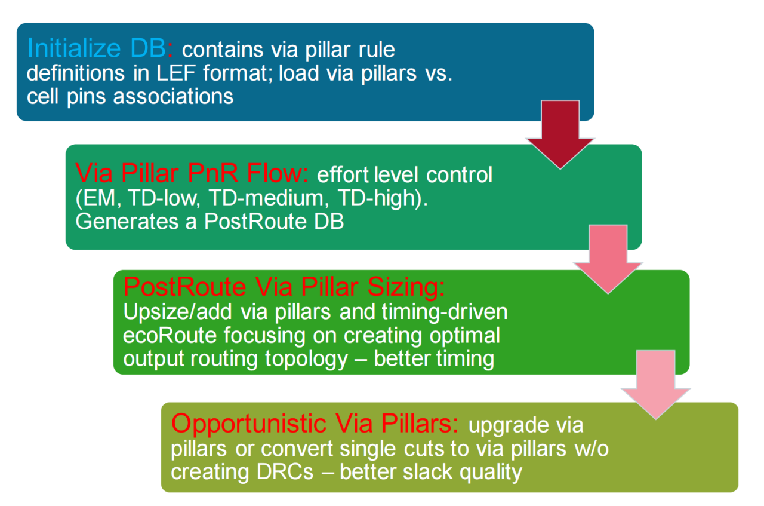

via pillar 在实际的使用流程为

这种结构设计有很多优点:

- 可以减小电路的电阻,分担电流,有效改善 EM 效应的问题;

- connecting to multiple fingers of a pin

- replacing multi-cut via at DPT layers

- improving tinming performance

- adding to the robustness of slack

- improving utilization

但是 via pillar 也有一个致命缺点————占用绕线资源。

NDR

先进工艺节点下数字设计需要考虑复杂物理效应和多样化需求,因此在芯片制作中会设置一些必须满足的设计规则,如最小间距、宽度要求等。

而 NDR(Non-Default Rule)主要是芯片物理设计阶段对特定信号线(如时钟、关键路径等)设置的绕线规则,与默认规则(Default Rule)相比,通过调整线宽、间距、金属层等参数优化信号性能。其核心作用包括:

- 改善时序性能:通过增大线宽降低电阻(RC值),减少信号延迟;增大间距减少串扰(Crosstalk)。

- 增强可靠性:通过屏蔽线(Shielding)隔离敏感信号,降低电磁干扰(EMI)和电压降(IR Drop)风险。

- 资源优先级分配:为高优先级信号(如时钟)分配高层金属资源,利用高层更优的电气特性(如更宽线宽、更低电阻)

NDR的主要应用场景

- 时钟树综合(CTS)

时钟线优化:时钟信号因翻转频率高、驱动负载大,常需设置 2W2S(双倍线宽与间距)或更高规格的 NDR。

分层策略:

- Trunk 线(主干):优先使用高层金属,避免低层金属的寄生效应。

- Leaf 线(末端):采用接近默认规则的 NDR,平衡性能和资源占用。

屏蔽设计:为高频时钟添加并行地线(Shielding Net),消除相邻信号干扰。

- 关键信号线处理

高速总线/模拟信号:设置 NDR 以减少串扰和噪声,例如模拟IP的连线需额外屏蔽和宽间距。

ECO 阶段修复:对时序违例或 EM 问题严重的信号线局部应用 NDR,避免全局规则调整带来的资源冲突。

- 特殊需求场景

车规芯片安全设计:通过 NDR 增强冗余路径的隔离性,满足ASIL-D等级的抗干扰要求(如锁步核间的独立绕线)

资源权衡策略

- 金属层优先级:

时钟线优先使用高层金属,但需避免低层金属的引脚访问冲突。 - 绕线资源限制:

工具可能因拥塞无法完全遵循 NDR,需设置达标率阈值(如 90% 以上满足)

NDR的优缺点

- 优势

性能显著提升:时钟线延迟可降低 10%-30%,串扰噪声减少 50% 以上。

灵活性高:支持按信号类型分层定制,适应不同场景需求。 - 劣势

绕线资源消耗:NDR 可能占用额外 30%-50% 的布线资源,加剧局部拥塞。

时序一致性风险:非整数倍线宽(如 1.5 倍 Pitch)可能导致预估时序与实际绕线结果偏差

Timing

时序驱动(Timing-Driven)功能的核心目标是确保芯片的物理设计满足所有时序要求(如时钟频率、建立时间/保持时间等),同时优化面积、功耗和可靠性,在布局布线阶段如何进行时序优化是确保芯片性能的难点。

浙公网安备 33010602011771号

浙公网安备 33010602011771号