[CMU 15-418] (Lecture1) Why Parallelism

本系列文章为 CMU 15-418/15-618: Parallel Computer Architecture and Programming, Fall 2018 课程学习笔记

课程官网:CMU 15-418/15-618: Parallel Computer Architecture and Programming

参考文章:CMU 15-418 notes

相关资源与介绍:CMU 15-418/Stanford CS149: Parallel Computing - CS自学指南

Challenges of parallelizing code, motivations for parallel chips, processor basics

Theme 1

Theme 2

Theme 3

Summary

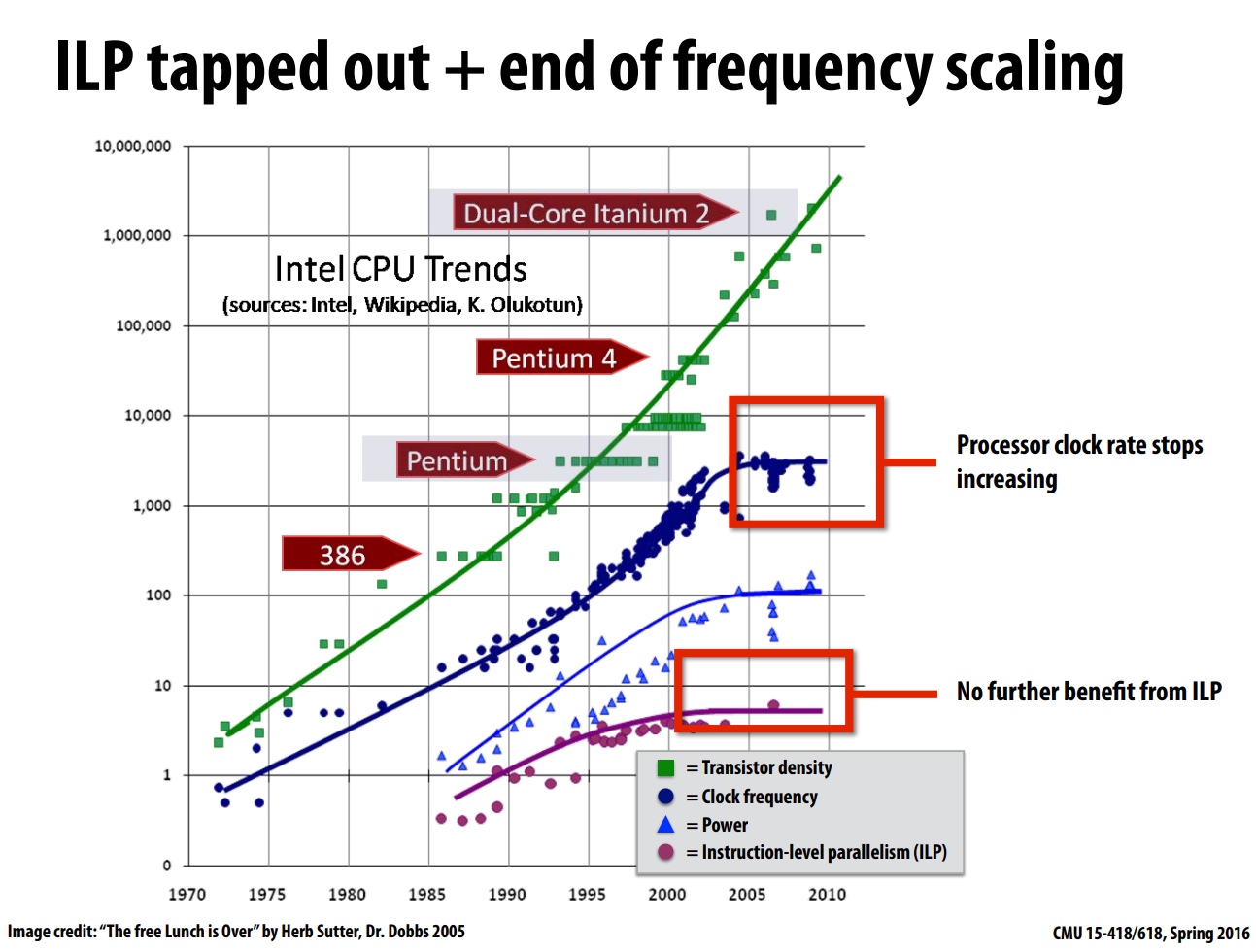

ILP(instruction level parallelism) 指令级并行不能一直增长,因为一个程序中出现若干不相关指令的数量有一定阈值(3~5)条。

由于功耗墙(power wall)的概念,提高主频的同时也会提高功耗,这时散热就成为了一个主要问题。所以,需要关注的是cores的效率(per area/per Watt),而不再是总性能。

所以,需要知道如何编写并行代码

并行代码需要考虑并行的划分,各并行之间的通讯与同步

并行系统的硬件构架知识是重要的

浙公网安备 33010602011771号

浙公网安备 33010602011771号