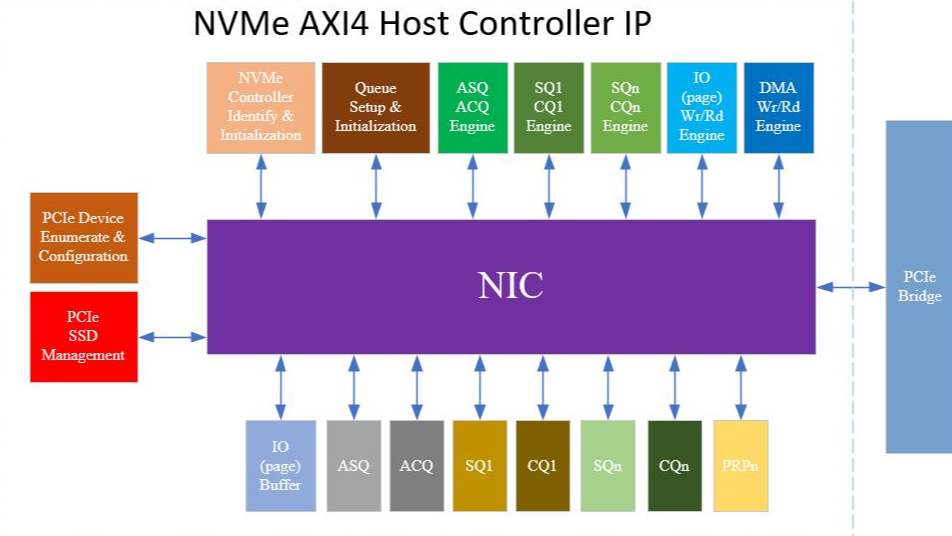

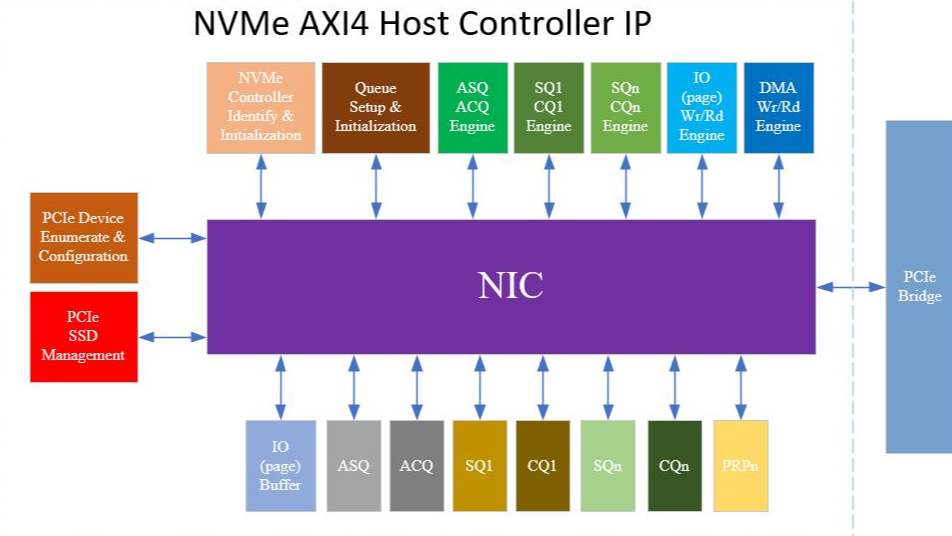

摘要:  NVMe AXI4 Host Controller IP可以连接高速存储PCIe SSD,无需CPU,自动加速处理所有的NVMe协议命令,具备独立的数据写入和读取AXI4接口,不但适用高性能、顺序访问的应用,也适用于随机访问的应用,同时结合外部存储器(比如DDR),使得Host端的数据访问管理更加灵活。 阅读全文

NVMe AXI4 Host Controller IP可以连接高速存储PCIe SSD,无需CPU,自动加速处理所有的NVMe协议命令,具备独立的数据写入和读取AXI4接口,不但适用高性能、顺序访问的应用,也适用于随机访问的应用,同时结合外部存储器(比如DDR),使得Host端的数据访问管理更加灵活。 阅读全文

NVMe AXI4 Host Controller IP可以连接高速存储PCIe SSD,无需CPU,自动加速处理所有的NVMe协议命令,具备独立的数据写入和读取AXI4接口,不但适用高性能、顺序访问的应用,也适用于随机访问的应用,同时结合外部存储器(比如DDR),使得Host端的数据访问管理更加灵活。 阅读全文

NVMe AXI4 Host Controller IP可以连接高速存储PCIe SSD,无需CPU,自动加速处理所有的NVMe协议命令,具备独立的数据写入和读取AXI4接口,不但适用高性能、顺序访问的应用,也适用于随机访问的应用,同时结合外部存储器(比如DDR),使得Host端的数据访问管理更加灵活。 阅读全文

posted @ 2024-07-17 23:25

adrifter

阅读(200)

评论(1)

推荐(0)

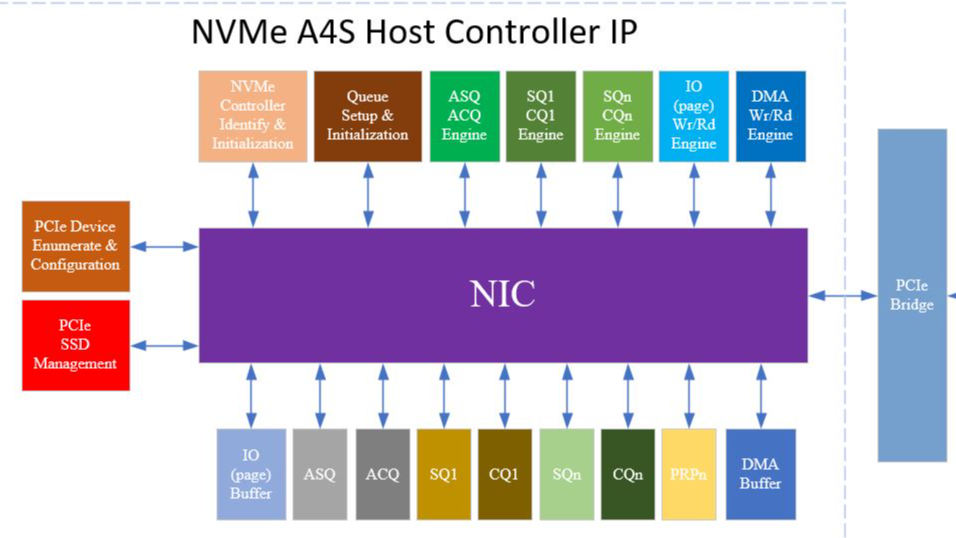

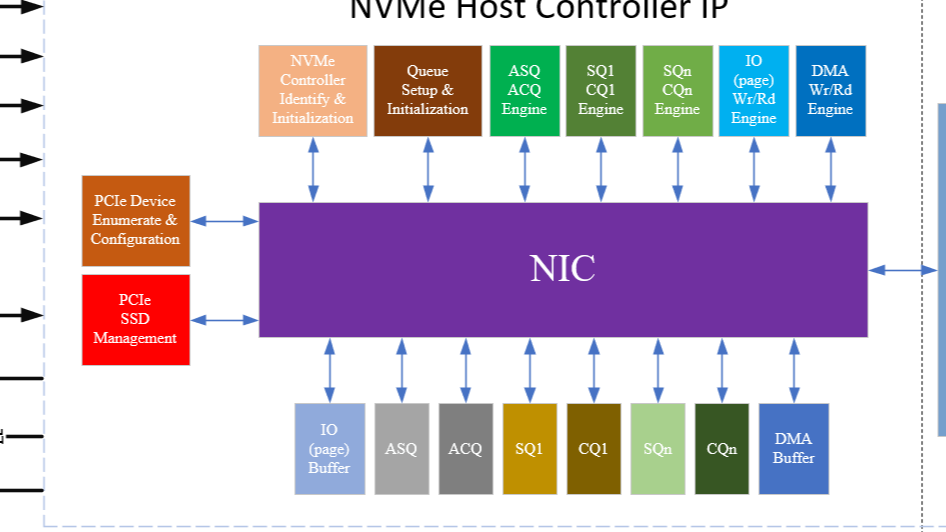

NVMe A4S Host Controller IP 1 介绍 NVMe A4S Host Controller IP可以连接高速存储PCIe SSD,无需CPU和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/FIFO接口和数据读取AXI4-Stream

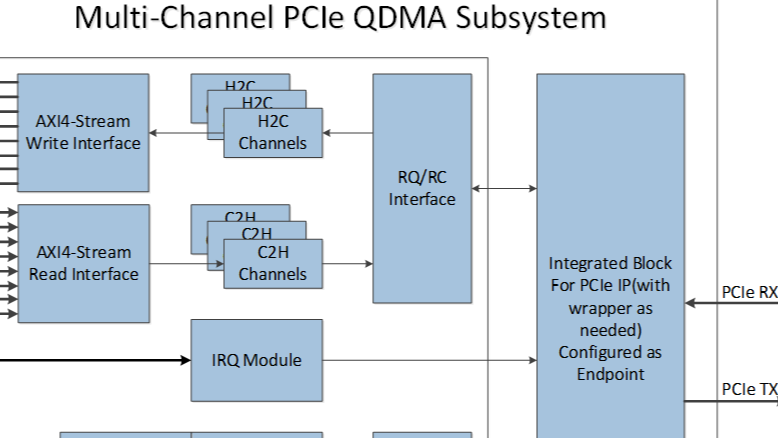

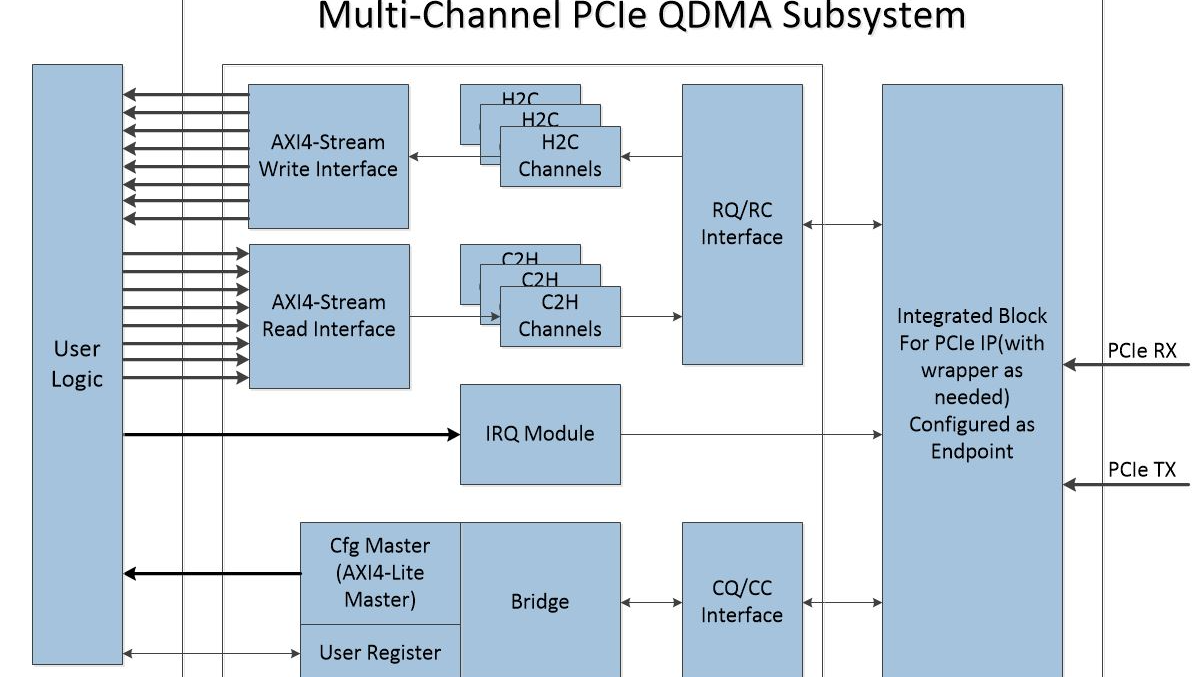

NVMe A4S Host Controller IP 1 介绍 NVMe A4S Host Controller IP可以连接高速存储PCIe SSD,无需CPU和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/FIFO接口和数据读取AXI4-Stream  Multi-Channel PCIe QDMA&RDMA IP 1 介绍 基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了使用DMA地址队列的独立多通道、高性能Continous或Scather Gather DM

Multi-Channel PCIe QDMA&RDMA IP 1 介绍 基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了使用DMA地址队列的独立多通道、高性能Continous或Scather Gather DM  NVMe Host Controller IP可以连接高速存储PCIe SSD,无需CPU和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/FIFO接口和数据读取AXI4-Stream/FIFO接口,非常适合于超高容量和超高性能的应用。此外,NVMe Host Controller IP支持RAID存储,从而可实现更高存储性能和存储容量。

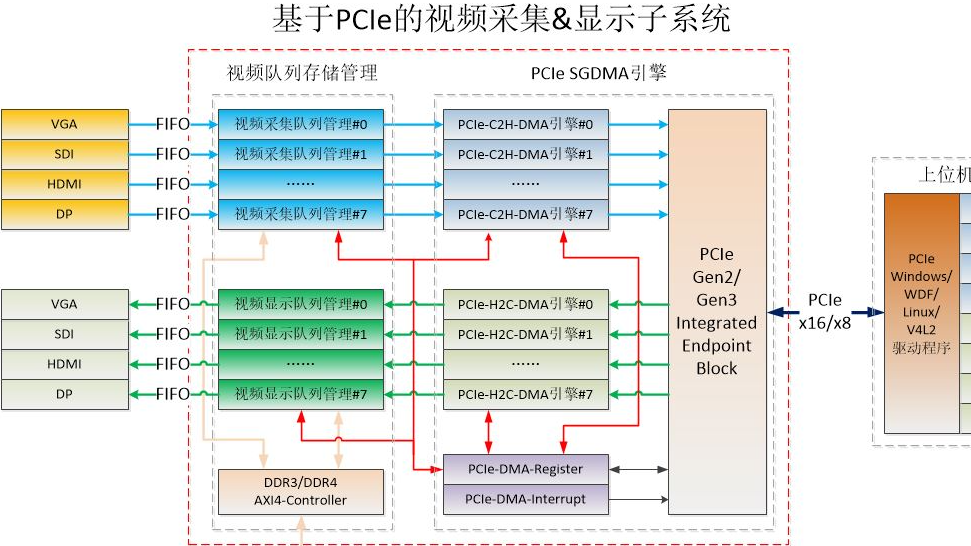

NVMe Host Controller IP可以连接高速存储PCIe SSD,无需CPU和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/FIFO接口和数据读取AXI4-Stream/FIFO接口,非常适合于超高容量和超高性能的应用。此外,NVMe Host Controller IP支持RAID存储,从而可实现更高存储性能和存储容量。  基于PCIe的多路视频采集与显示子系统 1 概述 视频采集与显示子系统可以实时采集多路视频信号,并存储到视频采集队列中,借助高效的硬实时视频帧出入队列管理和PCIe C2H DMA引擎,将采集到的视频帧实时传递到上位机采集缓冲区。 视频采集与显示子系统使用高效的PCIe H2C DMA引擎读取上位机

基于PCIe的多路视频采集与显示子系统 1 概述 视频采集与显示子系统可以实时采集多路视频信号,并存储到视频采集队列中,借助高效的硬实时视频帧出入队列管理和PCIe C2H DMA引擎,将采集到的视频帧实时传递到上位机采集缓冲区。 视频采集与显示子系统使用高效的PCIe H2C DMA引擎读取上位机  基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了基于DMA地址队列的高性能Continous或Scather Gather DMA,提供FIFO/AXI4-Stream用户接口。

基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了基于DMA地址队列的高性能Continous或Scather Gather DMA,提供FIFO/AXI4-Stream用户接口。  浙公网安备 33010602011771号

浙公网安备 33010602011771号