Verilog HDL与软件编程语言(如C语言)的区别?

Verilog HDL与软件编程语言的区别?【豆包】

Verilog HDL(硬件描述语言)与 C、Python、Java 等软件编程语言的核心区别,源于二者的设计目标差异 —— 前者用于描述硬件电路的结构与行为(最终生成物理电路),后者用于编写指令序列控制处理器执行任务(依赖现有硬件运行),这种目标差异进一步延伸到语法逻辑、执行方式、核心特性等多个维度。以下从 6 个关键维度展开对比,清晰呈现二者的本质不同:

1、设计目标:“造硬件” vs “用硬件” 这是二者最根本的区别,直接决定了后续所有差异的方向:

(1)Verilog HDL:目标是 “定义硬件”—— 通过代码描述电路的组成(如 “两个与门串联”)、信号的流向(如 “时钟上升沿时数据从 A 传到 B”),最终经综合工具(如 Quartus、Vivado)转化为 FPGA/ASIC 的物理电路(逻辑门、寄存器、布线等),本质是 “用代码生成硬件实体”。

(2)软件编程语言:目标是 “利用现有硬件”—— 基于已有的 CPU、内存等硬件,编写指令序列(如 “先计算 a+b,再判断结果是否大于 10”),最终经编译器 / 解释器转化为机器码,由 CPU 按顺序或并行(如多线程)执行,本质是 “用代码控制硬件完成任务”。

2、执行方式:“并行硬件行为” vs “串行 / 伪并行指令” 硬件与软件的运行逻辑截然不同,直接体现在代码的执行方式上:

(1)Verilog HDL:并行执行(模拟硬件特性) 硬件电路中,所有模块(如寄存器、逻辑门)是同时工作的(只要有输入信号,就会即时输出结果),因此 Verilog 代码的执行逻辑是 “并行的”—— 代码中不同的 “always 块”“assign 语句” 会同时响应各自的触发条件,不存在 “顺序执行” 的概念。 示例:一个包含 “按键检测模块” 和 “LED 驱动模块” 的 Verilog 代码,两个模块会同时监听各自的输入(按键信号、时钟信号),互不等待,完全模拟真实电路的并行工作状态。

(2)软件编程语言:串行为主(依赖 CPU 指令流) 软件的执行依赖 CPU 的 “取指 - 译码 - 执行” 流水线,默认是顺序执行(一条指令完成后再执行下一条);即使是 “多线程 / 多进程”,本质也是 CPU 通过 “时间分片” 实现的伪并行(快速切换不同任务,并非真正同时执行),核心仍受限于 CPU 的指令执行逻辑。 示例:一段 Python 代码 “print (1); print (2);” 会严格先输出 1、再输出 2;即使开启多线程,两个线程的指令也需争夺 CPU 时间片,无法像硬件那样 “无冲突同时运行”。

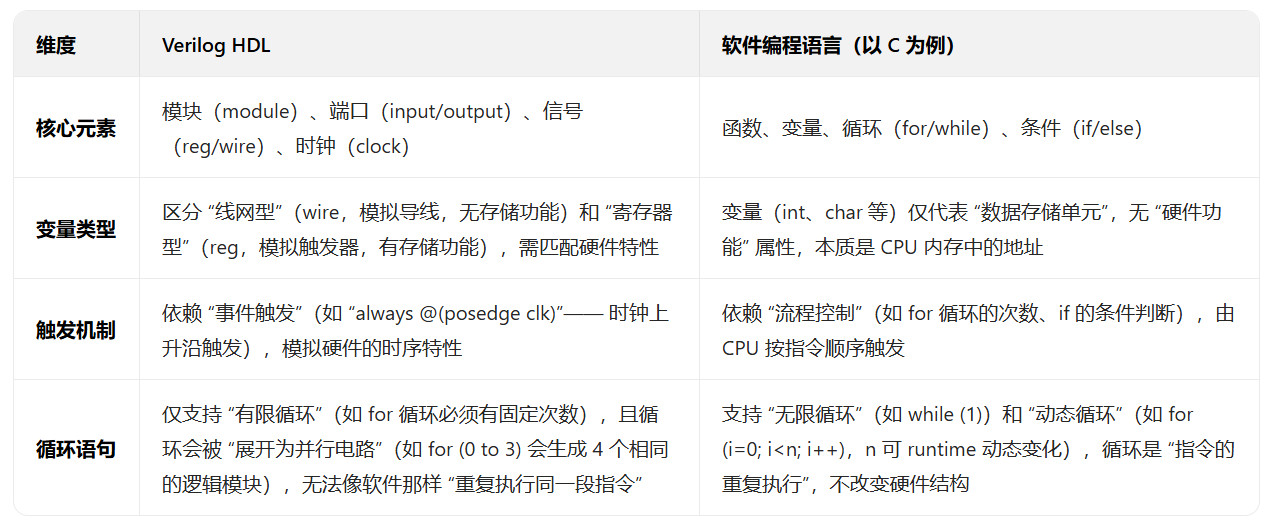

3、核心语法:“描述电路” vs “描述算法” 二者的语法设计围绕各自目标展开,逻辑模型完全不同

4、时间模型:“精确时序” vs “模糊时间” 硬件电路对 “时间”(时钟、延迟)的要求极高,而软件对时间的定义更偏向 “逻辑顺序”:

4、时间模型:“精确时序” vs “模糊时间” 硬件电路对 “时间”(时钟、延迟)的要求极高,而软件对时间的定义更偏向 “逻辑顺序”:

(1)Verilog HDL:精确时序建模 代码需明确描述电路的时序特性—— 如 “数据在时钟上升沿后 10ns 稳定”“信号经过与门有 2ns 延迟”,这些时序参数会直接影响最终电路的稳定性(如是否满足 “建立时间 / 保持时间”),是硬件设计中 “时序分析” 的核心依据。 即使是 “行为级 Verilog”(不关注具体延迟),也需通过 “时钟触发” 明确信号的更新时机,本质仍是对硬件时序的抽象。

(2)软件编程语言:模糊时间(依赖 CPU 速度) 软件中的 “时间” 是 “相对的”—— 如 “延迟 1 秒” 是通过 “让 CPU 执行空指令循环” 或调用系统时钟函数实现的,实际执行时间依赖 CPU 的主频(不同 CPU 执行同一段延迟代码,耗时可能不同),代码本身不定义 “硬件级的精确延迟”,仅关注 “逻辑上的时间间隔”。5、代码归宿:“综合为硬件” vs “编译为机器码” 二者的 “代码→可执行形式” 的转化过程完全不同,最终产物的形态也天差地别:

(1)Verilog HDL:综合→网表→物理电路,Verilog 代码的转化流程是: 行为级 / 结构级代码 → 综合工具(如 Synplify)转化为 “门级网表”(描述逻辑门、寄存器的连接关系) → 布局布线工具(如 Vivado)将网表映射到 FPGA/ASIC 的物理资源(如 LUT、FF) → 生成可下载到硬件的 “比特流文件”,最终产物是物理电路。 注意:并非所有 Verilog 代码都能 “综合”—— 如 “$display”(打印语句)仅用于仿真,无法转化为硬件,仅在 “仿真验证” 阶段使用。

(2)软件编程语言:编译 / 解释→机器码→CPU 执行; 软件代码的转化流程是: 高级语言代码 → 编译器(如 GCC)转化为 “汇编代码” → 进一步转化为 “机器码”(CPU 能识别的 0/1 指令) → 机器码加载到内存,由 CPU 按指令流执行,最终产物是可执行的指令序列,不改变硬件本身的结构。

6、核心思维:“硬件结构思维” vs “算法流程思维” 编写代码时的 “思考角度” 完全不同,是区分二者的关键:

(1)写 Verilog:先想 “电路长什么样” 编写前需先构建 “电路结构”—— 比如 “要实现一个计数器,需要 1 个寄存器存储计数值,1 个加法器实现加 1,1 个时钟触发寄存器更新”,再用代码描述这个结构(如 “always @(posedge clk) begin cnt <= cnt + 1; end”),本质是 “用代码画电路”。 若按软件思维写 Verilog(如用 “无限循环” 模拟计数),代码可能无法综合,或生成冗余、不稳定的电路。

(2)写软件:先想 “步骤怎么排” 编写前需先规划 “指令步骤”—— 比如 “要实现计数器,先定义变量 cnt=0,再用 while (1) 循环让 cnt++,每次循环延迟 1 秒”,本质是 “用代码规划 CPU 的执行步骤”,无需关心 CPU 内部的电路结构(如加法器如何实现)。

总结:一句话区分 用Verilog写代码:相当于 “用文字描述一栋房子的图纸(承重墙、水管、电线走向)”,最终能按图纸盖出真实的房子; 用软件语言写代码:相当于 “用文字描述如何使用这栋房子(先开门、再开灯、最后做饭)”,依赖已有的房子完成任务,不会改变房子的结构。这种本质差异,决定了二者在电子设计领域的分工:Verilog 用于 “前端硬件设计”,软件语言用于 “后端嵌入式控制”,二者常配合使用(如 FPGA 中,Verilog 实现硬件加速模块,C 语言编写 CPU 控制逻辑),但绝不能混淆其设计逻辑。

浙公网安备 33010602011771号

浙公网安备 33010602011771号