IO与中断

I/O系统概述

- I/O系统作用,一言以蔽之,就是协调高速cpu与低俗外设之间的信息交换

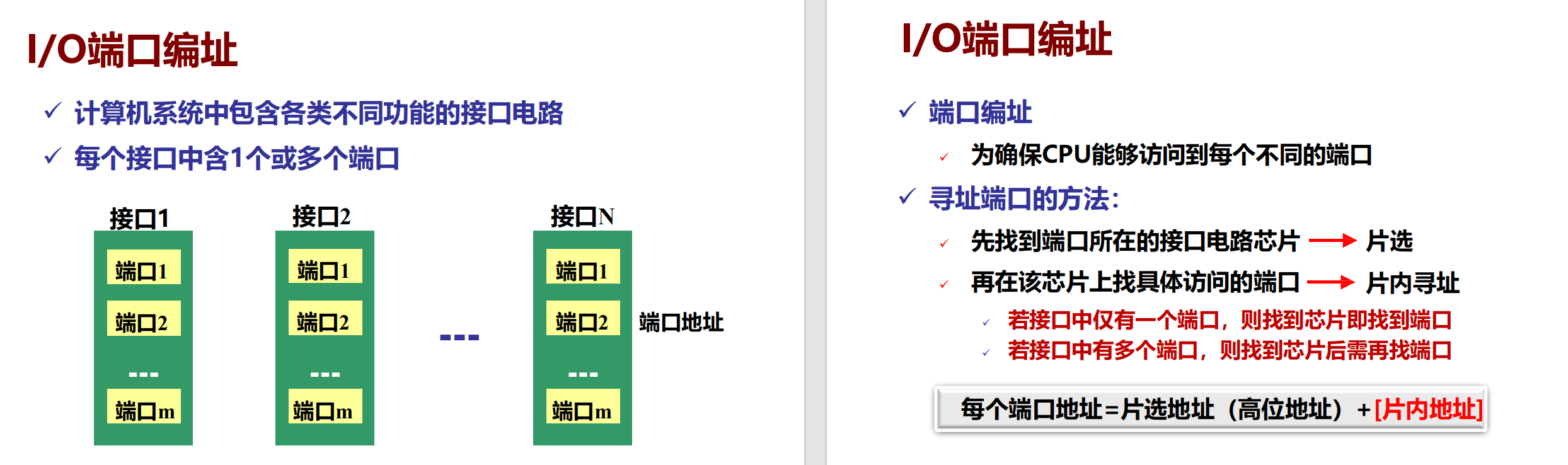

- 两种编址方式,与内存统一编址和独立编制,8086/8088采用独立编址,与内存共用地址总线,用IO/#M,信号状态区分,访问端口时仅使用地址总线的:A15~A0,可寻址的I/O端口数为64K(65536)个,I/O地址范围:

0~FFFFH - IBM PC只使用了1024个I/O地址(0~3FFH)

简单接口芯片

接口分类与特点

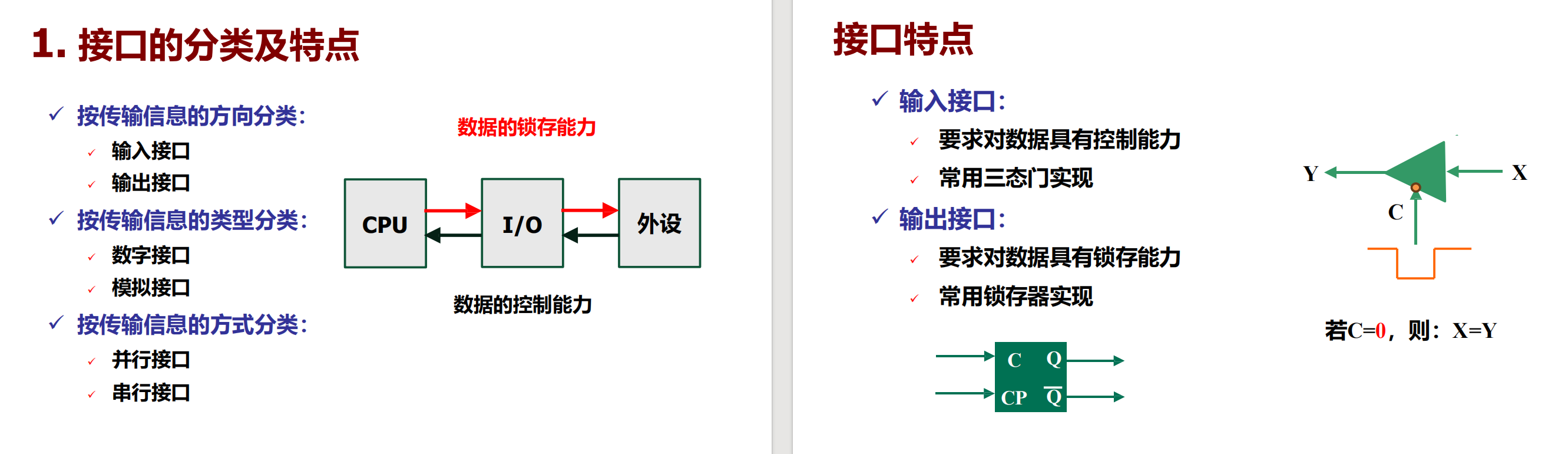

- CPU把数据存进IO,对应的是输出接口要有良好的数据锁存能力

- 外设把数据写进IO,对应的是输入接口要有对数据有控制能力,即:CPU指令一到,外设就要把数据立刻写入IO

输出输入都是看的出cpu还是入cpu

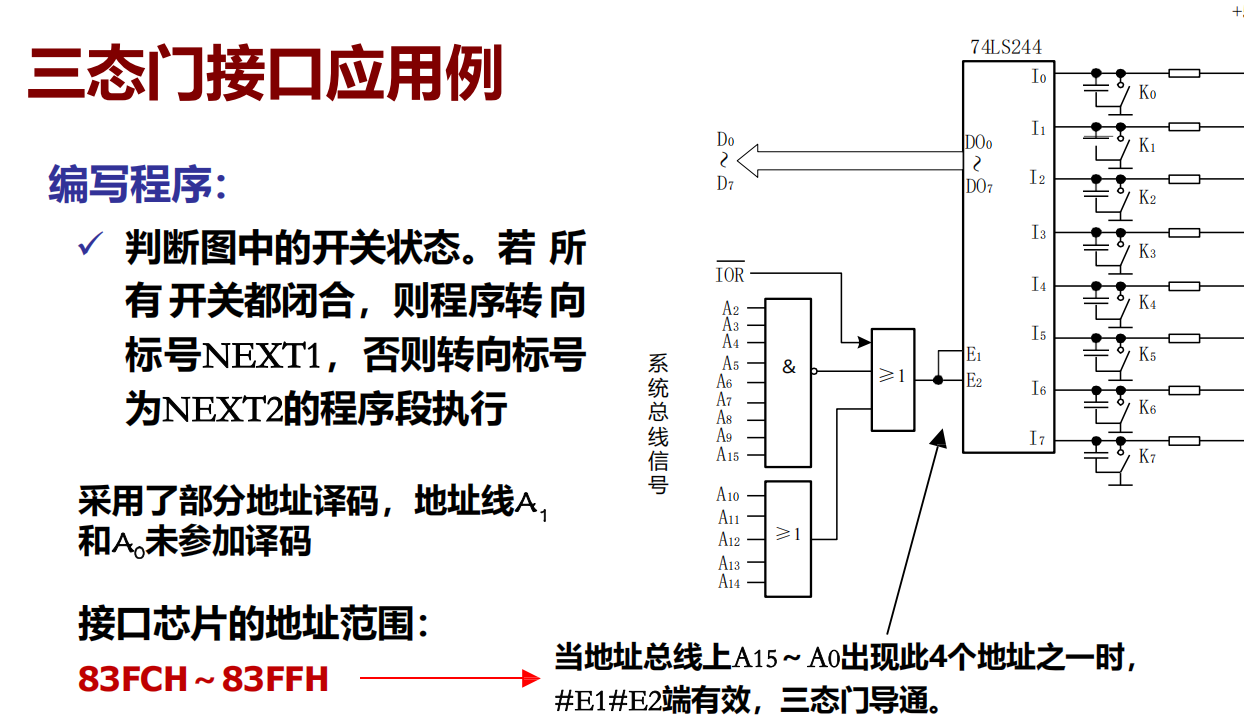

三态门接口:写入CPU:74LS244

在外设具有数据保持能力时用来输入接口,例如74LS244,它是含8个三态门的集成电路芯片

1都去与非,0都去或。A1,A0(BHE)未参与译码,因此可以推断出端口地址为83FCH-83FFH。

MOV DX,83FCH

IN AL,DX # DX对应的内容写入AL

AND AL,0FFH # 判断是否全闭合

JZ NEXT1 # 是,跳转NEXT1

JMP NEXT2 # 不是,跳转NEXT2

NEXT1:

NEXT2:

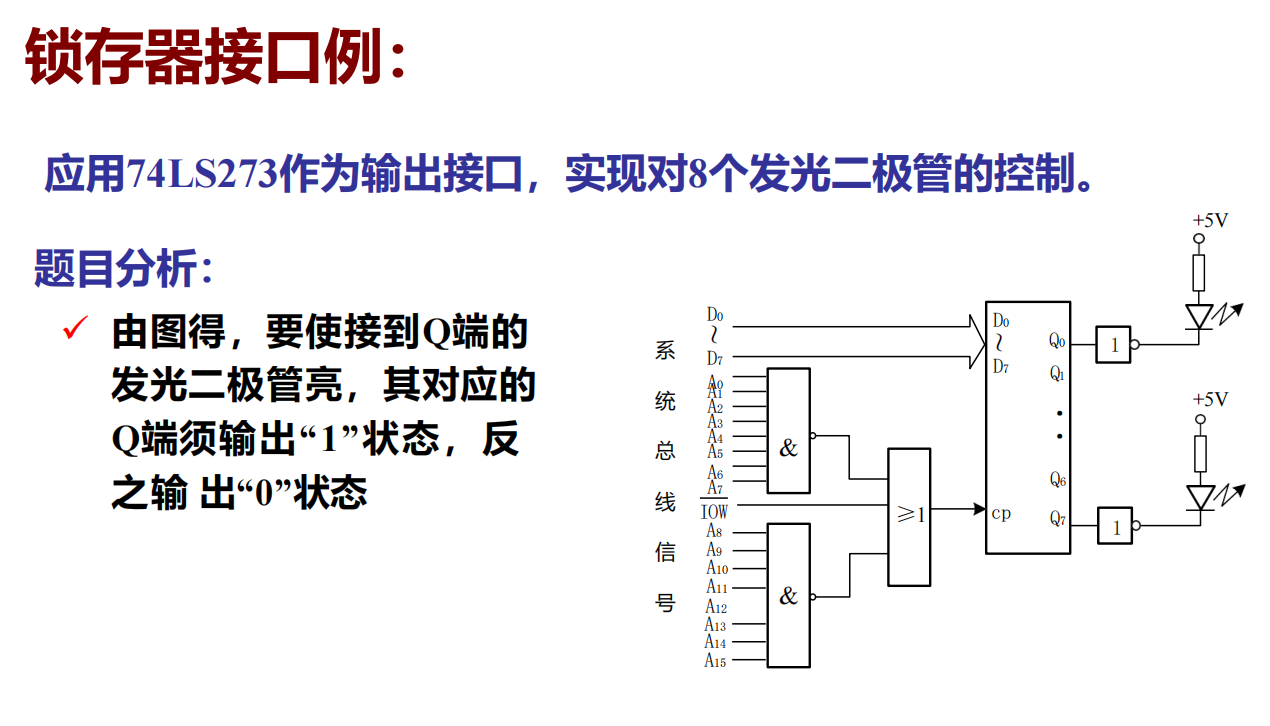

锁存器接口

- 74LS273只能锁存(cpu向外写)

- 74LS373既可以做输入接口,也可以做输出接口。

PPT给的例题较为简单:

74LS273地址显然为FFFFH

MOV DX 0FFFFH #当十六进制数以字母(A-F)开头时,必须在前面加前导零

MOV AL 10000001B

OUT DX, AL

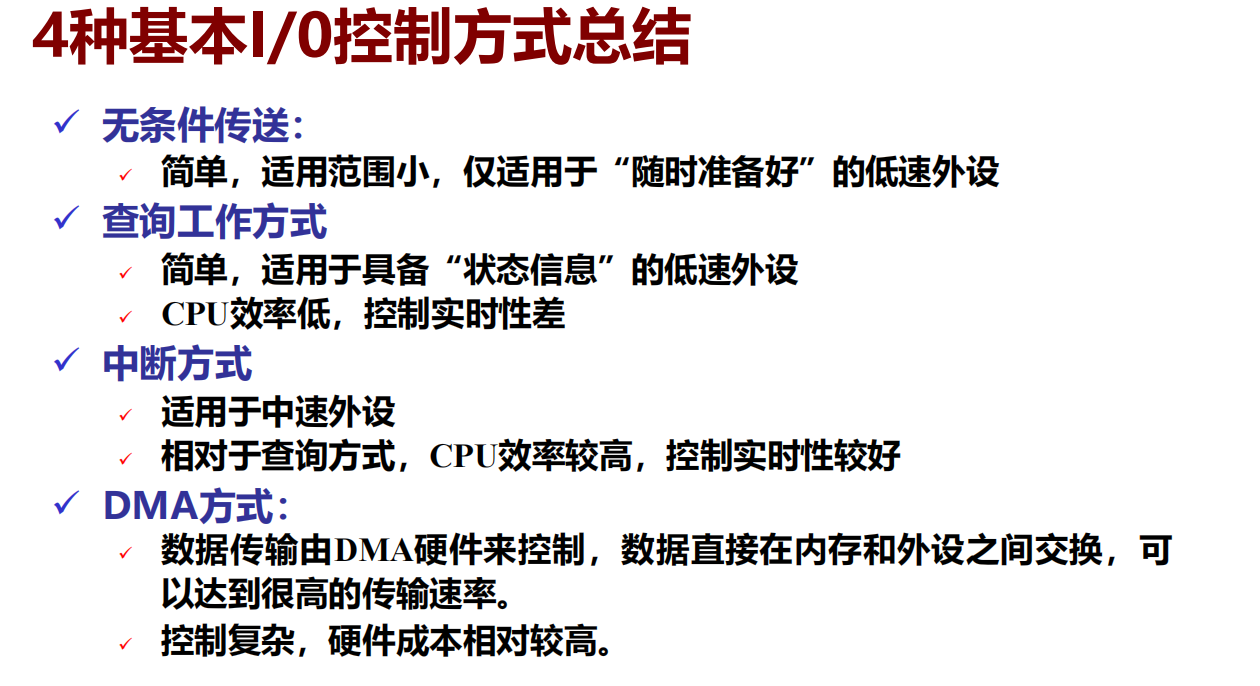

基本输入输出方法(简答)

- 无条件传送,例如LED灯

- 查询:仅当条件满足时才能进行数据传送,每满足一次条件只能进行一次数据传送

- 中断:外设在需要时向CPU提出请求,CPU再去为它服务。服务结束后或在外设不需要时,CPU可 执行自己的程序

上述三种信息的传送均需通过CPU

- DMA:外设直接与存储器进行数据交换 ,CPU不再担当数据传输的中介,总线由DMA控制器(DMAC)进行控制(CPU要放弃总线控制权),内存/外设的地址和读写控制信号均由DMAC提供

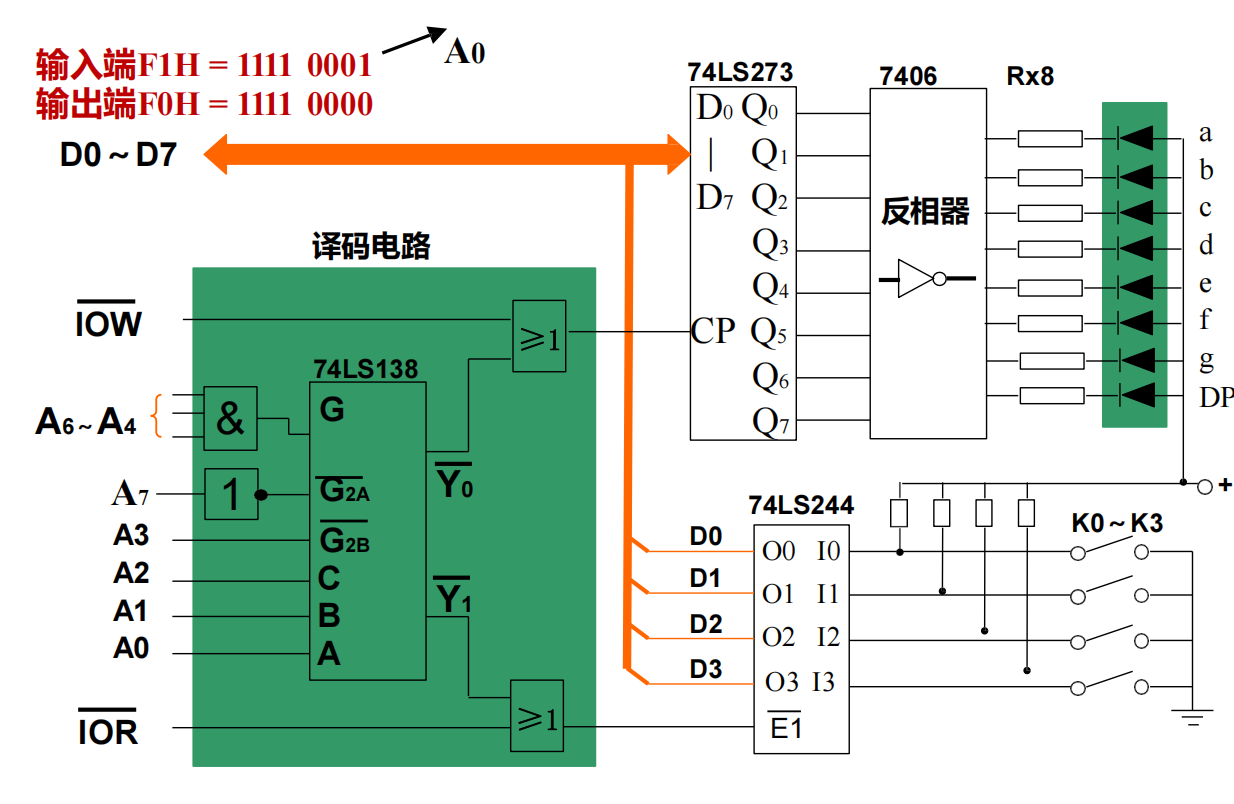

简单I/O接口电路设计示例(简答-画图)(不考)

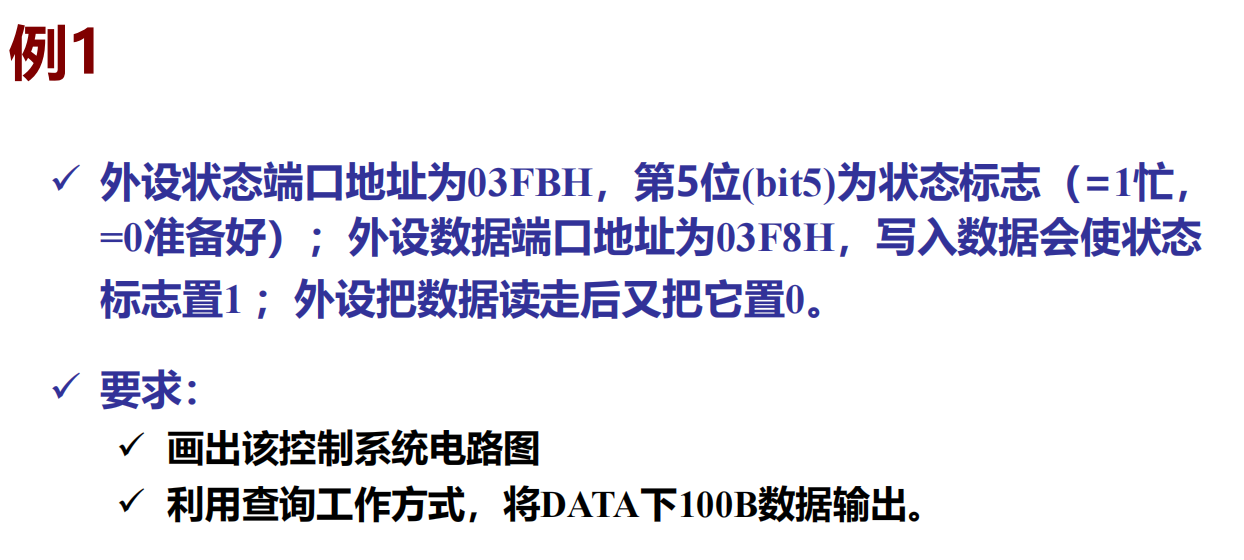

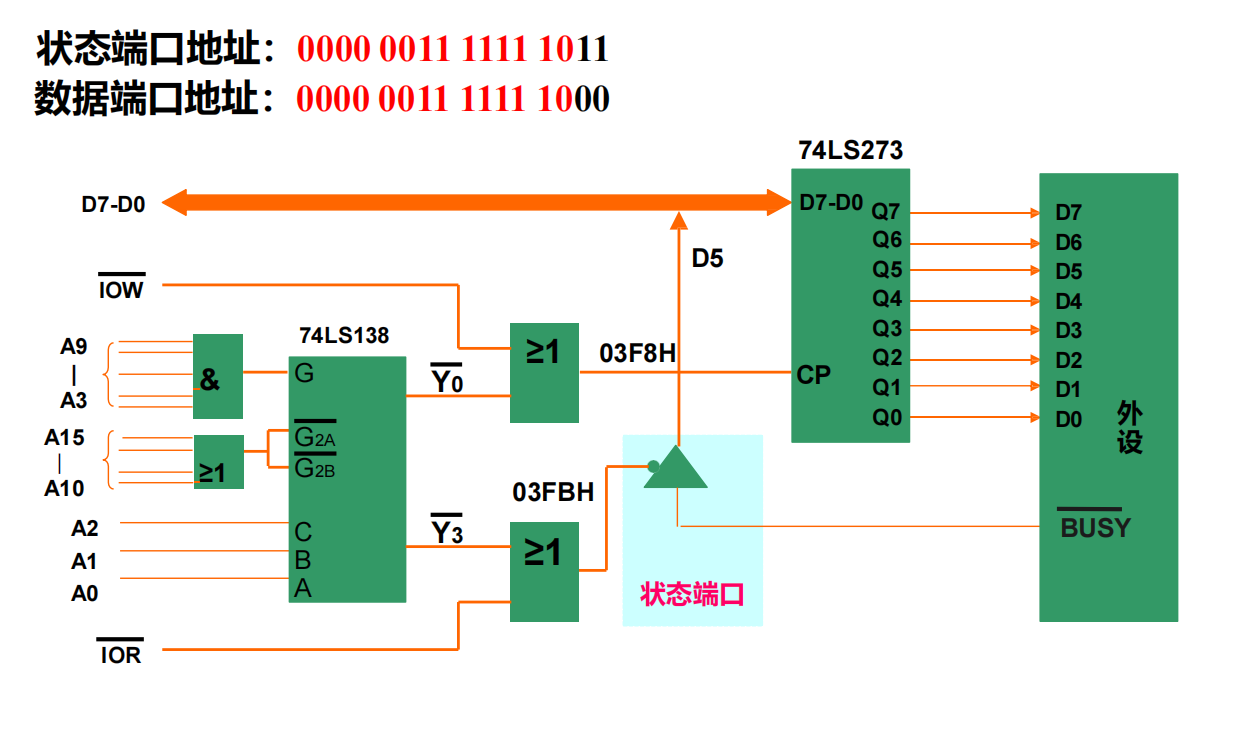

例题1

- 列出状态端口地址和数据端口地址,发现只有后两位不一样

- A系列以及#IOR译码给三态门控制用,准备将BUSY信号写入cpu

- A系列和#IOW译码给74LS273的CP用,控制数据锁存

- 74LS273的Q直连外设的D,74LS273的D直连cpu的D

- BUSY直连CPU的D

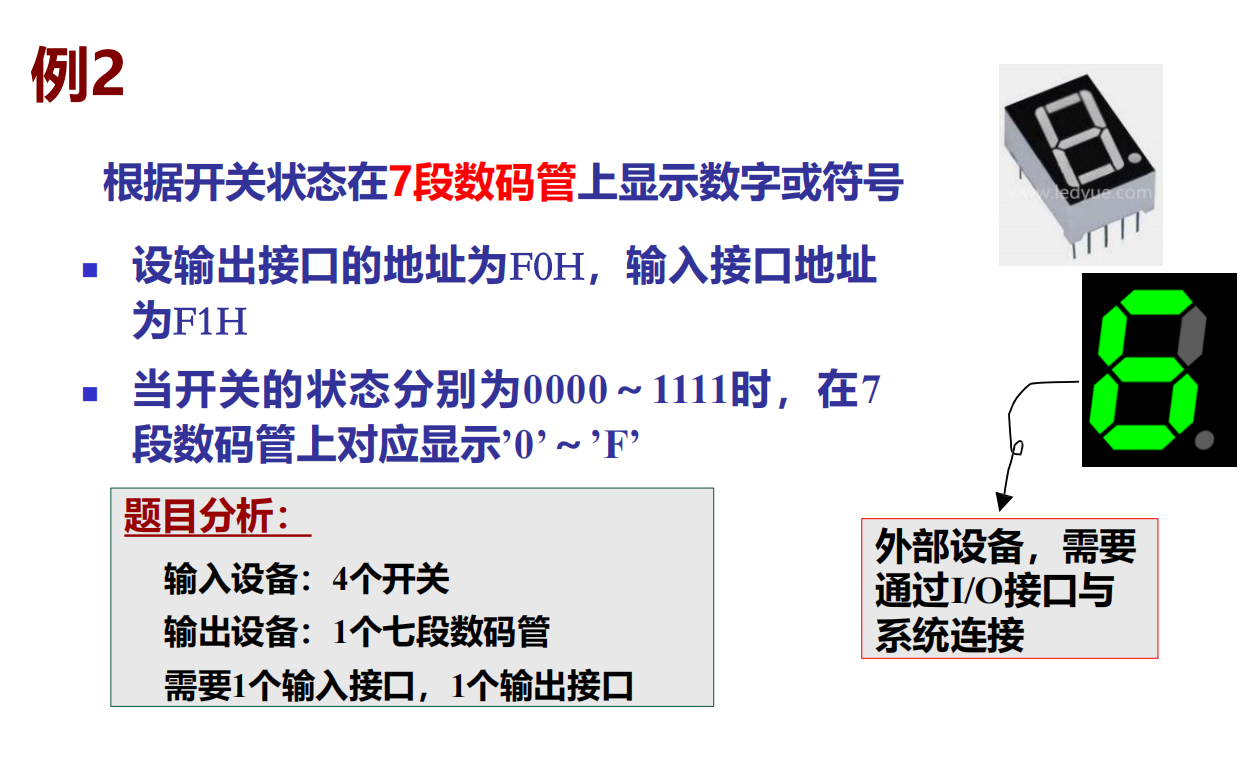

例题2

- 记住CP和#E1分别用于使能即可,译码得出的信号输出给使能端

中断技术(简答)(不考)

有关基本概念

- 为了提高cpu利用率引入中断

- CPU执行程序时,由于发生了某种随机的事件(外部或内部), 引起CPU暂时中断正在运行的程序,转去执行一段特殊的服务程序,以处理该事件,该事件处理完后又返回被中断的程序继续执行,这一过程称为中断。

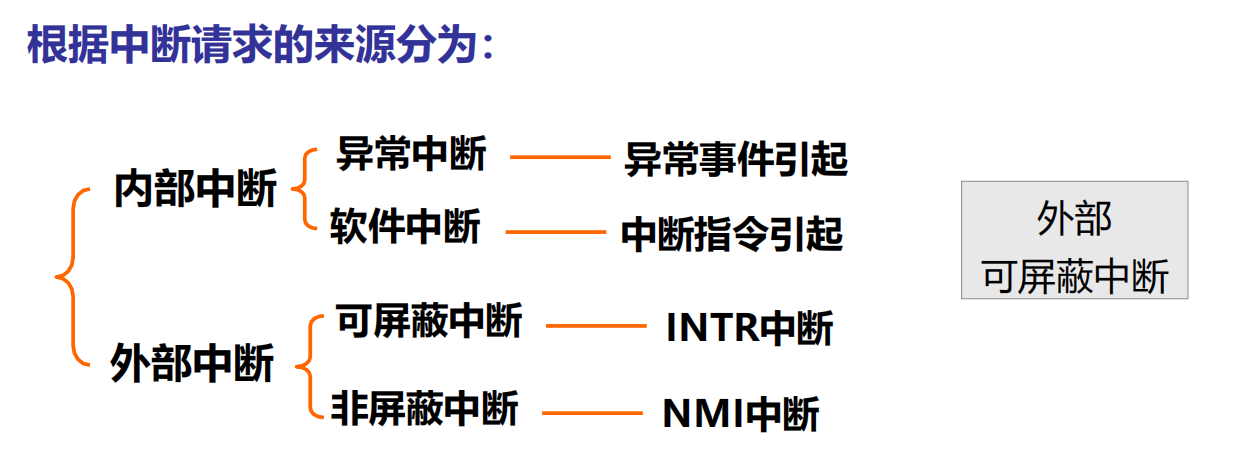

中断类型的分类

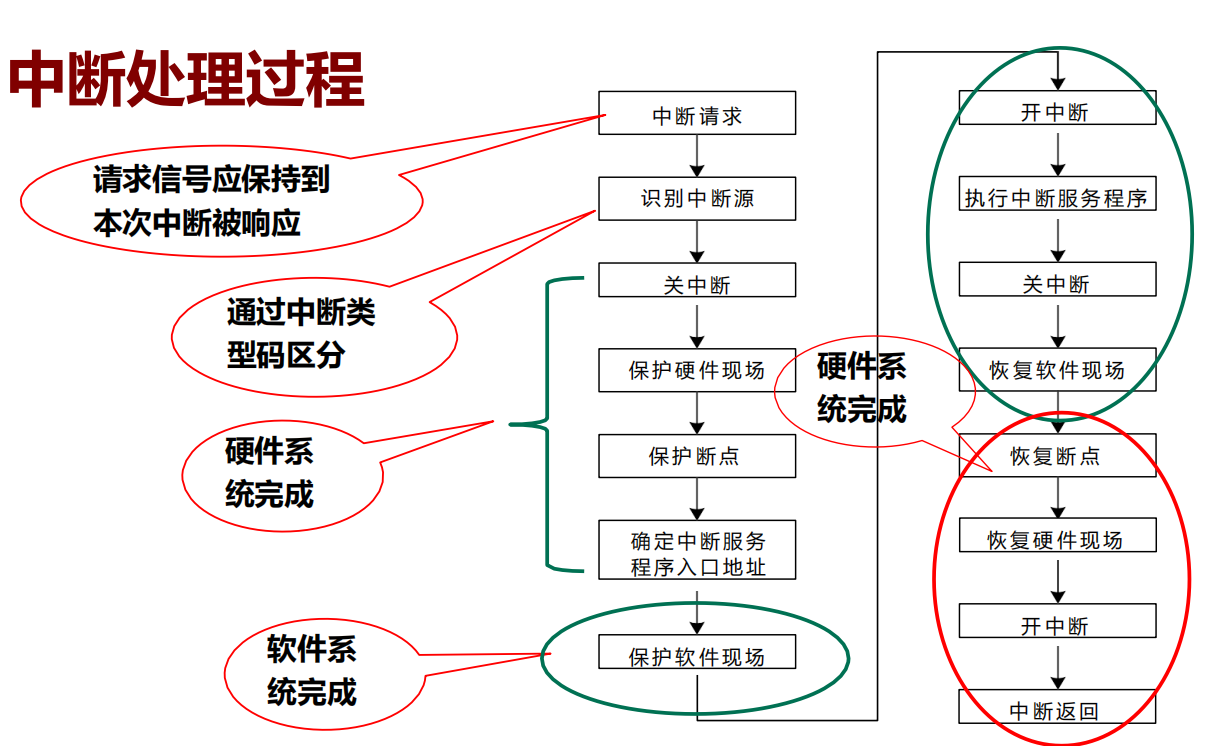

外部可屏蔽中断响应的一般过程(流程大致能答出来)

- 1.中断请求,外部可屏蔽中断请求信号是INTR,中断请求信号应保持到中断被处理为止

- 2.中断源识别(多个中断请求)+中断判优,根据中断向量码(中断类型码)确定中断源,根据程序优先级或者排队原则来确定先处理哪一个中断

- 3.中断响应,向中断源发出中断信号#INTA(告诉他我开始处理中断了!)然后保护现场

- 4.中断处理,根据中断向量执行中断程序

- 5.中断返回,执行IRET指令,使IP、CS和FLAGS从堆栈弹出

浙公网安备 33010602011771号

浙公网安备 33010602011771号