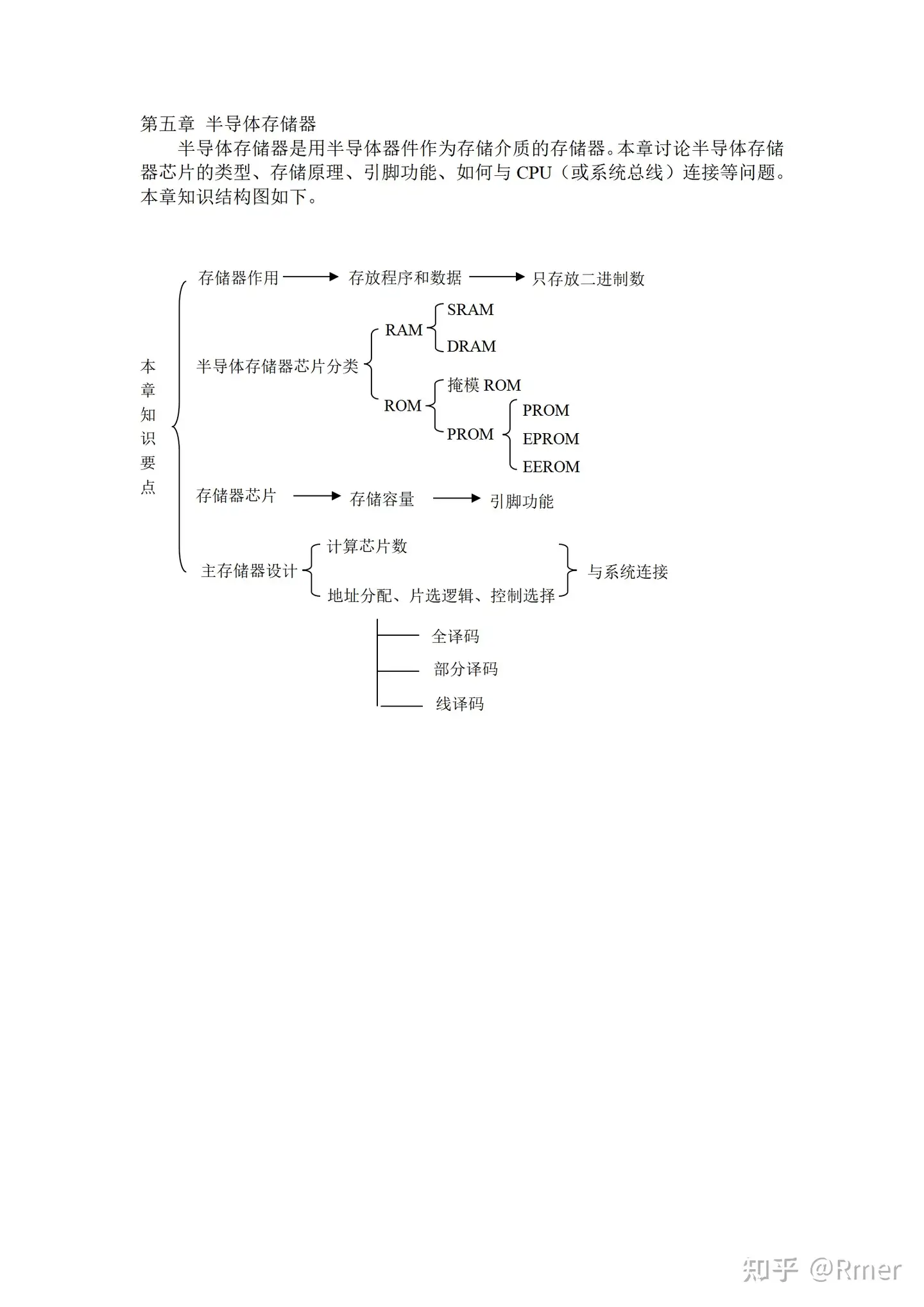

存储器

存储器概述

重点关注RAM,ROM分类各个类别特点即可

一些评价指标:

- 存储容量 存储单元个数×每单元的二进制数位数

- 存取时间 实现一次读/写所需要的时间

- 存取周期 连续启动两次独立的存储器操作所需间隔的最小时间

- 可靠性,功耗

存储单元编址

存储单元的编址是指为每个存储单元分配一个唯一的地址,以便CPU可以通过地址访问特定的存储单元。

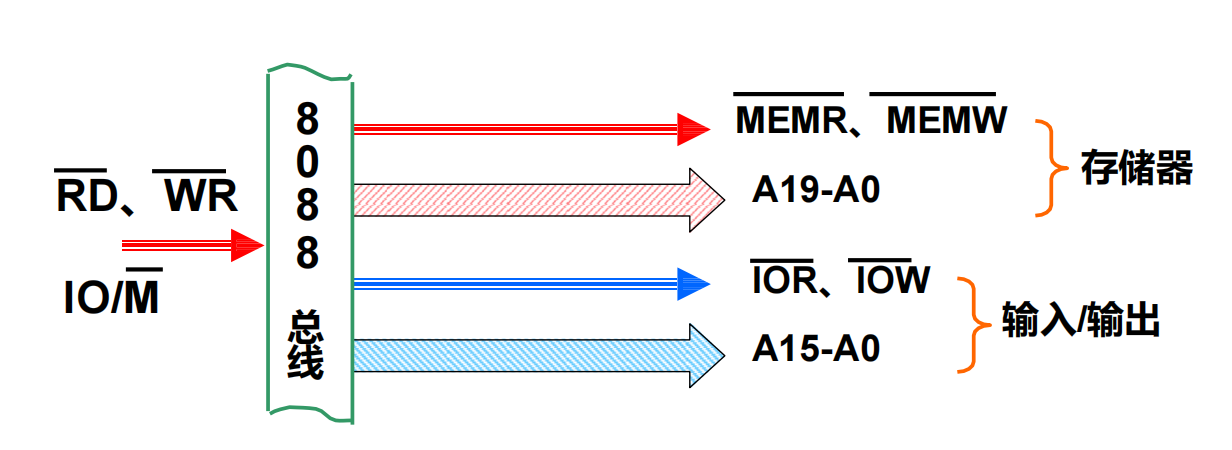

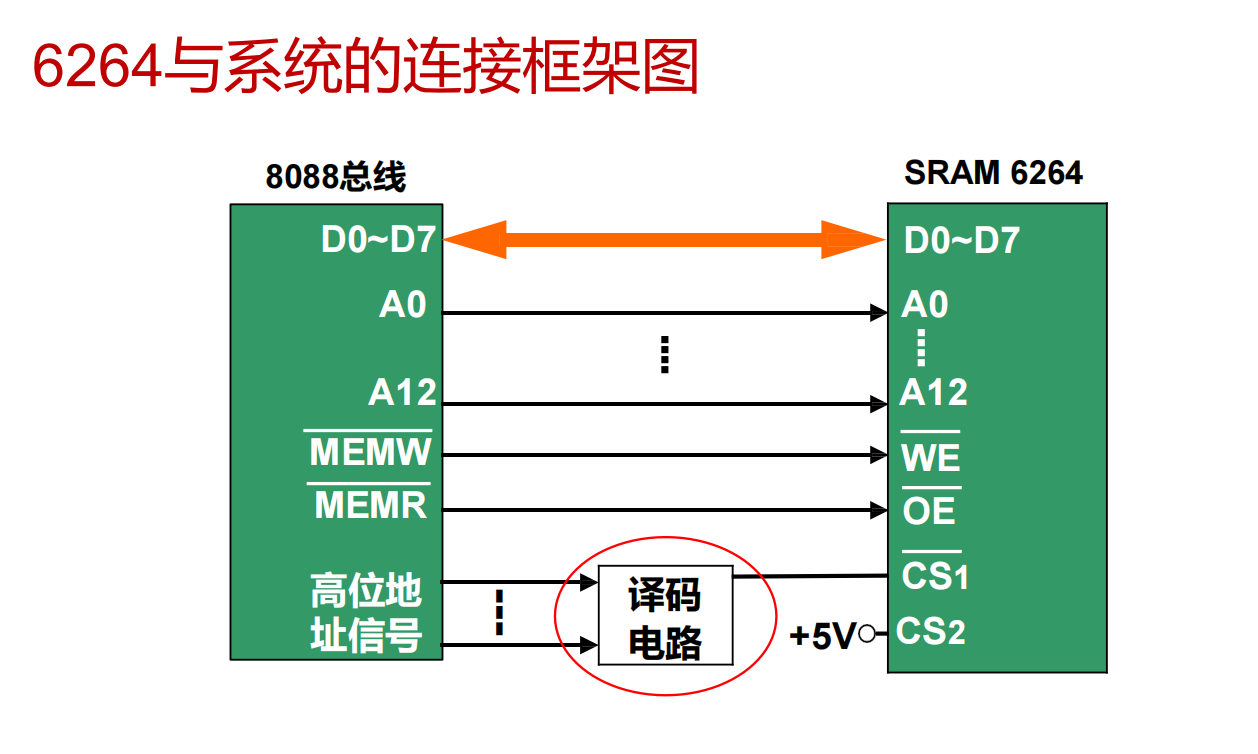

首先记忆8088的总线信号,这里会考画图题,务必记清楚

- \(\overline{RD}\)为8088读信号,一般连接芯片的\(\overline{OE}\)读使能

- \(\overline{WR}\)为8088写信号,一般连接芯片的\(\overline{WE}\)写使能

8088里面

MEMR = RD & ~IO_M; // 存储器读

MEMW = WR & ~IO_M; // 存储器写

所以做题一般都是直接用\(\overline{MEMR}\)和\(\overline{MEMW}\)来表示8088的读写信号。

关于存储器的编址,由两部分组成,其一是片选地址用来选择芯片,其二是片内地址用来选择芯片上的单元,做片内寻址用。片选信号由存储器上的$$\overline{CS}$$信号控制,接受一个译码电路产生的片选信号。

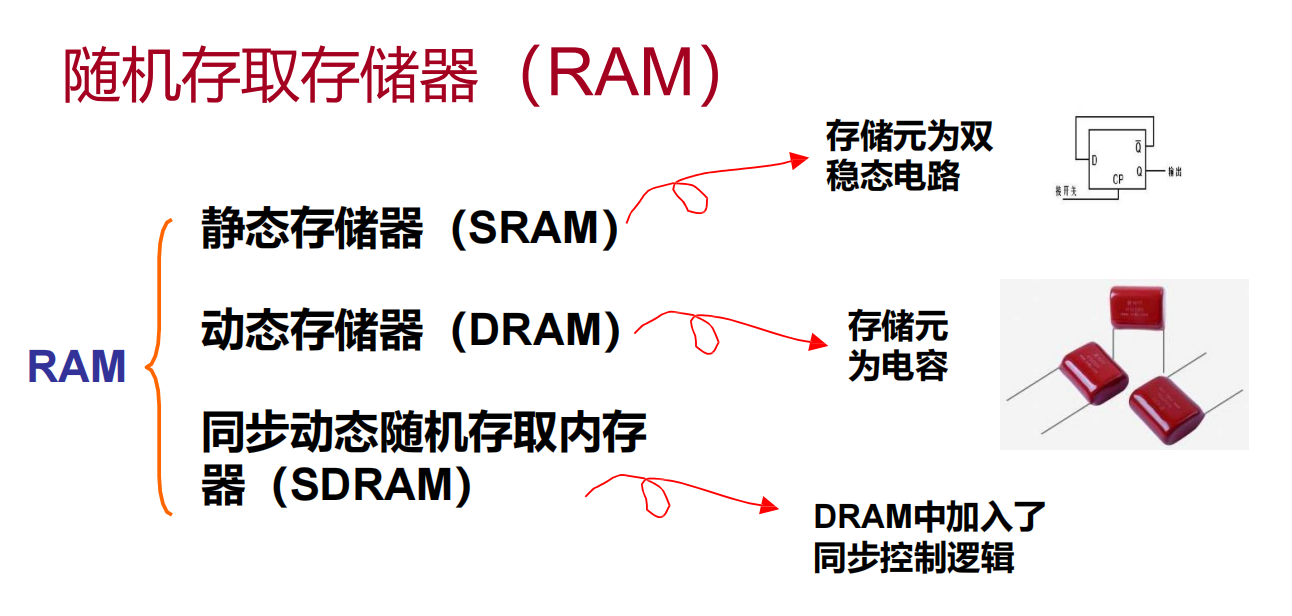

RAM(简答题)

RAM分为静态存储器SRAM(存储元为双稳态电路)和动态存储器DRAM(存储元为电容器)。DRAM需要定期刷新以保持数据,而SRAM不需要。

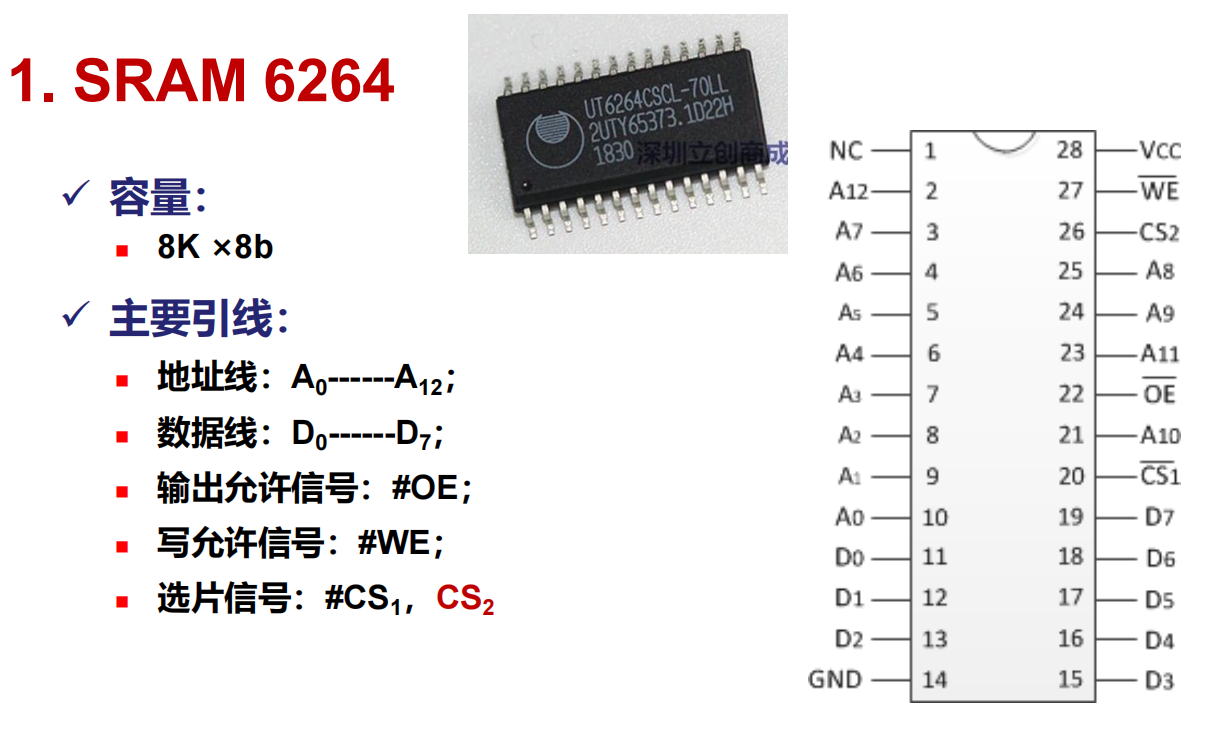

详细讲讲SRAM 6264 (64=88也就是8K8=8KB内存大小)

左边列出的引脚就是我们需要记忆的,主要包括:

- A0-A12: 地址引脚,用于选择存储单元(\(2^{13}=8K\))

- D0-D7: 数据引脚,用于数据的输入输出

- \(\overline{{CS}_{1}},{CS}_{2}\): 片选信号,一般1用于片选,2直接接+5V

- \(\overline{OE}\): 读使能信号,接8088的\(\overline{MEMR}\)信号

- \(\overline{WE}\): 写使能信号,接8088的\(\overline{MEMW}\)信号

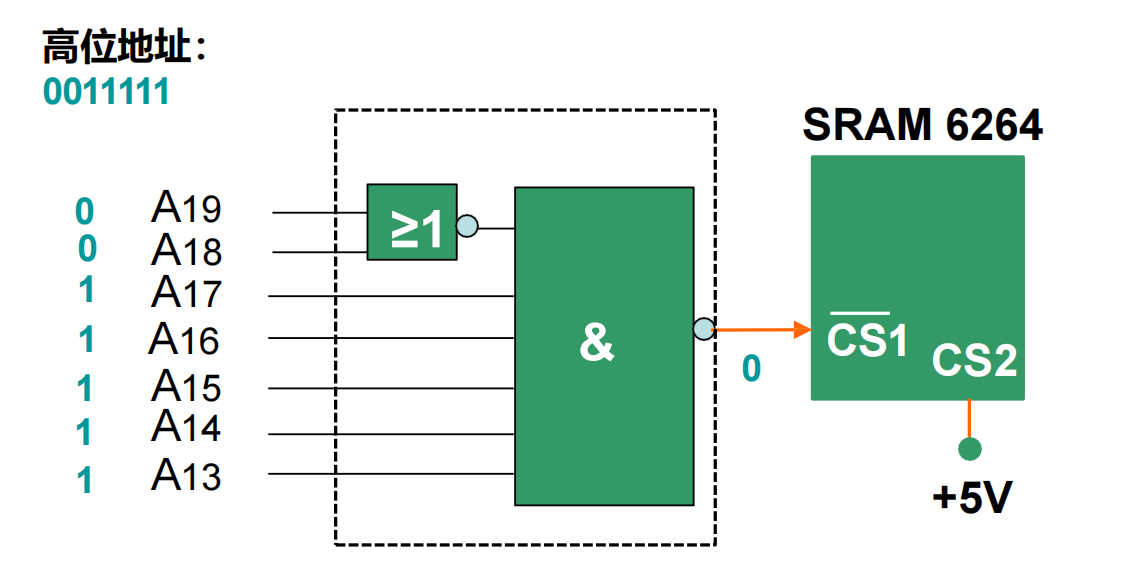

一大考点在于译码电路设计,译码方式分为两种,全地址译码和部分地址译码。

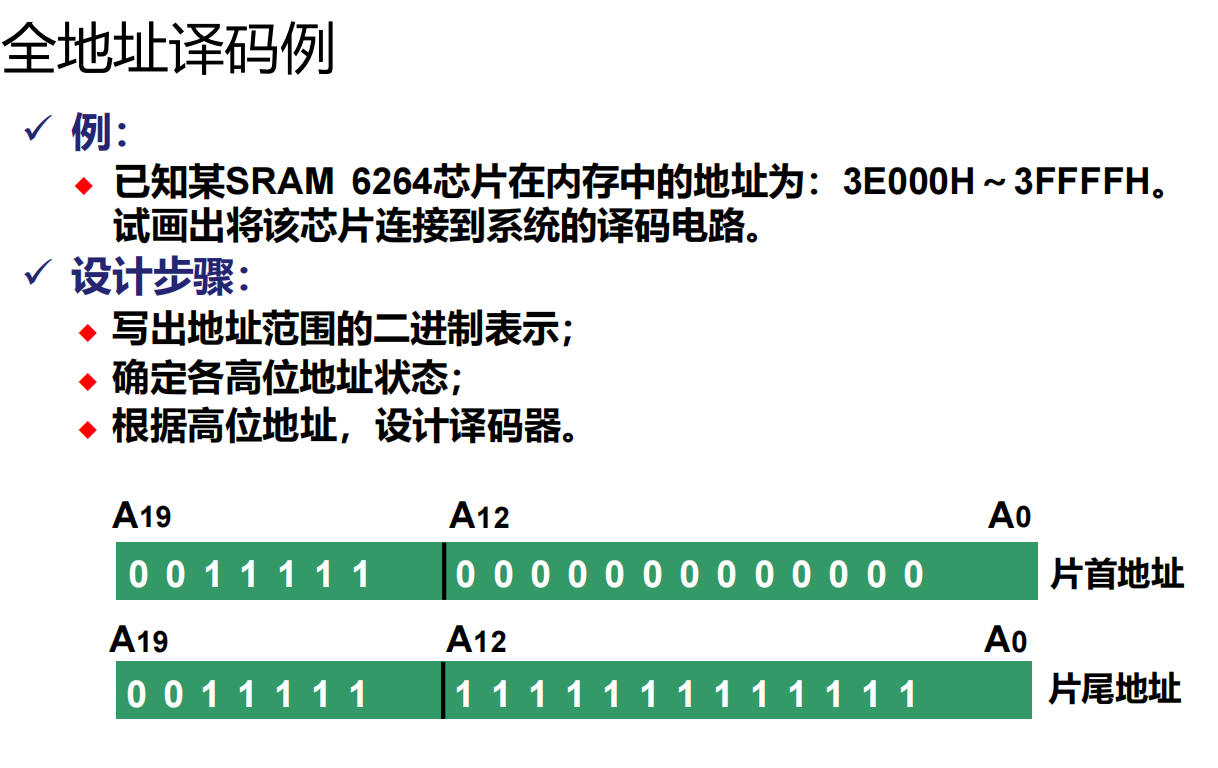

全地址译码用全部的高位地址信号作为译码信号,使得存储器芯片的每一个单元都占据一个唯一的内存地址:

部分地址译码用部分高位地址信号(而不是全部)作为译码信号,使得被选中存储器芯片占有几组不同的地址范围

举个例子就可以简单说明了,这种题都会给出给芯片分配的地址起始和结束地址,要求设计译码电路。

- 首先注意到内存占用大小为\(2^{13}\),因此只需要一个6264芯片

- 然后列出起始地址的二进制表达,可见A19-A13高位不变,参与译码即可

- 0参与或,1参与与,全部正常使给\(\overline{CS}\)输进去片选信号

部分地址译码就是丢掉某个或某些脚,是0是1无所谓,最终的译码信号依然能够正确选择到目标芯片。

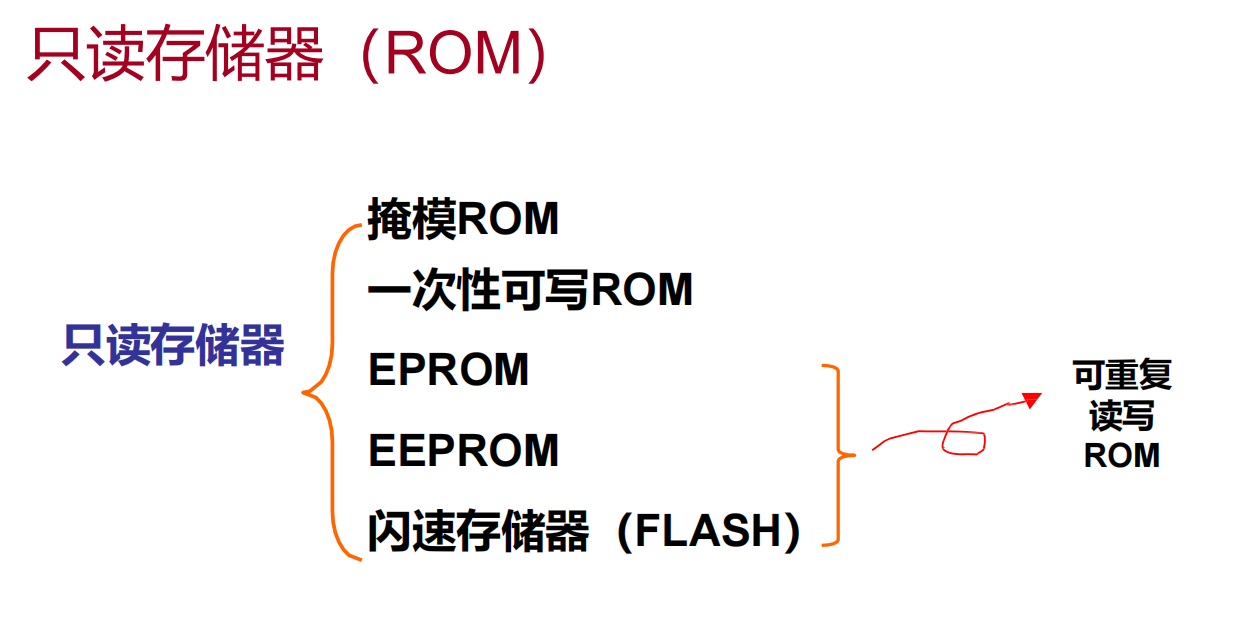

ROM(小题)

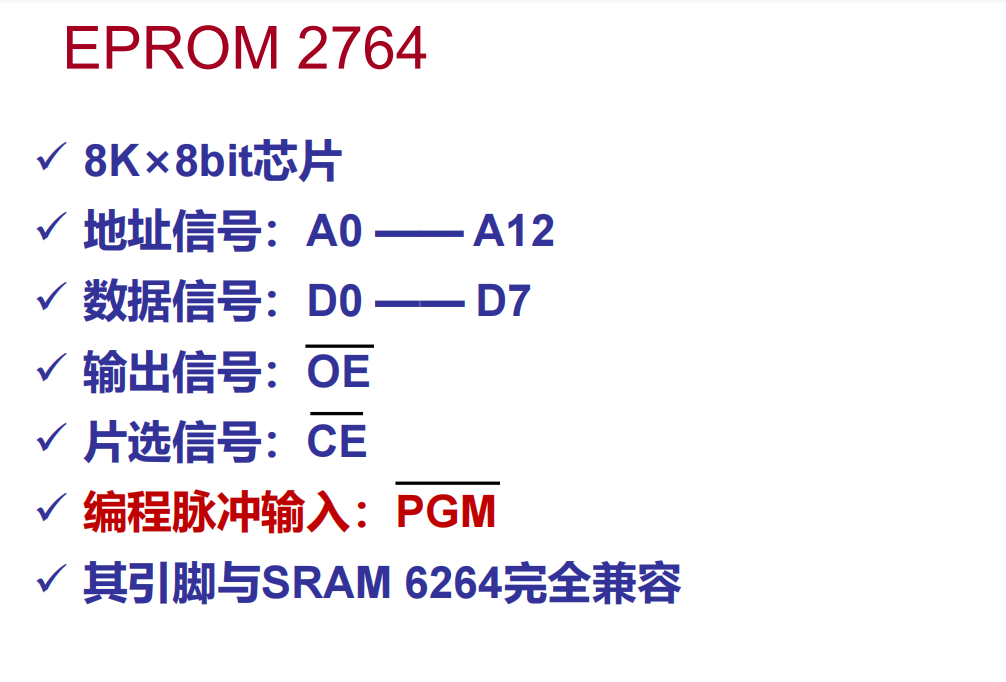

EPROM 2764

- 可多次编程写入

- 掉电后内容不丢失

- 内容的擦除需用紫外线擦除器

以2764为例子,在PGM一个低脉冲期间进行一次编程写入操作,擦除需要紫外线照射。

EEPROM 98C64A

- 可多次编程写入

- 掉电后内容不丢失

- 内容的擦除需用电信号擦除器

引脚为

- 8K×8bit芯片

- 13根地址线(A0 —— A12)

- 8位数据线(D0 —— D7)

- 输出允许信号(OE)

- 写允许信号(WE)

- 选片信号(CE)

- 状态输出端(READY / BUSY)

他的引脚区别在于状态输出端(READY / #BUSY),仅当READY / BUSY=1时才能进行“写”操作

Flash

通过向内部控制寄存器写入命令的方法来控制芯片的擦除和编程操作。Flash存储器的擦除和编程速度比EEPROM快得多,且可以在系统中直接编程。

存储器扩展技术(简答并且画图)

存储器扩展方法

- 位扩展:扩展字长,例如2114

- 字扩展:扩展单元

- 字位扩展:既扩展字长,又扩展单元

位扩展(应该不考,主要记忆字扩展)

位扩展:确保所有芯片具有完全相同的地址范围,对需要位扩展的存储芯片,单独1片没有意义

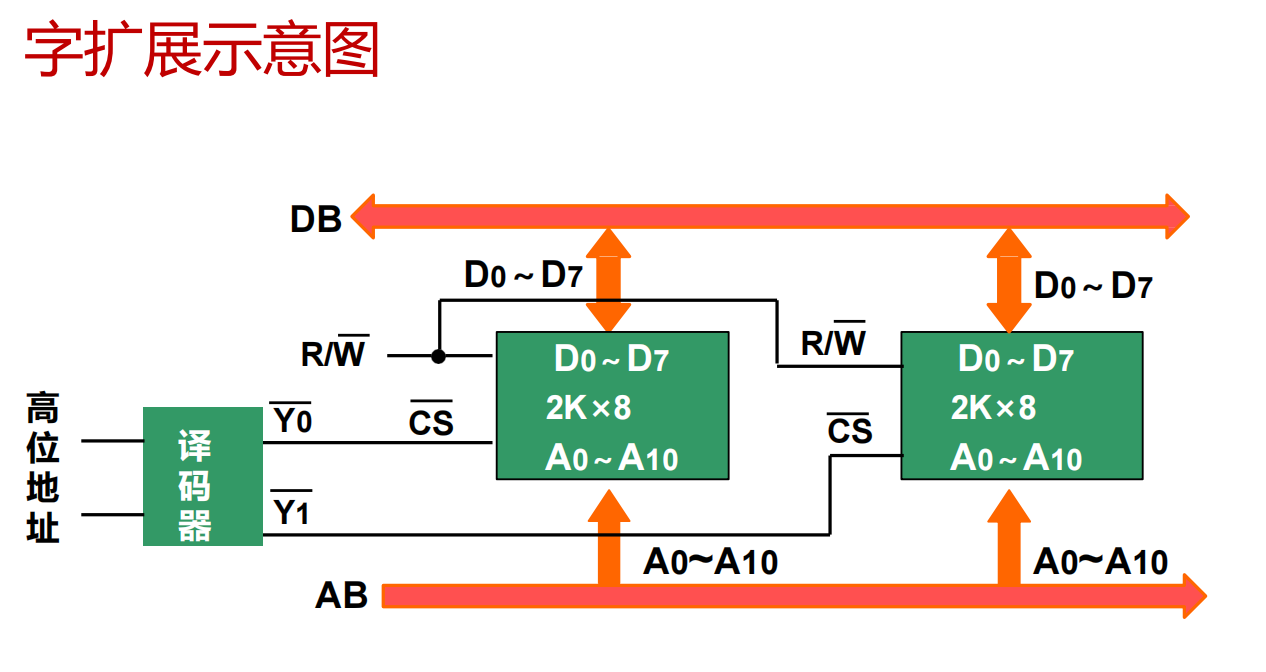

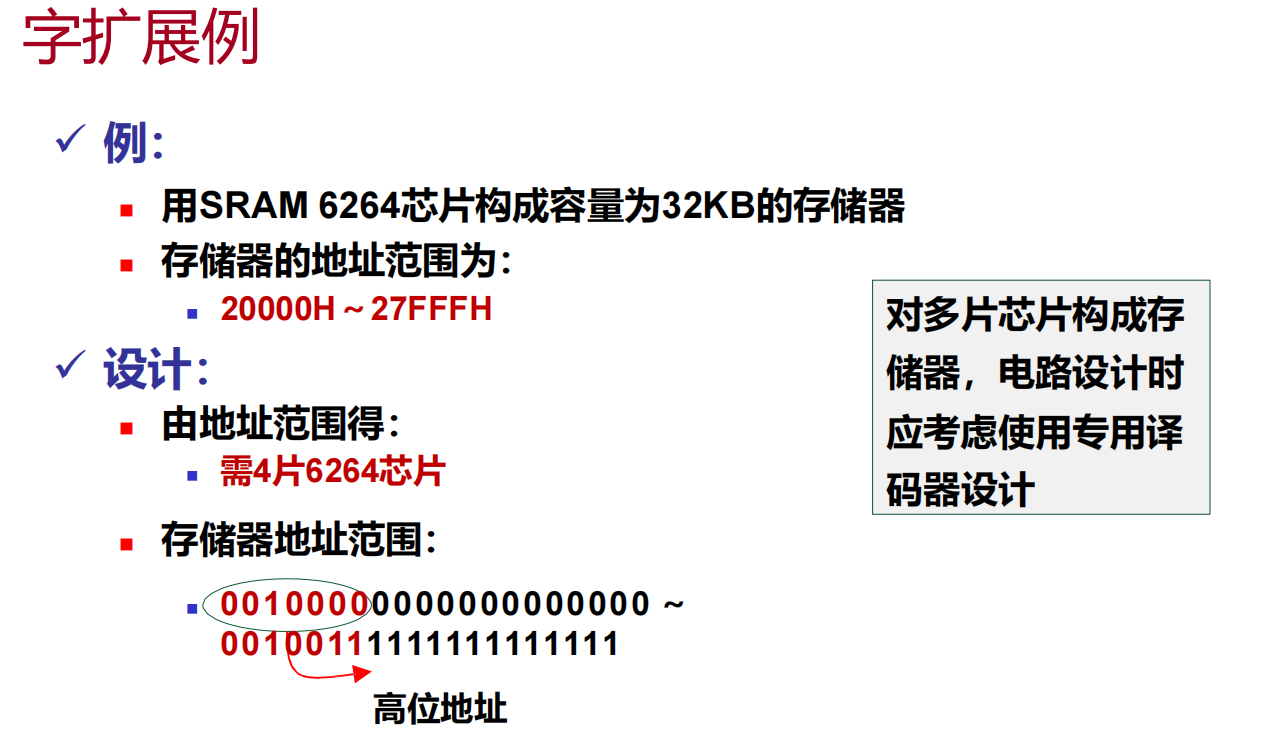

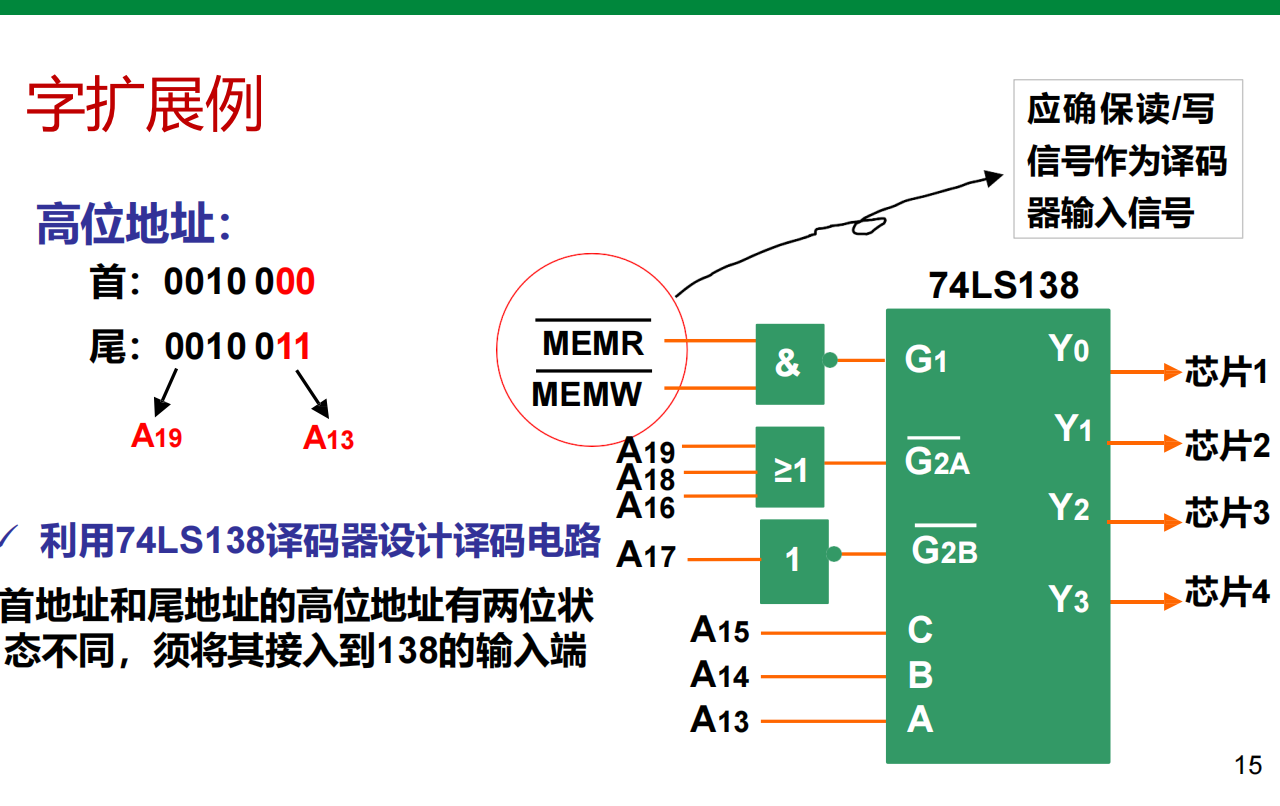

字扩展(考一个画图题)

扩展原则:

- 每个芯片的地址线、数据线、控制线并联。

- 片选端分别引出,以使每个芯片有不同的地址范围

示意图:

关注例题

64=8k*8=8KB,因此需要四片,留出三位做片选,高四位

高速缓存存储器Cache(简答)

为啥需要cache?

CPU与主存之间存在较大的速度差异,例如主频为733MHz的Pentium3处理器执行一次指令的时间为1.35ns,而与其配套的SDRAM存取时间为7ns,速度相差约5倍。为解决这一问题,可以通过以下方法:插入等待周期让CPU等待内存数据、使用速度较快但成本高的SRAM作为内存储器、或在慢速DRAM与快速CPU之间插入速度较快且容量较小的SRAM(Cache),以提高整体存储性能。

cache位置

主内存和cpu之间

cache设置条件

程序的局部性原理(时间+空间)

- 时间局部性:最近的访问项可能在不久的将来再次被访问

- 空间局部性:一个进程所访问的各项,其地址彼此很接近

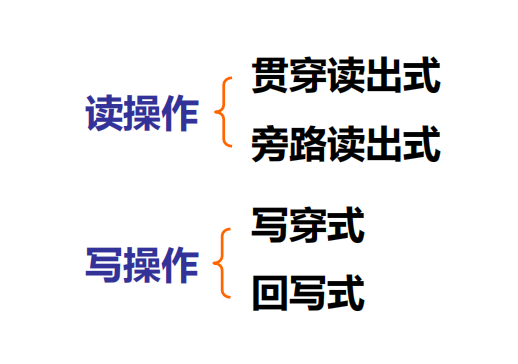

读写操作分类

- 贯穿读出:CPU对主存的所有数据请求都首先送到Cache,在Cache中查找,若命中,将数据送出;如果不命中,则将数据请求传给主存

- 旁路读出:同时对cache和主存读,若cache命中,中断对主存的请求

- 写穿式:从CPU发出的写信号送Cache的同时也写入主存

- 回写式(写更新):数据一般只写到Cache,当Cache中的数据被再次更新时,将原更新的数据写入主存相应单元,并接受新的数据。

微机中的存储器系统

见PPT

浙公网安备 33010602011771号

浙公网安备 33010602011771号