[文档].艾米电子 - 使用Verilog设计的Quartus II入门指南

说明

本文的部分章节,来源于本人翻译的Terasic DE2-115的英文入门文档。

平台

硬件:艾米电子EP2C8-2010增强版套件

软件:Quartus II 10.0 + ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition

内容

- 典型的CAD流程

- 开始

- 新建工程

- 录入Verilog设计

- 编译设计

- 引脚分配

- 仿真设计电路

- 编程及配置到FPGA器件

- 测试设计电路

典型的CAD流程

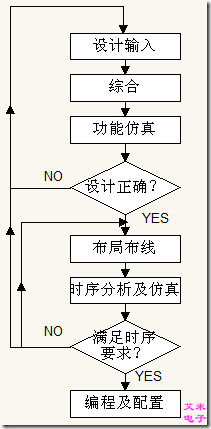

计算机辅助设计(CAD)软件,使得运用可编程逻辑器件实现所需逻辑电路,变得容易。比如现场可编程门阵列(FPGA)。典型的FPGA CAD设计流程如图1所示。

图1 典型的FPGA CAD设计流程

CAD流程包含以下步骤:

- 设计输入——所需电路可通过原理图方式或硬件描述语言方式(如Verilog或VHDL)进行设计。

- 综合——输入的设计被综合进入由逻辑元素(LEs,FPGA芯片提供)组成的电路中。

- 功能仿真——综合电路被测试以验证其功能是否正确,次仿真不考虑时序因素。

- 布局布线——CAD Fitter工具决定网表中定义的LEs如何布置成FPGA芯片中的实际LEs。

- 时序分析——分析已布局布线电路中的不同路径的传播延迟,用以指示所需电路的性能。

- 时序仿真——测试已布局布线电路,验证其是否在功能和时序上都正确。

- 编程及配置——设计的电路,通过编程配置开关,被实现到一个物理的FPGA芯片。配置开关用于配置LEs和建立所需线路连接。

本指南介绍Quartus II软件的基本特征。展示如何使用Verilog硬件描述语言来设计和实现电路。使用GUI来实现Quartus II指令。通过本份指南,读者将学习到:

- 新建工程

- 使用Verilog代码录入设计

- 将综合的电路布局到Altera FPGA

- 分配电路的输入输出到FPGA上的指定引脚

- 仿真设计电路

- 编程配置艾米电子EP2C8核心板上的FPGA芯片

1. 开始

在Quartus II中设计的每个逻辑电路或子电路,叫做一个工程。软件每次运行一个工程,并将所有信息保存在单一文件夹中。欲开始一个新的逻辑电路设计,第一步就是新建一个文件夹来保存文件。为了保存本指南的设计文件,在D盘新建introtutorial文件夹。指南者运行的范例为一个简单的双路灯控电路。

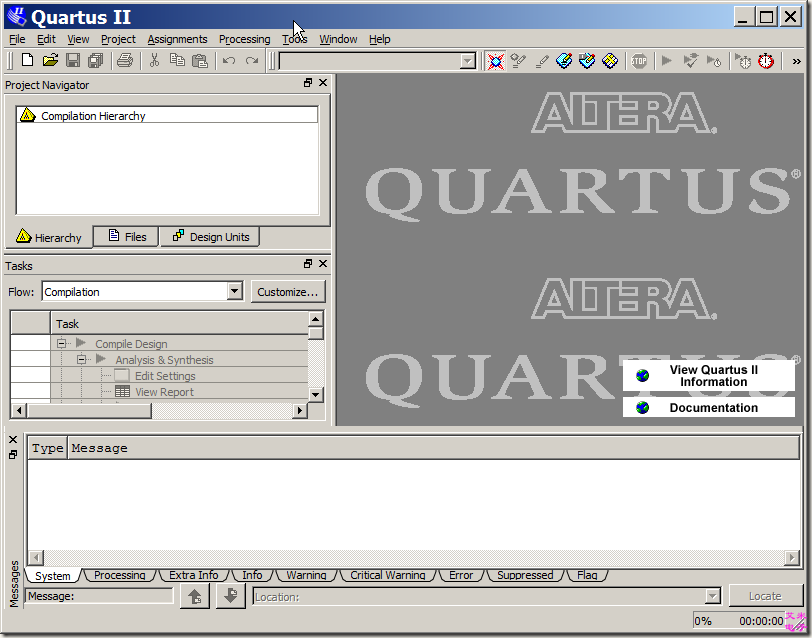

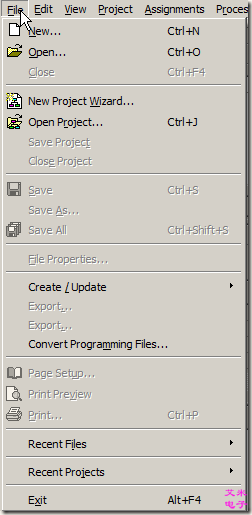

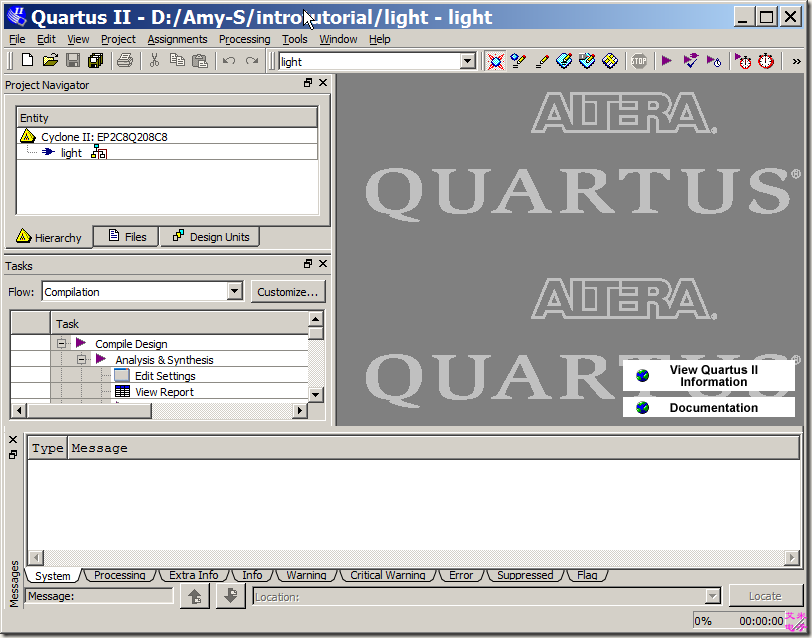

打开Quartus II软件,将看到类似于图2的画面。该显示画面包括若干窗口,用户可使用鼠标选择,以访问Quartus II软件的相关功能。Quartus II提供的大多数命令都可用菜单形式来访问。例如,在图2中,在File标签下点击左键,可打开如图3所示的菜单。用左键单击Exit可退出Quartus II软件。

图2 Quartus II主体显示

图3 File菜单一例

对于有些命令,需要连续访问两个或以上的菜单才可以使用。

1.1 Quartus II在线帮助

Quartus II软件提供了容易理解的在线文档,可解答许多在使用软件时遇到的问题。用户可通过选择Help>Search来快速访问帮助话题,在打开的对话框中,可以输入关键字。另外一个方法是,内容感应帮助,以快速查找指定话题的文档。在大多数的应用中,按住键盘上的F1键将打开一个显示该应用的可用命令的帮助窗口。

2 新建工程

按如下步骤新建工程:

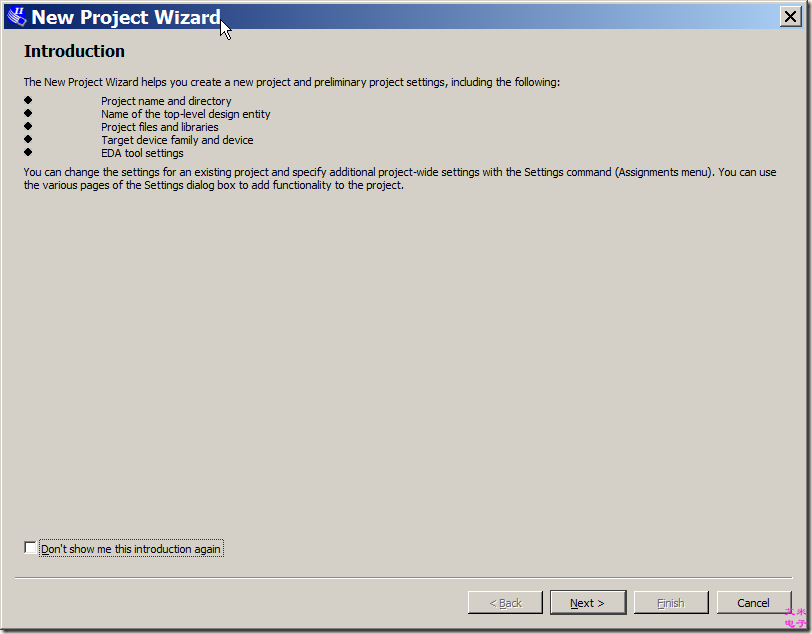

1. 选择File>New Project Wizard,以打开图4所示窗口,可通过Don't show me this introduction again跳过此窗口步骤。单击Next,出现图5所示窗口。

图4 引导的任务显示

图5 创建新的工程

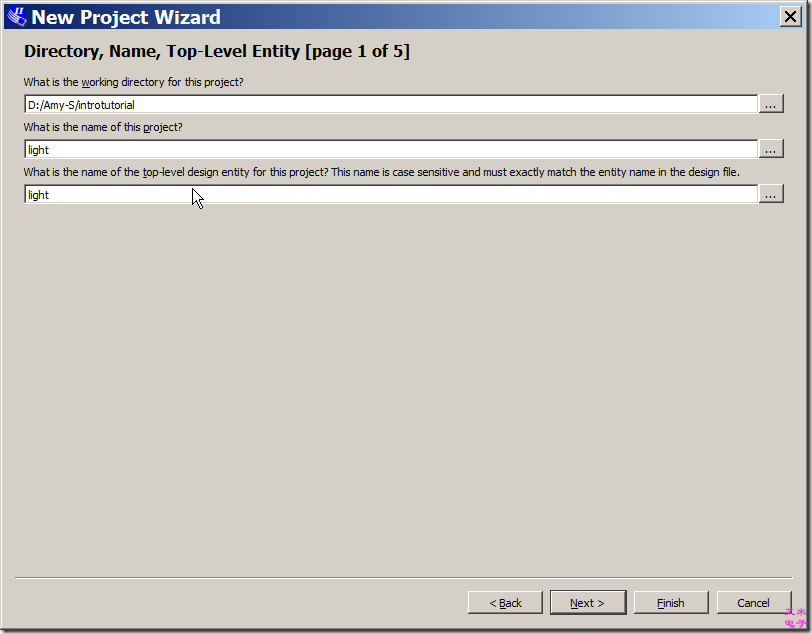

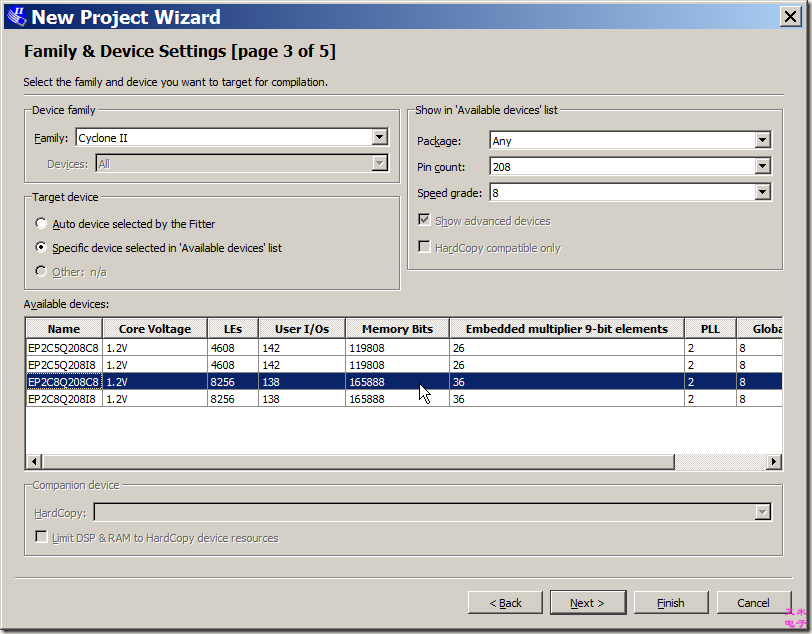

2. 选择工作文件夹introtutorial,也可以使用您自己设定的文件夹。工程必须有一个名字,通常情况下,与顶层设计实体的名字相同。如图5所示,选择light作为工程名和顶层实体名。单击Next。因为还没有创建introtutorial文件夹,Quartus II弹出一个对话框,询问是否新建所需文件夹,如图6所示。单击Yes,将会引出图7所示的窗口。

图6 创建新的工程文件夹与否?

图7 添加用户指定设计文件

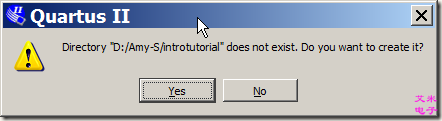

3. 如果没有已存在的设计文件,单击Next,将会打开如图8所示的画面。

图8 选择器件家族和指定的器件

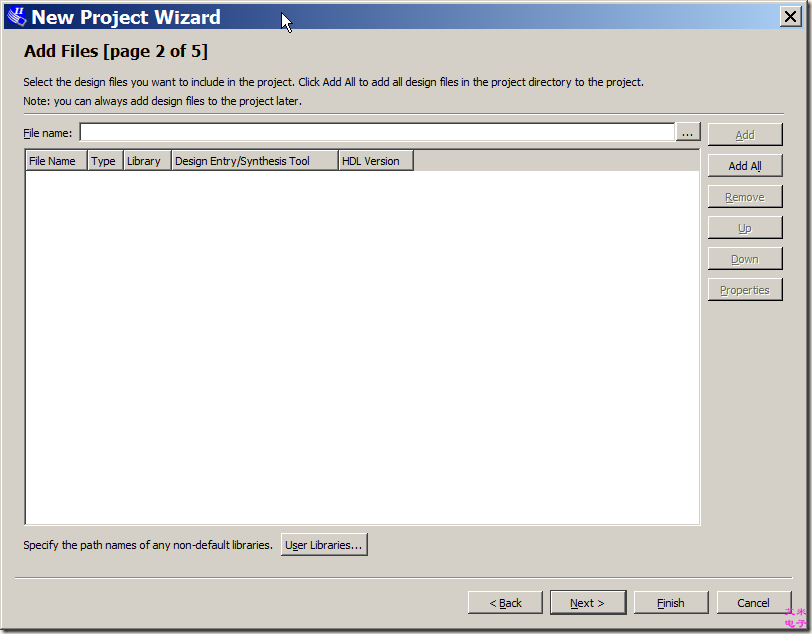

4. 艾米电子EP2C8核心板采用的器件为Cyclone II EP2C8Q208C8。此处选择Cyclone II器件家族,器件为PQFP封装,有208个引脚,速度等级为8。单击Next,出现图9所示画面。

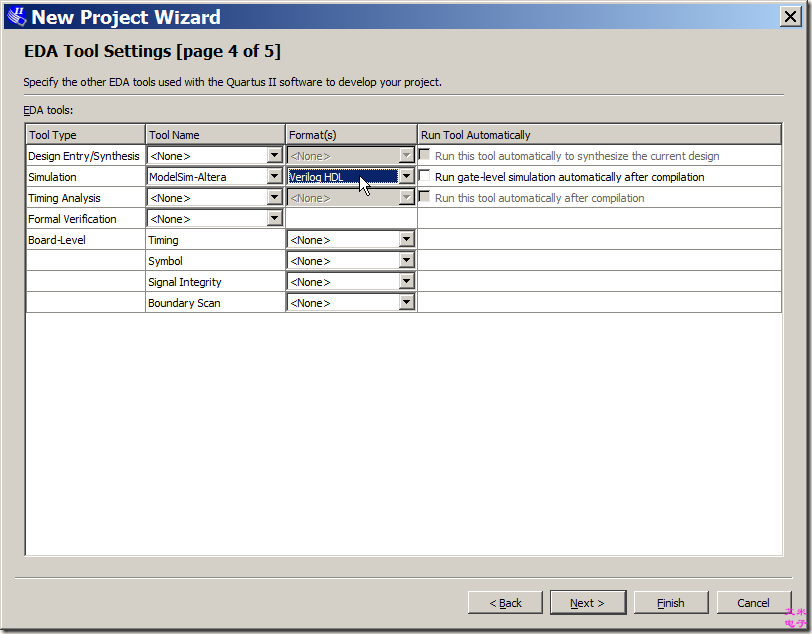

图9 指定第三方EDA工具

5. 用户可指定一些第三方EDA工具。持续Simulation选用ModelSim-Altera,格式为Verilog HDL。单击Next,出现图10所示窗口。

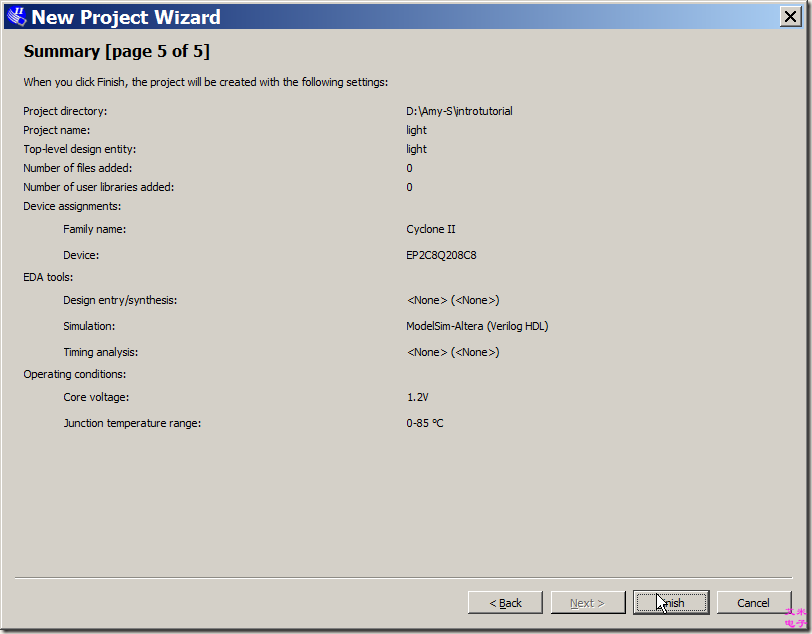

6. 设置一览如图10所示。单击Finish,返回Quartus II主体窗口。标题栏将显示light工程,如图11所示。

图10 工程设置一览

图11 Quartus II显示已建工程

3 使用Verilog代码设计输入

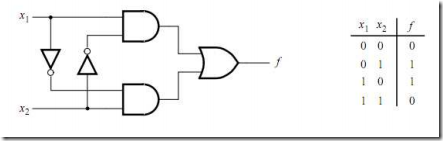

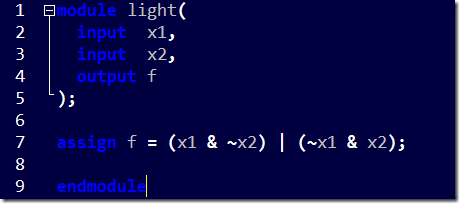

作为一个设计范例,我们将采用双路的灯控电路,如图12所示。此灯可由两个按键中的任一按键来控制,x1和x2,按键的闭合相应的逻辑值为1。真值表也同时在图中给出。注意输入x1和x2是异或的关系,但是我们仍然用门来显示。

图12 灯控电路

所需电路,如图13所示,使用Verilog代码来描述。注意,Verilog模块叫做light,这个图5所示的名称是一致的。此代码的编辑可以使用任何可存储ASCII码的文本编辑器,或者使用Quartus II自带的编辑器。当然,文件的名称可以任意取;而和顶层Verilog模块的名称一致,是一个设计惯例。文件名称必须带.v扩展名,用以指示此文件为Verilog文件。所有,我们使用light.v这个名称。

图13 图12所示电路的Verilog代码

3.1 使用Quartus II 文本编辑器

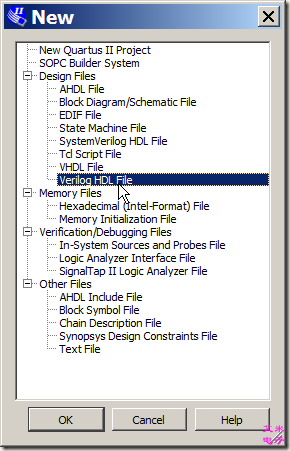

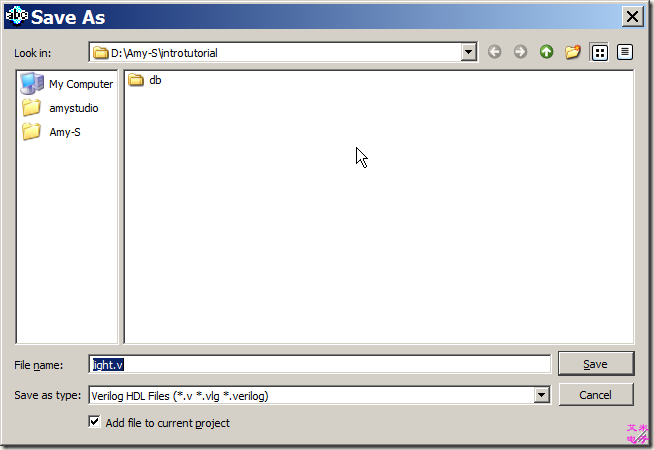

本节将展示如何使用Quartus II文本编辑器。如果你喜欢使用其他文本编辑器来创建Verilog源文件,可以逃过此节。选择File>New打开图14所示窗口,选择Verilog HDL File,并单击OK。这将打开文本编辑器窗口。第一步是指定所创建的文件的名称。选择File>Save As,打开图15所示的对话框。选择存储类型为Verilog HDL File,填写名称为light.v。单击Save,打开图16所示窗口。输入图13所示的代码。使用Ctrl+s保存该文件。

图14 选择新建的文件类型

图15 命名文件

图16 文本编辑器窗口

3.1.1 使用Verilog模板

对于设计者来说,Verilog的语法有时很难被记住。为了解决问题,文本编辑器提供了Verilog模板集。这些模板提供了不同类型的Verilog表达的范例,譬如module声明、always块和设置语句的陈述。可以通过Edit>Insert Template>Verilog HDL来浏览这些模板,以熟悉这些资源,这是相当值得的。

3.3 添加设计文件到工程中

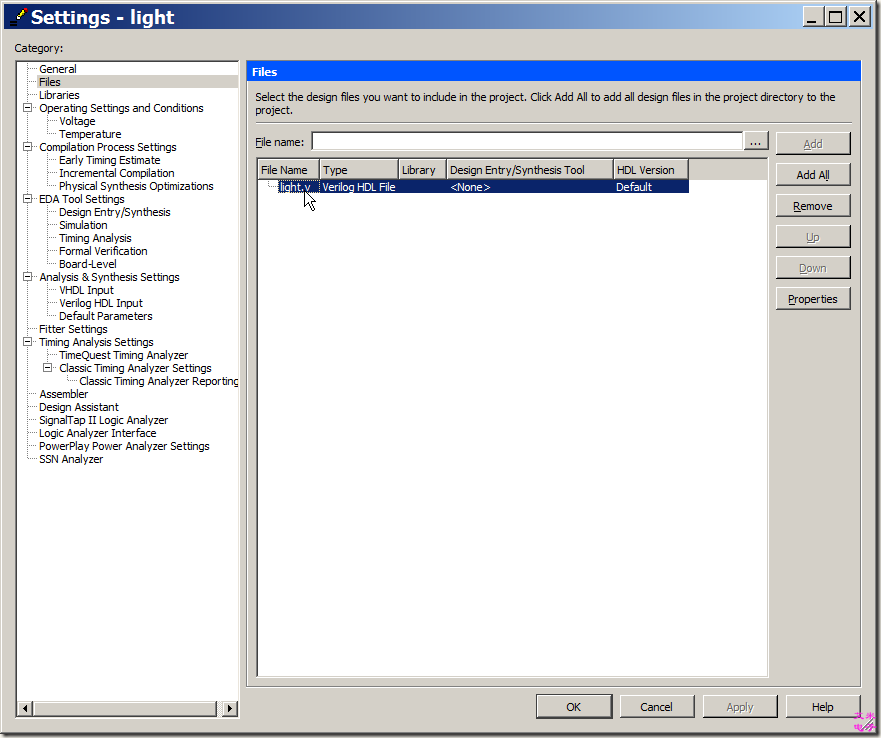

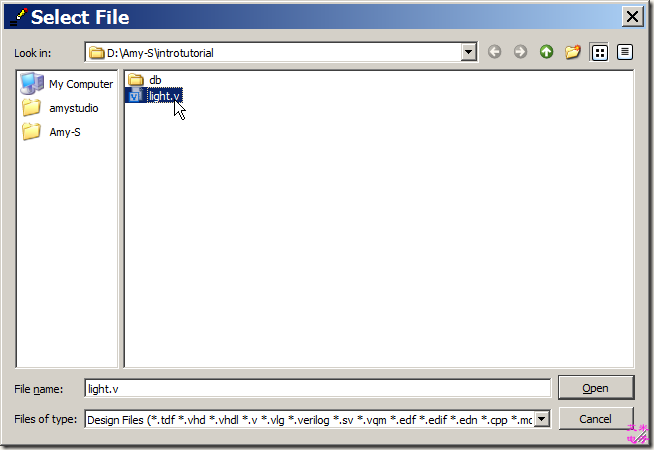

正如图7所讨论的那样,我们可以告诉Quartus II软件,哪些文件是当前工程的一部分。要查看当前的light工程中已包含的文件列表,选择Assignment>Setting>File,这将打开图17所示画面。另外一个可用的方法是选择标签Project>Add/Remove Files in Project。

使用Quartus II文本编辑器创建文件时,勾上Add file to current project选项,所创建文件即自动加入到工程文件列表。如果使用的不是Quartus II自带的文本编辑器,那么图17,列表中就没有所创建的文件,此时必须手动添加文件到工程文件列表中。欲添加文件到工程文件列表中,单击图17中的File Name:的按钮,弹出图18所示对话框,选择light.v,单击Open。再次查看图17画面,此时所添加的文件就已经在文件列表了。需要注意的是,在大多数案例中,Quartus II软件可根据各个实体自动找到正确的文件,即使某些文件没有被认真地添加到工程中。

然而,对于包含许多文件的复杂工程,按照上述方法,添加指定所需文件到工程中,是一个很好的设计惯例。

图17 设置窗口

图18 选择文件

4 编译设计电路

在light.v中Verilog代码,要经过几个Quartus II工具的处理:分析代码、综合电路以及生成目标芯片的实现内容。这些应用程序被聚集在一起,且被称作编译器。

选择Processing>Start Compilation运行编译器,或者单击![]() 按钮运行。在编译过程中,Quartus II的左边会显示不同阶段的进度。编译成功(或不成功)后,会弹出一个对话框。

按钮运行。在编译过程中,Quartus II的左边会显示不同阶段的进度。编译成功(或不成功)后,会弹出一个对话框。

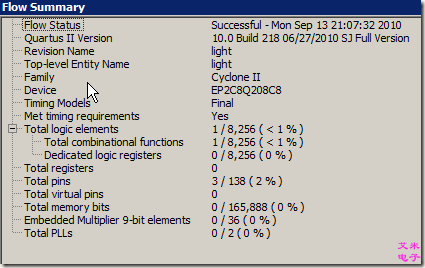

单击OK确认。Qartus II会显示图19所示画面的编译报告。当编译成功后,也可以通过![]() 按钮手动打开编译报告。

按钮手动打开编译报告。

图19 编译报告

在此窗口的左面,列出了许多信息的列表。如图19所示,本工程使用了1个LE和3个引脚。

4.1 错误

在编译期间,Quartus II在消息窗口,会显示生成的消息。如果此Verilog设计正确,其中一条消息就会显示编译成功及无错误。

如果编译不是零错误,那么在Verilog代码中,至少有一个错误。在这种情况下,与错误对应的消息就会在消息窗口显示。双击某条错误信息,该信息将会滚动显示完整;并且打开Quartus II自带文本编译器,Verilog代码中的某行将被高亮显示。类似的,编译器也会显示许多警告消息。同样的方法也适用于查看完整的警告消息。针对于某条错误或警告消息,想得到更多信息,可选住此条消息,然后按住F1功能键,即可查看。

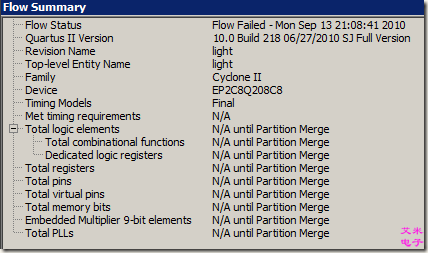

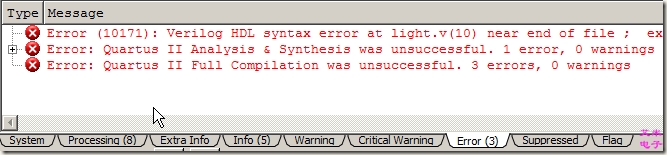

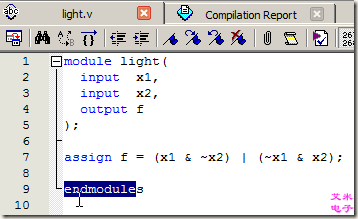

我们将light.v的最后一行改成endmodules,重新编译。Quartus II弹出对话框,报告编译错误;单击OK,以确认。编译报告如图20所示。在消息窗口,单击Error标签,显示图21所示消息。双击第一条错误信息,Quartus II文本编辑器打开light.v,最后一行被高亮,如图22所示。修正代码,重新编译,直至成功为止。

图20 编译报告

图21 错误信息

图22 指示错误代码的位置

5 引脚分配

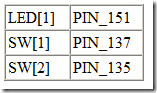

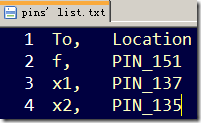

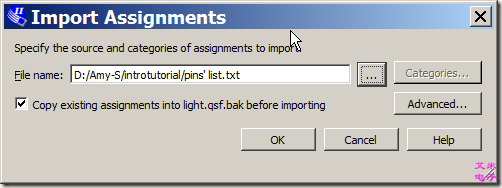

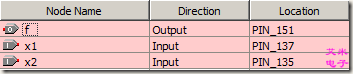

在艾米电子EP2C8-2010增强版套件中,我们使用LED[1]代表f,SW[1]和SW[2]分别代表x1和x2,所需引脚映射如图23所示。使用文本编辑器,新建一文件,命名为pins’ list.txt。录入图24所示内容。选择Assignments>Import Assignments,打开图25所示窗口。选择pins’ list.txt路径,单击OK导入引脚配置。选择Assignments>Pin Planner(或单击![]() 按钮),打开图26所示窗口,查看引脚是否分配正确。

按钮),打开图26所示窗口,查看引脚是否分配正确。

图23 所需引脚映射

图24 引脚分配文件——pins’ list.txt

图25 导入设置

图26 查看引脚分配

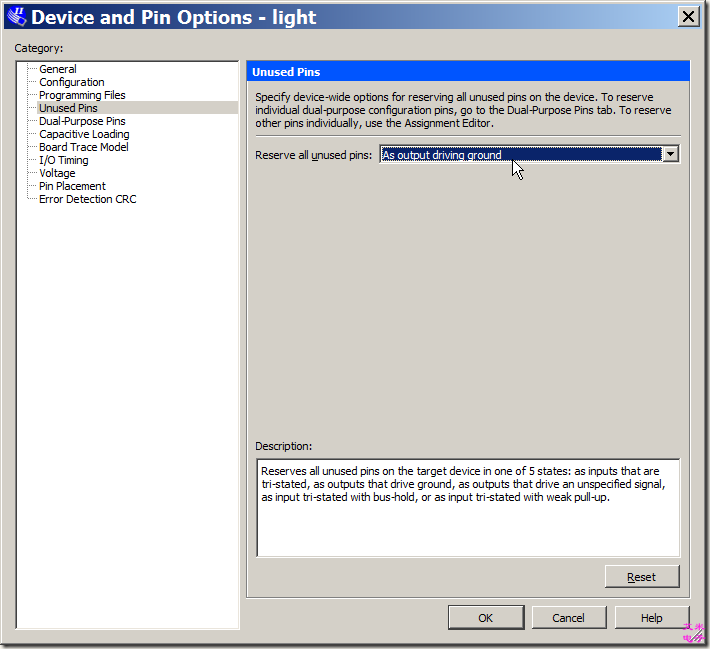

5.1 配置未用引脚

未用引脚需要一定得约束,倘若没有这些约束,就有可能出现一些莫名其妙的问题。选择Assignments>Device>Device and Pin Options>Unused Pins,打开图27所示窗口。一般情况下,按照图28所示配置。

图27 配置未用引脚

图28 配置未用引脚为三态输入

6 仿真所设计的电路

在艾米电子EP2C8-2010增强版套件实现所需电路之前,审慎的做法是,先仿真以确定所设计电路是否正确。下面将介绍如何使用ModelSim-Altera仿真:

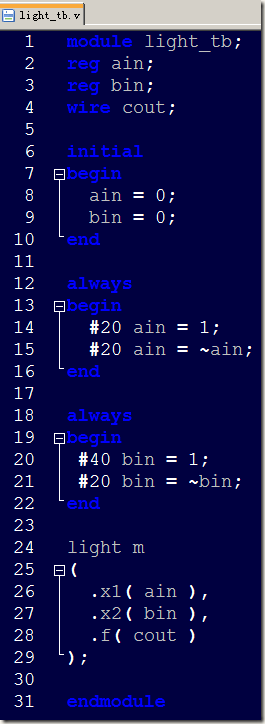

6.1 新建testbench文件

使用文本编辑器新建testbench文件,文件类型与图9一致,命名为light_tb.v;不要勾Add file to current project选项,即不可加入到Quartus工程文件夹列表。录入图29所示代码。

图29 light_tb.v

6.2 设置ModelSim-Altera路径

第一次使用需要先设置ModelSim-Altera路径。选择Tools>Options>General>EDA Tool Options,打开EDA工具选择,如图30所示,设置路径。单击OK,返回Quartus II主题界面。

图30 设置ModelSim-Altera路径

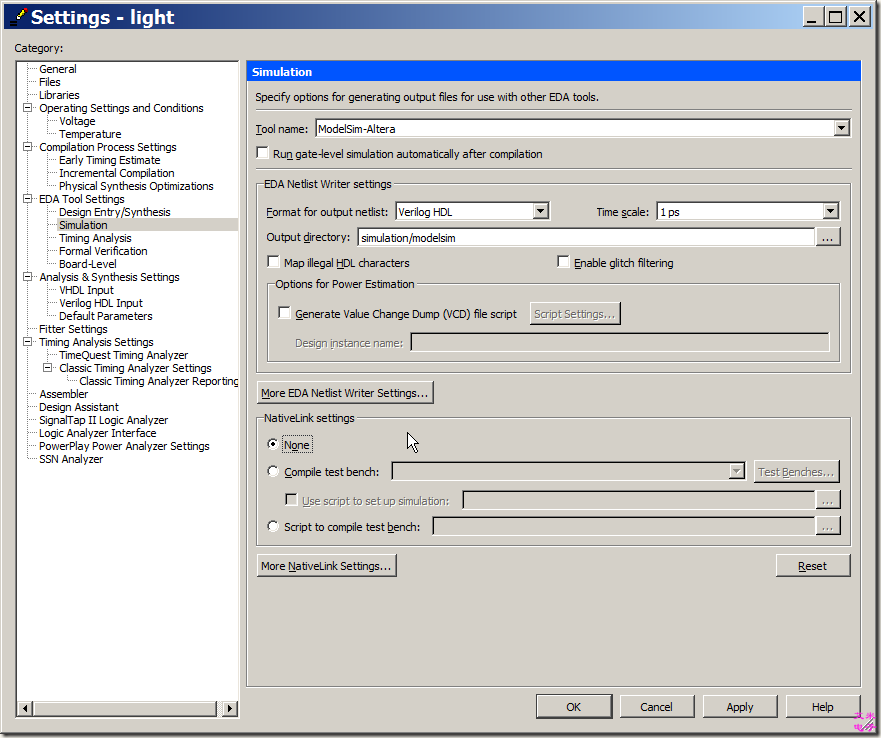

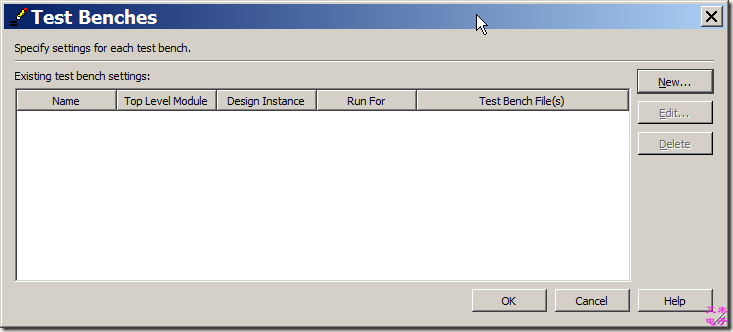

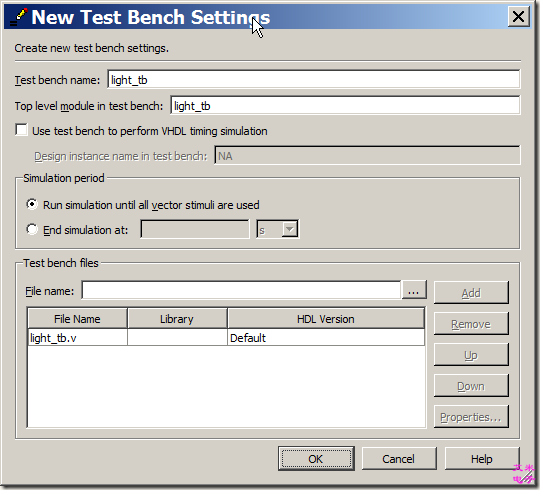

6.3 添加仿真所需测试文件

选择Assignments>Setting>EDA Tool Setting>Simulation,打开图31所示窗口。在NativeLink setting下,选择Compile test bench:标签,单击Test Benches按钮,打开图32所示窗口。单击New,弹出设置窗口,命名Test bench name:为light_tb(与前面编写light_tb.v一致);在File name:处,点击…按钮,添加light_tb文件路径;单击Add,完成后如图33所示。连续三次单击OK,返回Quartus II主题窗口。

图31 仿真选项设置

图32 指定Test Benches

图33 添加Test Benches

6.4 开始仿真

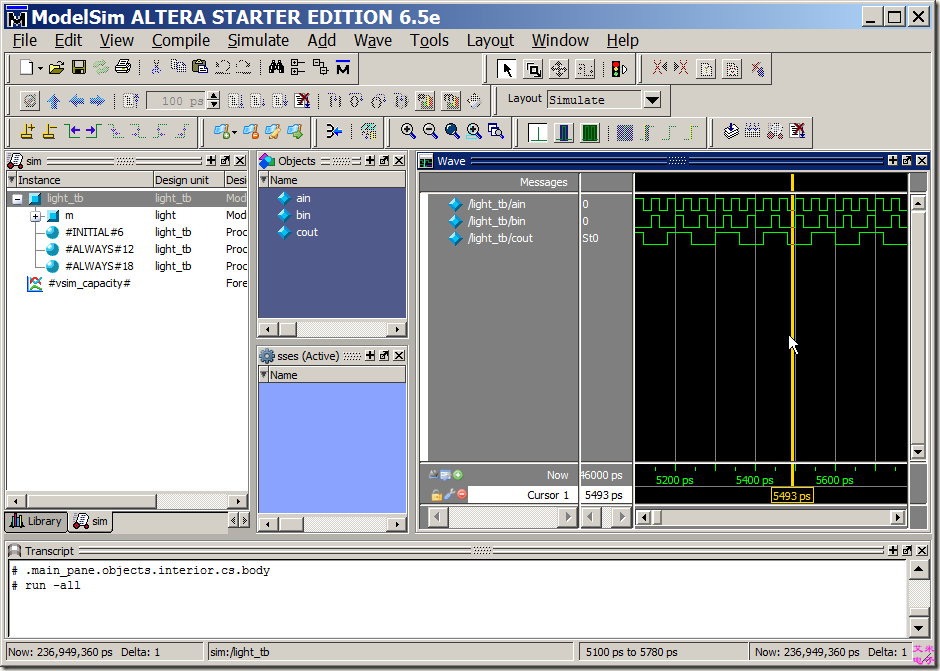

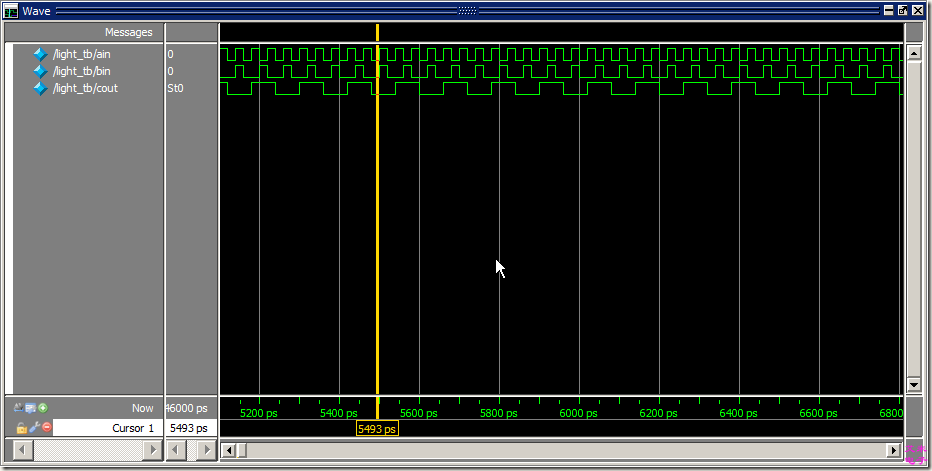

选择Tools>Run EDA Simulation Tool>EDA RTL Simulation,进行RTL仿真;或者选择Tools>Run EDA Simulation Tool>EDA Gate Level Simulation,进行门级仿真。此处以RTL仿真为示范。选择选择Tools>Run EDA Simulation Tool>EDA RTL Simulation,弹出图34所示仿真画面。稍等片刻,波形就会显现。

图34 ModelSim-Altera仿真画面

在Wave窗口右上角,单击![]() ,最大化Wave窗口,方便查看波形,如图35所示。将鼠标放在想要查看的波形上面,按住Ctrl键,滚动鼠标滚轴,可以很方便地放大缩小波形。

,最大化Wave窗口,方便查看波形,如图35所示。将鼠标放在想要查看的波形上面,按住Ctrl键,滚动鼠标滚轴,可以很方便地放大缩小波形。

图35 查看波形

7 编程及配置FPGA器件

7.1 安装下载电缆驱动

- USB-Blaster用户,请参考http://www.altera.com.cn/literature/ug/ug_usb_blstr.pdf

- ByteBlaster II用户,请参考http://www.altera.com.cn/literature/ug/ug_bbii.pdf

-

EthernetBlaster用户,请参考http://www.altera.com.cn/literature/ug/ug_ebcc.pdf

7.2 JTAG编程

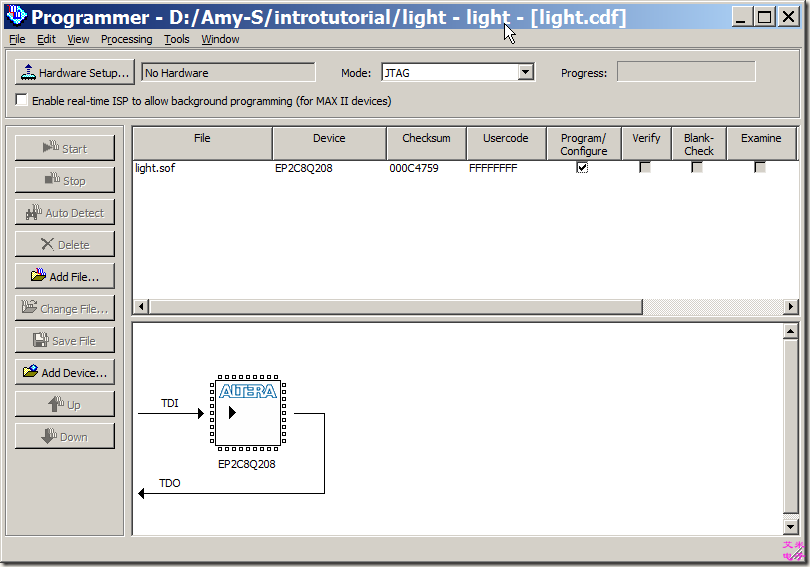

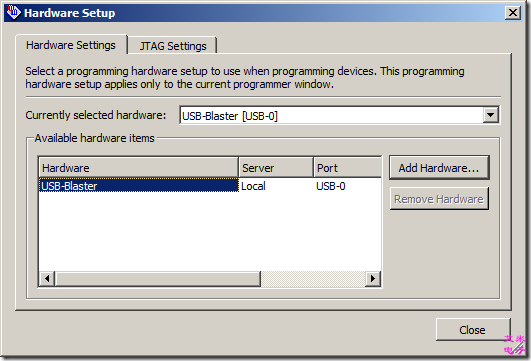

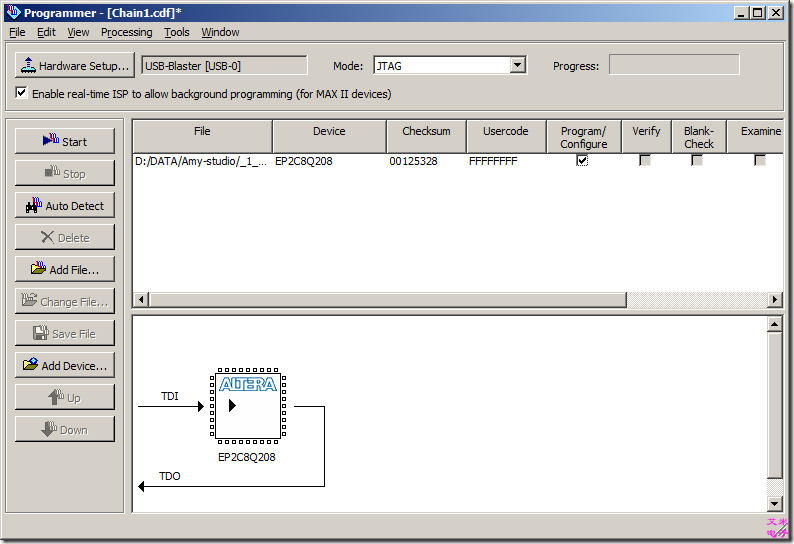

将USB-Blaster与FPGA开发板连接在一起,打开FPGA开发板电源,回到Quartus II主题窗口。选择Tools>Progrmmer或单击![]() 按钮,打开图35所示窗口。选择Mode为JTAG。缺省情况下,USB-Blaster没有被选中,单击Hardware Setup按钮,在弹出的窗口选择USB-Blaster,如图36所示,单击Close退出。

按钮,打开图35所示窗口。选择Mode为JTAG。缺省情况下,USB-Blaster没有被选中,单击Hardware Setup按钮,在弹出的窗口选择USB-Blaster,如图36所示,单击Close退出。

图36 编程器窗口

图37 硬件设置窗口

如图37所示,light.sof已被列入窗口。如果没有列入的话,单击Add File,选择light.sof文件加入。这是一个由编译器的汇编模块生成的二进制文件,它包含配置FPGA器件的数据。.sof文件后缀,表示SRAM目标文件(SRAM Object File)。同时可以注意到,选中的器件为EP2C8Q208,即艾米电子EP2C8套餐所用器件。勾上Program/Configure,单击Start开始下载。

图38 下载SRAM目标文件

8 测试设计电路

下载完毕后,就可以测试实现的电路了。使用SW[1]和SW[2]输入所有可能值,观察LED[1]亮灭是否和预期一致。

进阶阅读

1. Altera.资料:Quartus II 开发软件

参考

1. Terasic.DE2_115_v.1.0_CDROM\DE2_115_tutorials\tut_quartus_intro_verilog.pdf

讲述如何使用Verilog在Quartus II IDE中进行设计的一般流程,及如何搭配ModelSim_Altera来进行仿真的流程。

讲述如何使用Verilog在Quartus II IDE中进行设计的一般流程,及如何搭配ModelSim_Altera来进行仿真的流程。