四步学位PCB评审

作为一个EE,可以不会画layout,但要会layout review,就是,你知道这块板子是什么类型的,哪些在布线布局等设计上有要注意的,大公司的checklist可能会多达成千上万条。学会这些review操作,将风险大的反馈给layout,降低风险,然后一板成功!本文是我翻译的一片外国同行的文章,大家仅供参考。

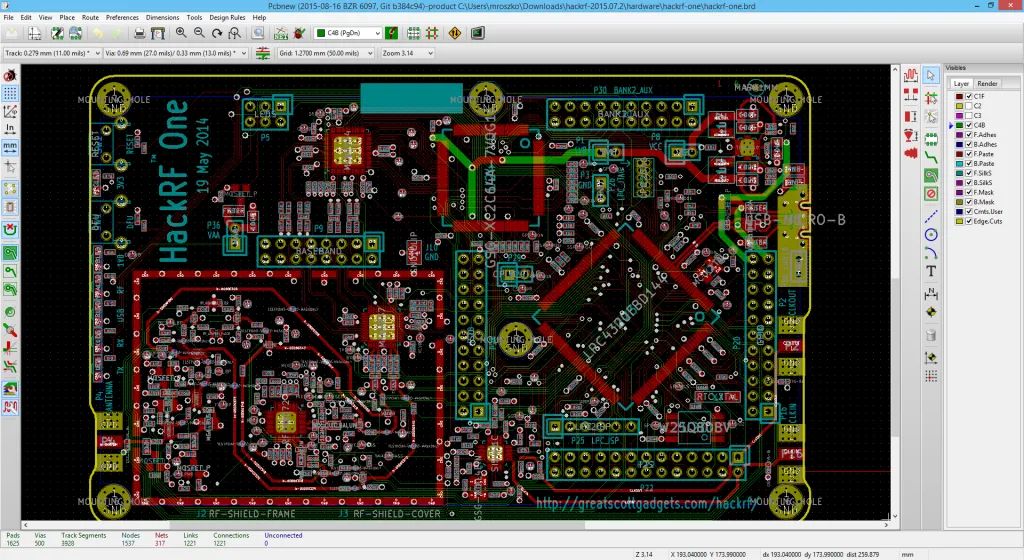

完成原理图的设计和BOM的整理后,就要进入PCB的Layout阶段了。这部分的进度经常会被压缩而且紧张。虽然某些部分的电路性能由原理图决定,但PCB布局最终决定了设计的命运。在布局期间,我们经常需要对板的尺寸,成本,可测试性和可制造性等进行折衷。现在这项设计也变得越来越和多学科相关,比如要了解散热和材料的电气特性等。

一个好的PCB布局审阅者(Reviewer)应该熟悉他们所审阅的电路类型。在PCB布局过程中,应分配预算和时间来检查布局,进行必要的更改,然后重新检查新的布局。现在花费的时间可以避免数小时,数天甚至数周浪费。** PCB布局审查通常可以减少PCB返工,这对于任何项目来说都是一项巨大的时间和成本上的节省。**

步骤一:资料收集和初步验证

1.

在开始审阅之前,请确保所有数据手册,参考设计和叠层信息均可用。

2.

验证原理图设计并签核。

3.

Layout DRC,并消除所有错误

4.

验证每个元件的封装

5.

原理图每个模块分别和PCB对应起来,这样有利于审阅。

6.

确保板尺寸正确,并且安装孔在正确的位置且具有一定的允许公差。

7.

检查是否有板边的信号

步骤二:布局

1.

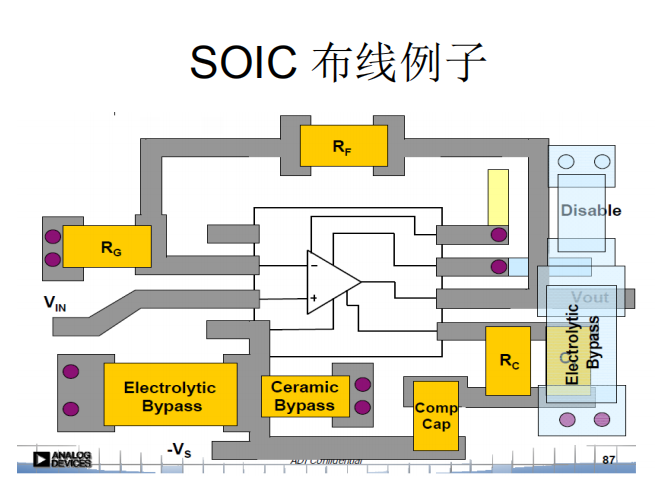

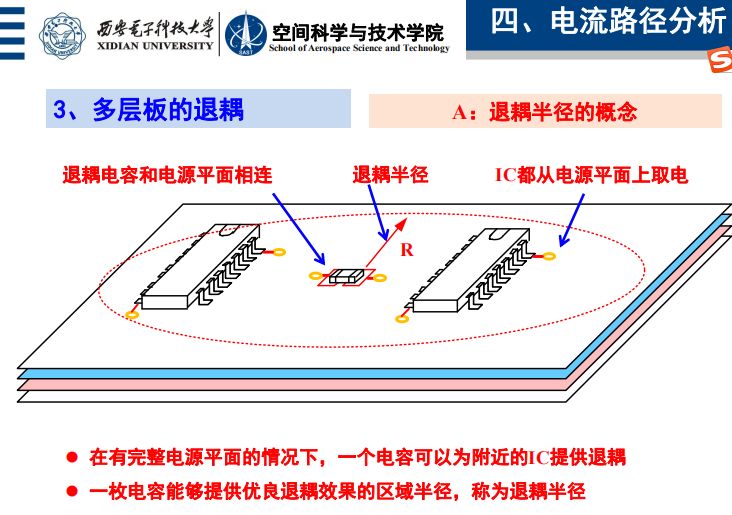

确保去耦电容尽可能靠近引脚放置。

2.

RFI和EMC滤波器应尽可能靠近输入输出。

3.

提供了足够的空间用于操作和散热器安装。

4.

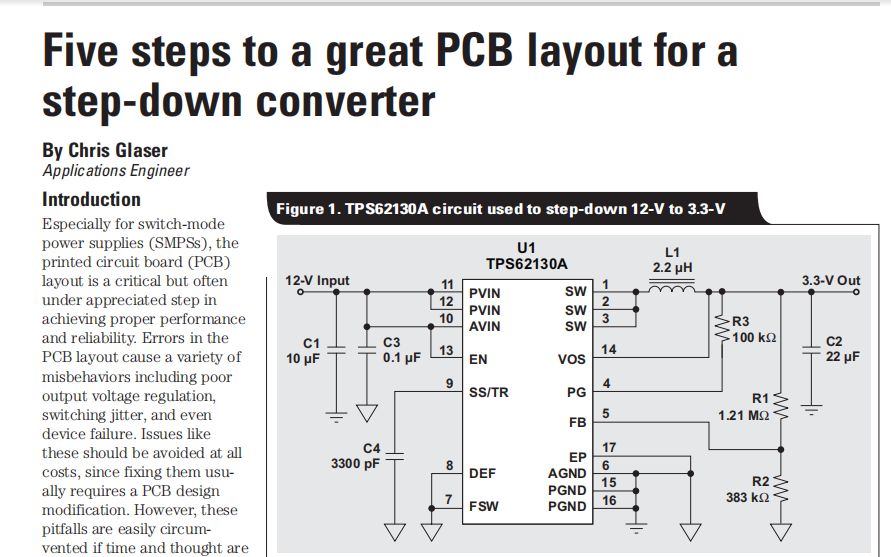

确保正确遵循各个IC的布局指南。

5.

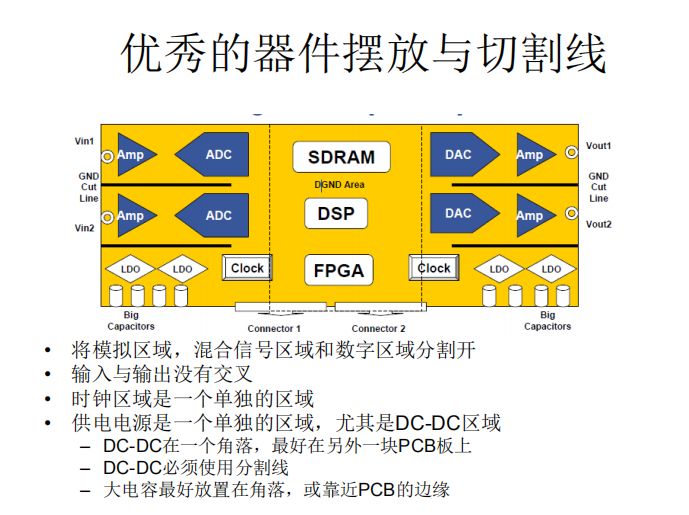

考虑回流路径,分析模拟和数字电路是否干扰。 这将引起信号完整性问题。

6.

所有有线连接器都放置在电路板的一侧,以保持接地电位尽可能接近。否则可能有天线效应。

7.

放置的方式应尽量减小走线长度和交叉。

步骤三:布线

平面

1.

确保数字和模拟电路的公共端仅在一个位置连接。

2.

每个信号在其下方都有其参考平面。

3.

电源线的宽度应与其承载的电流成比例。

4.

确保电源平面中的插槽尽可能少,接地平面应连续。

5.

任何平面都不应在中间形成空的环路。

6.

确保磁性元件和滤波器下方平面挖空,否则会污染平面。

信号

1.

除非特别强调,否则不要有多余的Trace。

2.

尽量保证SMD器件下无走线

3.

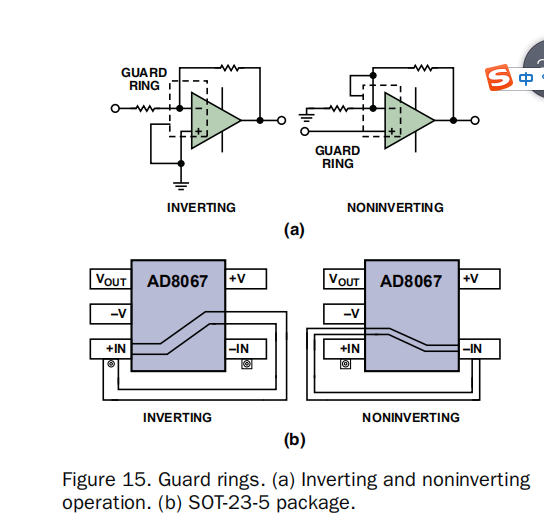

敏感模拟信号需要提供保护环

4.

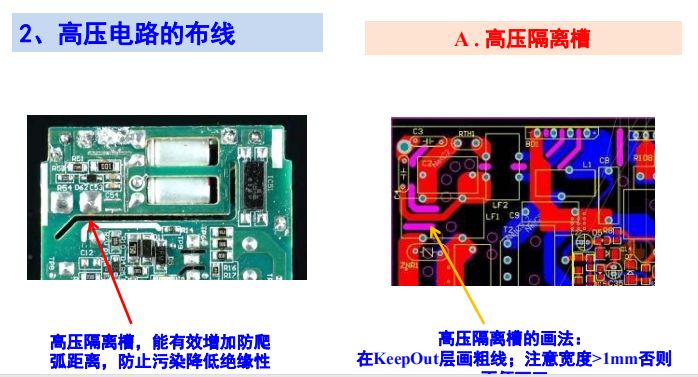

所有信号到板边距离至少20mils。

5.

高速信号的参考平面中间没有截断

6.

根据制造商提供的叠层信息,确定信号阻抗匹配

步骤四:丝印

1.

确保IC下或焊盘上没丝印。

2.

遵循同向。

3.

LOGO和版本号等。

PCB设计没有某些规则,许多规则相互矛盾。由于没有一个问题的固定解决方案,因此有时将其视为艺术,在这里经验比什么都重要。

全文完。下面可以欣赏一些别人的经验:

自我介绍:B站资深恰饭Up,双985通信专业毕业,擅长高速数字电路设计(X86/FPGA/ARM等)。不定期分享硬件电路设计干货,知识体系,有趣专业实验。包括但不仅限于学习方法、模电、FPGA、小信号、高速电路、信号完整性、Layout、嵌入式、学习方法。已帮助成千上万电子专业学生和初级工程师入门成长。技术交流群集合了众多经验丰富的技术大牛,交流氛围极佳。我的宝藏都在这了。

posted on 2021-09-07 19:28 yiludaifei 阅读(75) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号