Verilog基础语法

1.基本词法

Verilog区分大小写;

所有的关键字均为小写;

内部信号(标识符)可以是字母,数字,_,$的任意组合,但第一个字符只能是字母或者下划线;

input为关键词,res和RES是两个不同的标识符

input res; input RES;

2.模块和端口

在Verilog中,模块(module)是最基本的组成单位。

模块声明由关键字module开始,endmodule结束。每个模块有一个模块名,模块的端口列表描述模块的输入和输出端口。

模块内部由5个部分组成:变量声明、数据流语句、低层模块实例、行为语句块、任务和函数。这些部分可以在模块的任意位置以任意顺序出现。

模块名为top_module,输入端口in,输出端口out

module top_module( input in, output out ); ... endmodule

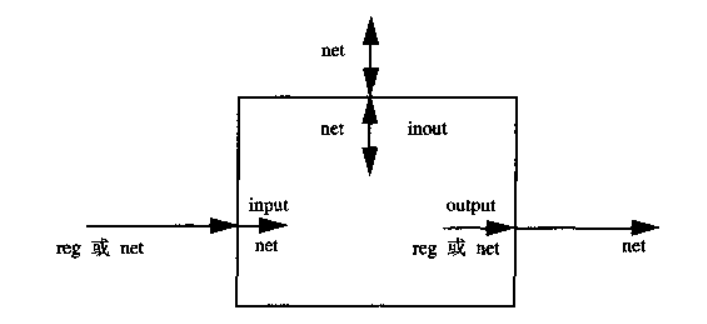

端口是模块与外界交互的接口,对外部环境来说,模块内部不可见,对模块的调用只能通过端口进行。

端口列表中所有端口均需在模块中声明,Verilog端口主要有三种:

(1)input:输入端口,从外界读取数据,在模块内不可写。

(2)output:输出端口,往外界发送数据,在模块内不可读。

(3)inout:数据可双向流动。

端口声明有以下两种:

module adder(a, b, cin, sum, cout); // 端口声明开始 input a,b,cin; output sum,cout; // 端口声明结束

...

... endmodule

module adder( input a, input b, input cin, output sum, output cout); // 括号中直接声明

...

... endmodule

Verilog中的变量类型

reg :本质是存储器,具有寄存功能;

wire(net):本质是一条没有逻辑的连线;

端口默认数据类型为wire型,如果希望输出端口能保存数据,则声明成reg型。

注意:不能将input类型的端口声明为reg,因为reg类型变量用于保存数据值,而输入端口反映的是与其相连的外部信号的变化,不能保存这些信号值。

3.Verilog常用数据类型

Verilog最常用的数据类型:wire、reg、parameter、integer

wire

wire 类型常用来表示以assign关键字指定的逻辑信号,是Verilog输入输出信号的默认类型,其表示硬件单元之间的物理连线,由其连接的器件输出端连续驱动。

格式:wire[n-1:0] 数据名1,数据名2,...,数据名N;含义:定义了N个变量,每个变量位宽为n;

// 定义了3个位宽为4的变量 wire[3:0] a,b,c;

reg

reg是寄存器数据类型变量的关键字。reg常用来表示always模块内的指定信号,代表触发器。

格式同上。与wire区别在于:reg型保持最后一次赋值,wire需要持续驱动

parameter

在Verilog中用parameter定义常量,该类型主要用来提高程序可读性以及方便维护。

格式:parameter 参数名1 = 数据名 1;

parameter a = 1; parameter[2:0] b = 3'h4;

integer

integer是整型变量,是一种用于过程赋值语句的通用的寄存器型变量,声明时不用指定位宽,通常用于for循环中指定循环次数。

4.Verilog中的数值种类和运算操作

Verilog 有四个基本的值表示硬件电路中的电平逻辑:0;1;x或X:未知;z或Z:高阻。

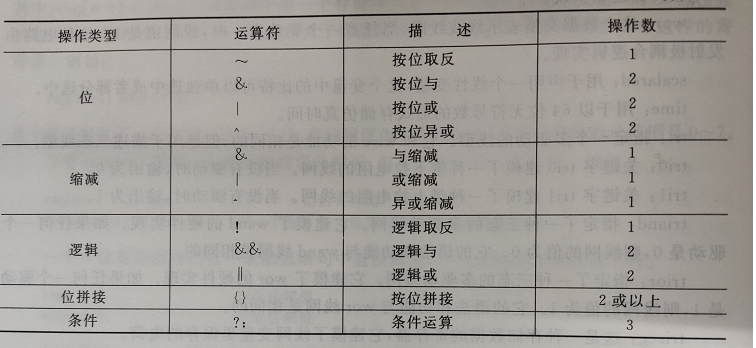

运算操作符:

运算优先级:

举例说明两种移位运算符:>>和>>>,前者表示逻辑右移,后者表示算术右移

逻辑移位(<<和>>)时移入的是0,算术右移(>>>)时移入的是标志位(即最高位),而算术左移(<<<)时移入的是0。

逻辑左移和算术左移结果相同。

| a | a>>2 | a>>>2 | a<<2 | a<<<2 |

| 0100_1111 | 0001_0011 | 0001_0011 | 0011_1100 | 0011_1100 |

| 1100_1111 | 0011_0011 | 1111_0011 | 0011_1100 | 0011_1100 |

浙公网安备 33010602011771号

浙公网安备 33010602011771号