Memory Systems_ Cache, DRAM, Disk (2010)-学习笔记4-What to Cache, Where to Put It, and How to Maintain It

What to Cache, Where to Put It, and How to Maintain It

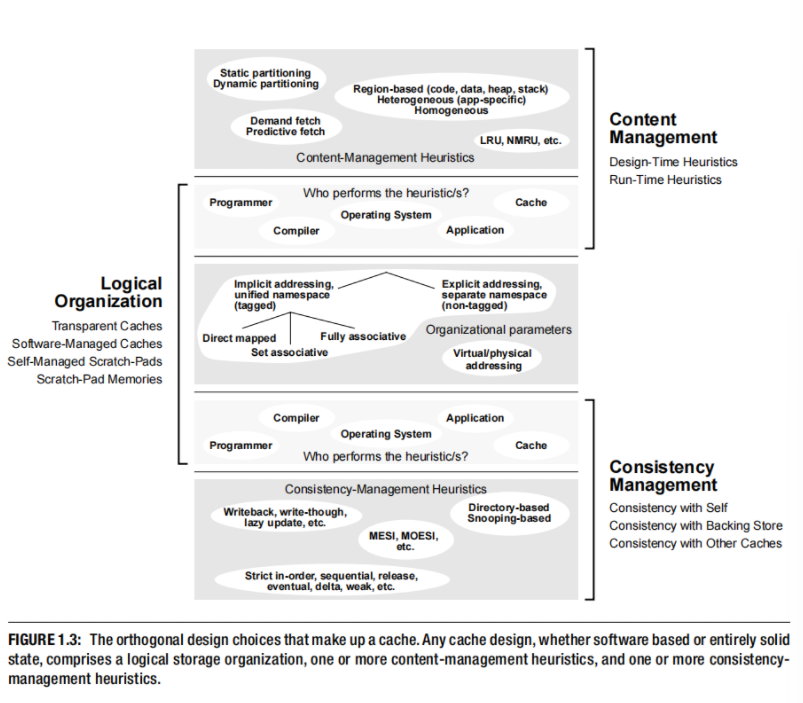

What to Cache(缓存什么)、Where to Put It(缓存在哪里)、How to Maintain It(如何维护缓存)

- 决定缓存中放什么(What to cache)

即选择哪些数据应该存入缓存。这一决策可以由程序员、编译器、运行中的应用程序、操作系统,或者缓存硬件本身,通过静态或动态的方法来做出。 - 内容管理启发式方法(Content-management heuristic)

管理缓存数据的策略,比如什么时候加载数据、什么时候替换数据等。这个策略的执行者也可以是上述任何一方。 - 缓存的物理和逻辑存储方式(Logical organization)

指缓存内部如何布局数据,包括物理空间和逻辑结构上的组织形式。 - 缓存一致性维护机制(Consistency management)

保证缓存中的数据和主存储中的数据保持一致。这一机制可以由应用程序、操作系统或缓存硬件共同完成。 - 组合的灵活性

缓存设计允许将任何逻辑组织与任何管理策略组合使用,设计灵活。

1.3.1 Logical Organization Basics: Blocks, Tags, Sets

缓存会存储来自主存(backing store,例如主内存或硬盘)的一段数据,这些数据块叫做 缓存块(cache block) 或 缓存行(cache line)。由于这种按块组织的方式,我们会把主存逻辑上划分为若干个与缓存块大小一致的部分,这样做的一个好处是,我们可以用一种简单有效的方式来标识每一个块块 ID(block ID)。

Cache结构:

整体存储结构,分为多个 Set(集合)。

Cache

├── Set[0]

│ ├── Block 0

│ │ ├── Valid bit

│ │ ├── Tag

│ │ └── Data (Cache block)

│ └── Block 1

│ ├── Valid bit

│ ├── Tag

│ └── Data (Cache block)

│ ...

├── Set[1]

│ ├── Block 0

│ ├── Block 1

│ ...

└── Set[n-1]

一个缓存条目(cache entry,也叫 cache line)通常包括三个主要部分,条目的实现形式可以多种多样,比如硬件里的 SRAM 数组,也可以是软件中的二叉树,甚至是链表:

| 字段 | 作用 |

|---|---|

| Tag(标签) | 用来标识该条目存储的是主存的哪个块(由 block ID 提供) |

| Status(状态) | 标记该缓存条目是否有效、是否被修改(Valid、Dirty 等) |

| Data(数据) | 缓存的数据块内容,通常是一整块数据(比如 16B、64B) |

cpu会生成内存地址,当我们数据时(比如内存地址为 0xABCDEF10),该地址会被拆分成两个部分:

| 字段名 | 位数(示例) | 位范围(从高位到低位) | 作用说明 |

|---|---|---|---|

| Tag | 28-n位 | 31 – 3-n | 用于唯一标识内存块(块ID的一部分),用来和缓存块中的Tag比对,判断缓存是否命中 |

| Index (Set ID) | n 位 | 3+n - 3 | 用来确定数据块所属的缓存组(set),快速定位缓存组 |

| Block Offset | 4 位 | 3 – 0 | 块内字节偏移,用来定位缓存块中具体的字节 |

如果缓存的大小只有一个块(block),那么它的组织结构是很明显的:新数据会直接放入这个唯一的缓存块中,替换之前存储的数据。但是,一旦缓存有多个块,其组织结构就变成了一个问题:第二个块应该放在哪里?对应特定块ID的数据只能出现在缓存中的一个条目里,但我们可以灵活选择这个条目的位置。我们用图中的纵向和横向维度来表示一组等价类;每一行就是一个等价类,称为“缓存组”(cache set)。一个特定数据块所属的唯一缓存组,通常是由块ID的一部分位来决定的,如图1.6所示。

确定了缓存组之后,这个数据块可以被放在该组内的任何一个块中。

根据这种等价类机制,缓存组织基本有三种类型:

- 直接映射缓存(Direct-Mapped Cache):每个缓存组只有一个块,因此每个块自己就是一个等价类。

- 全相联缓存(Fully Associative Cache):整个缓存只有一个组,所有块都属于同一个等价类(又称内容可寻址存储器)。

- 组相联缓存(Set-Associative Cache):介于两者之间,有多个缓存组(如果只有一个组,就是全相联缓存),且每组中有多个块(如果每组只有一个块,就是直接映射缓存)。

1.3.2 Content Management: To Cache or Not to Cache

从上一小节的信息可以得出cpu访问cache的流程

+---------------------+

| CPU发出内存访问请求 |

+----------+----------+

|

v

+----------------------------+

| 从内存地址解析出: |

| - Block ID(块ID) |

| - Set Index(组索引,若有) |

| - Byte Offset(块内偏移) |

+------------+---------------+

|

v

+----------------------------+

| 根据 Set Index 定位缓存组 |

| (直接映射只有一个块, |

| 组相联多个块, |

| 全相联是整个缓存作为一个组) |

+------------+---------------+

|

v

+----------------------------+

| 在该组内搜索匹配的 Tag |

| (即对应的块ID) |

+------------+---------------+

|

+----+----+

| |

命中(Hit) 未命中(Miss)

| |

v v

+-------------+ +--------------------+

| 取出数据 | | 从主存读取对应块数据 |

| (根据Byte | | 将数据放入缓存 |

| Offset定位)| | 替换缓存中旧块 |

+------+------+-+--------------------+

| |

v v

+-----------------+

| 返回数据给CPU |

+-----------------+

浙公网安备 33010602011771号

浙公网安备 33010602011771号