AD学习笔记(16)——PCB Nets的管理与添加

很多Protel老工程师一般习惯直接绘制无网络的导线条进行PCB设计, 往往是只有设计工程师自己比较清楚连接关系,而会给后期维护的工程师造成相当大的困扰。

1、单个网络的添加

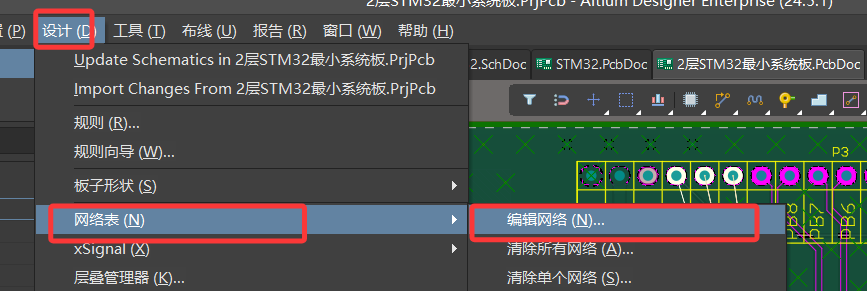

(1)点击设计 -> 网络表 -> 编辑网络,进入添加网络的界面

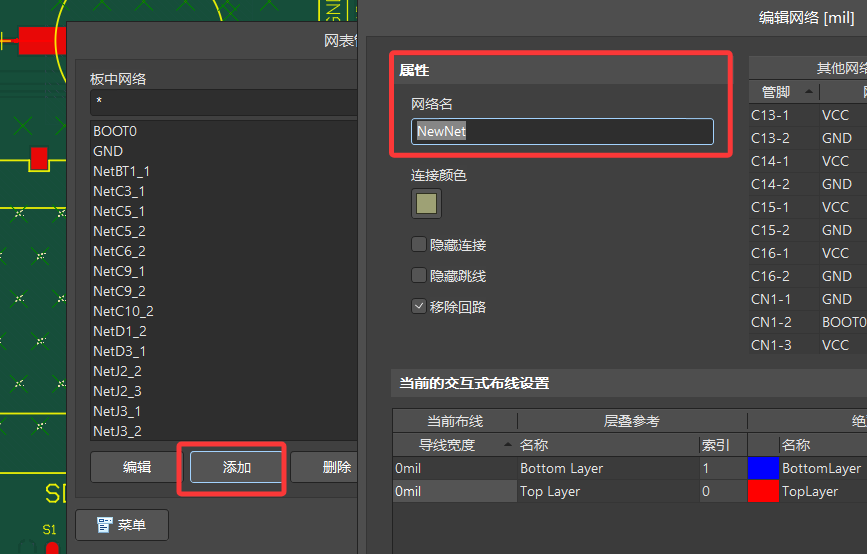

(2)点击添加网络,在弹出的界面输入网络名称

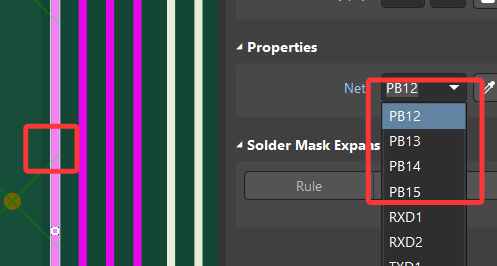

(3)Ctrl+h点击走线,把相关物理连接全部选中,就可以在侧边栏将连接添加至新增网络

2、全部网络的添加(批量自动生成网络)

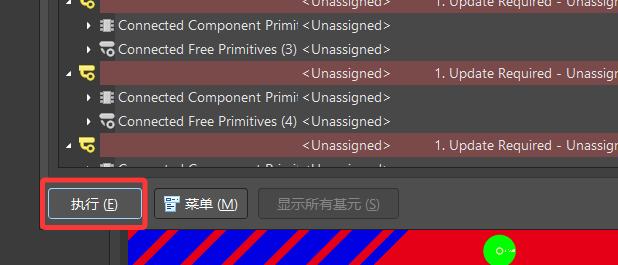

(1)批量生成网络需要先清除所有网络

(2)设置物理网络,点击执行等待网络生成即可(不过自动生成的网络,名称是流水号的形式)

在PCB设计中,网络(Net)是连接元件引脚的电气连接集合,其管理与添加直接影响电路功能与信号完整性。以下从原理图设计到PCB实现的全流程,结合主流工具操作与高级规则展开说明:

一、原理图阶段:网络的创建与管理

1. 基础连接方法

- 导线与总线:使用带电气属性的导线(如Altium的Ctrl+W)或总线连接元件引脚,自动生成网络。总线可简化复杂电路的连接显示,但需配合网络标签明确信号关系。

- 网络标签(Net Label):相同标签的引脚自动归属同一网络,适用于跨页连接或分散布局的元件。例如,在KiCad中通过“放置网络标签”功能分配标签,确保原理图中同名标签的一致性。

- 电源与地符号:直接放置电源/地符号(如GND),工具自动将其关联到对应网络,避免手动连接的繁琐。

2. 网络表生成

- 原理图检查:在Altium中通过“工程验证”(ERC)检查电气规则,如未连接引脚;

- 导出网络表:完成原理图后,生成网络表(如Altium的*.NET文件,KiCad的*.net文件),包含元件封装、网络连接等信息,用于导入PCB设计。

二、PCB阶段:网络的导入与优化

1. 网络表导入与冲突解决

- 导入流程:在PCB设计工具(如Altium的“Import Changes”或KiCad的“加载网表”)中导入网络表,工具自动创建飞线显示网络连接。

- 常见问题排查:

- 封装缺失:原理图元件未分配封装时,PCB中会提示“Unknown Component”,需在原理图中双击元件指定封装(如KiCad的“分配合适的封装”功能)。

- 管脚不匹配:原理图与封装管脚号不一致时,通过修改库文件或手动调整封装管脚号解决。

- 网络表重复导入:部分工具需两次导入以彻底识别错误,首次仅加载,第二次生成报告。

2. 网络可视化与分层管理

- 网络高亮显示:在Altium中选择“Nets”面板,通过“Mask”模式高亮特定网络,方便观察电压分布或信号流向。例如,选中电源网络后,PCB中对应铜箔和过孔会突出显示。

- 网络类(Net Classes):将相关网络分组管理,如将所有电源网络归入“PWR”类,便于统一设置规则(如线宽、间距)。在Altium中通过“设计->类”创建网络类,并批量添加网络。对于多引脚排针,可通过“右键->网络操作->Add selected net to Netclass”快速归类。

三、高级网络管理:规则与策略

1. 差分对处理

- 布线要求:差分信号需等长(误差≤±5mil)、等宽、平行且不换层,以减少共模噪声和时序偏移。例如,USB 2.0数据线需控制差分阻抗为90±10%,线长偏差在±5mil以内。

- 补偿技巧:通过弓形走线补偿短线长度,同时尽量保持平行以维持耦合强度。接收端可并联匹配电阻(如90~130Ω)抵消阻抗不匹配的影响。

2. 电源网络分割

- 内层分割:在Allegro或Altium中,使用“Split Plane”功能分割电源层。例如,将不同电压网络(如DVDD18、DVDD28)分配到独立区域,通过隔离带(如40mil线宽)避免短路。

- 铺铜策略:优先使用正片(Split/Mixed层)进行分割,自动移除独立焊盘并支持走线。铺铜时需设置合适的过孔连接方式(如十字连接或全连接),平衡散热与平面完整性。

3. 设计规则检查(DRC)

- 规则配置:在嘉立创EDA或Altium中设置间距、线宽、过孔尺寸等规则。例如,国内板厂通常支持5mil线宽,故最小线宽可设为6mil以降低成本。

- 实时检测:开启实时DRC功能,在布线过程中即时提示短路、间距不足等问题(如红色“X”标识)。完成设计后,运行全面检查并导出报告,逐项修正错误。

四、工具操作示例

- Altium Designer:

1. 原理图中通过“放置网络标签”定义网络,生成网络表后导入PCB。

2. 在PCB中使用“Nets”面板管理网络,通过“设计->规则”设置DRC规则(如电源网络线宽10~80mil)。

3. 差分对布线时启用“等长模式”,并在规则中定义差分阻抗和间距。

五、常见问题与解决方案

- 网络表导入失败:

- 检查原理图封装是否缺失或管脚号不匹配,通过“工具->封装分配”修正。

- 确认PSMPATH路径设置正确,确保封装库文件(.dra/.psm)可被工具识别。

- DRC报错:

- 间距不足:调整线宽或间距规则,如将All Clearance设为5mil。

- 铺铜冲突:重建铺铜(Shift+B)以更新与其他元素的间距检测。

- 信号完整性问题:

- 差分对时序偏移:通过绕线补偿长度,或在接收端添加匹配电阻。

- 电源平面分割不当:优化隔离带宽度,确保不同网络无电气连接。

通过上述方法,可系统性地管理与添加PCB网络,从原理图到PCB实现高效协同,同时满足电气规则与信号完整性要求。实际操作中需结合具体工具特性,灵活运用网络类、差分规则及DRC检查,确保设计可靠且符合生产规范。

浙公网安备 33010602011771号

浙公网安备 33010602011771号