LVDS

LVDS

背景

通信系统中最基本的部分是传输介质。这也是信号最容易受到干扰、失真和衰减的地方。在一些对屏蔽性能和连接器要求较高的关键应用中,传输介质可能会变得非常笨重且昂贵。在这种情况下,电磁干扰(EMI)是主要的问题来源,它可能会将信号质量降低到导致系统故障的程度。此外,为了获得监管机构的市场认证,设备的电磁兼容性(EMC)也必须符合相关标准。

为了解决这些问题,人们开发了低压差分信号传输标准(LVDS)。该标准利用差分信号线提供良好的电磁干扰抑制能力,并且兼容低压工艺技术。

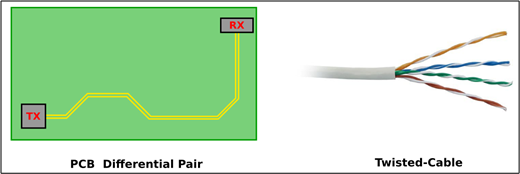

LVDS的主要传输介质:PCB差分线和双绞线。

LVDS基本概念

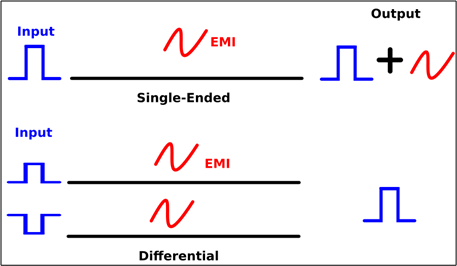

LVDS 的工作原理很简单:电磁干扰(EMI)是在空气中传播的,因此信号的幅度会随着位置的不同而变化。这意味着两根导线之间的距离越近,它们所受到的干扰就越相似。因此,在双绞线配置中(如下图所示),每根导线上耦合的电磁干扰基本上是一样的,因此导线之间的电压差几乎为零。这使得双绞线的差分电压比单端信号更不容易受到电磁干扰的影响。在 LVDS 中,使用差分信号来传输信息,而电磁干扰则被作为共模噪声被抑制掉。

为了避免混淆,LVDS 并不是一种通信协议。它是一种技术标准,规定了信号应该如何传输,而任何协议都可以将此标准作为其底层技术基础。

LVDS 标准规定,信号应通过一对差分线进行传输,并且该差分对中的每条线路都应具有相同幅度但极性相反的电压。例如,如果传输的是 1V 的差分信号,则其中一条线上的电压为 +0.5V,另一条线上的电压则为 -0.5V(此时共模电压为零)。

因此,发送端必须具有两个完全相同的输出端来驱动这对差分信号,而接收端则应在第一级对这两个信号执行减法运算,以恢复原始的差分信号。

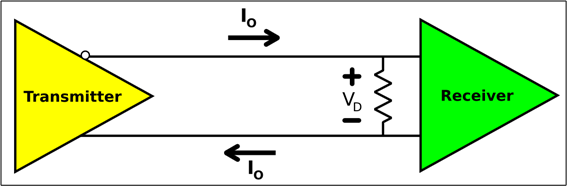

在典型的高速应用中,通常使用差分电流而不是电压:每对差分线会传输相同的电流(通常是同一个电流从发送端流出并流回发送端),该电流在接收端产生一个差分电压。

这种方法不仅提升了性能,因为电流信号更不容易受到损耗和干扰的影响,而且还减少了电磁辐射,因为正向电流产生的磁场会被反向电流的磁场所抵消。

LVDS元件

与任何通信系统一样,LVDS 的基本组成部分包括发送端(Transmitter)、接收端(Receiver)和传输线(Transmission Line)。

发送端负责向差分对中注入电流。该电流从一条线路流出,并从另一条线路流回发送端,电流的极性决定了逻辑电平。

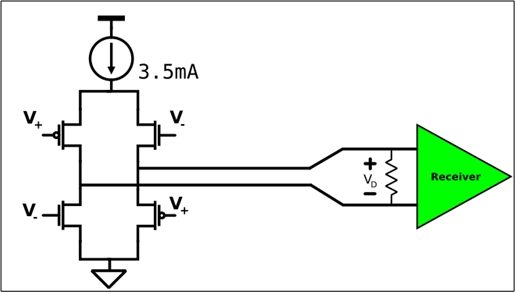

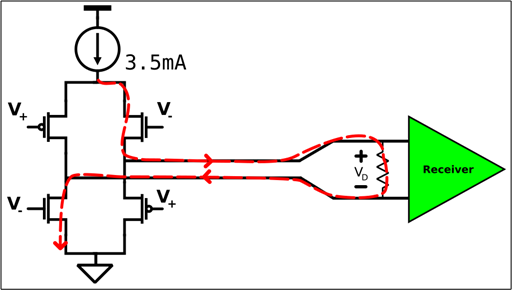

发送端由一个恒定电流源(典型值为 3.5 mA)和四个 MOSFET 开关组成,这四个开关构成一个 H 桥结构,如下图所示。

一条线路的上开关与另一条线路的下开关共用同一个控制信号,因此它们会同时导通或关断。同一线路中的两个开关则由互补的控制信号驱动,这样就可以控制流经差分对的电流方向(即极性)。

电流随后流经差分传输线,差分线可以通过双绞铜线或PCB上的差分走线来实现。

接收端,电流流过一个终端电阻。该电阻的阻值通常为100Ω左右,应与传输线的特性阻抗匹配,以避免在高频下产生信号反射。当电流流经该电阻时,在接收器的两个输入端之间会产生一个电压降。接收器随后对这两个电压进行差分运算,得到差分电压值。

如果使用3.5mA的驱动电流和100Ω的终端电阻,那么产生的电压差仅为350mV,这使得LVDS适用于非常低电压的应用场景。LVDS信号线的共模电压通常约为1.2V,但在一些低压应用中,共模电压甚至可以低至400mV。此外,LVDS标准允许发送端与接收端之间的地电位偏移达到±1V。这种地偏移加上发送端的共模电压以及传输线上的共模噪声,最终会在接收端形成所需的共模电压范围。

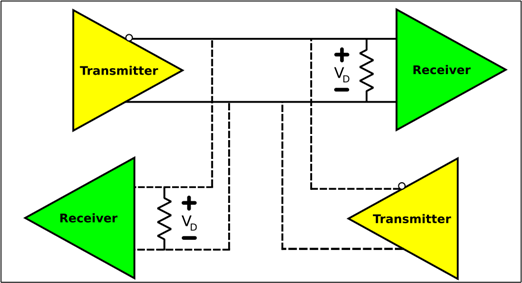

双向通信也可以实现,方法是为每个方向的接收端各配置一个终端电阻。当然,每次只能使用一个传输方向,也就是说当一个设备发送信号时,另一个设备必须保持静默状态。这种方法的主要缺点是,从发送端看去,这些电阻是并联的,这会降低电压降,从而减小噪声容限。

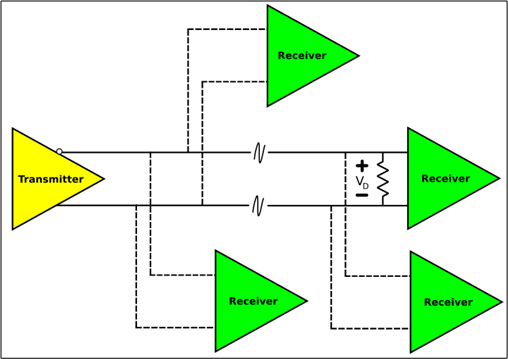

此外,还可以实现多点LVDS(也称为LVDS总线),在这种结构中,多个不同的接收器可以从同一条总线上读取数据。设计这类电路时需要特别小心,因为发送端必须能够驱动多个终端电阻。

LVDS总线

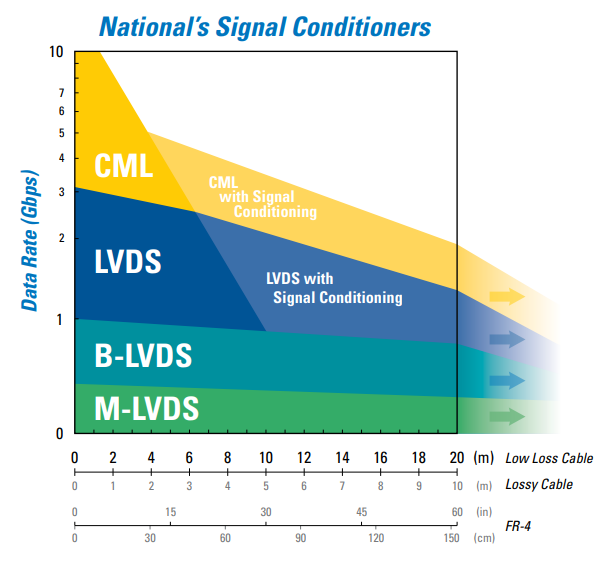

广义的LVDS总线分很多类型。针对实际应用的需求,不同的总线可以承载不同大小的数据流。在350mV的典型信号振幅下,LVDS总线只会消耗非常少量的能量,而与此相对的,LVDS总线的数据传输速率可以达到相当可观的3.125 Gbps。如下图,展示了LVDS总线的传输速率和总线长度的关系。

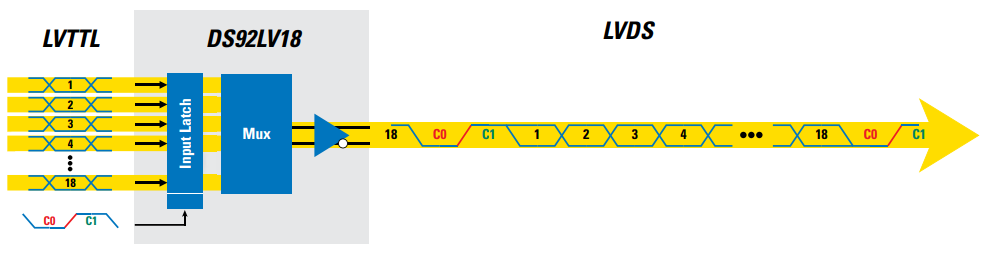

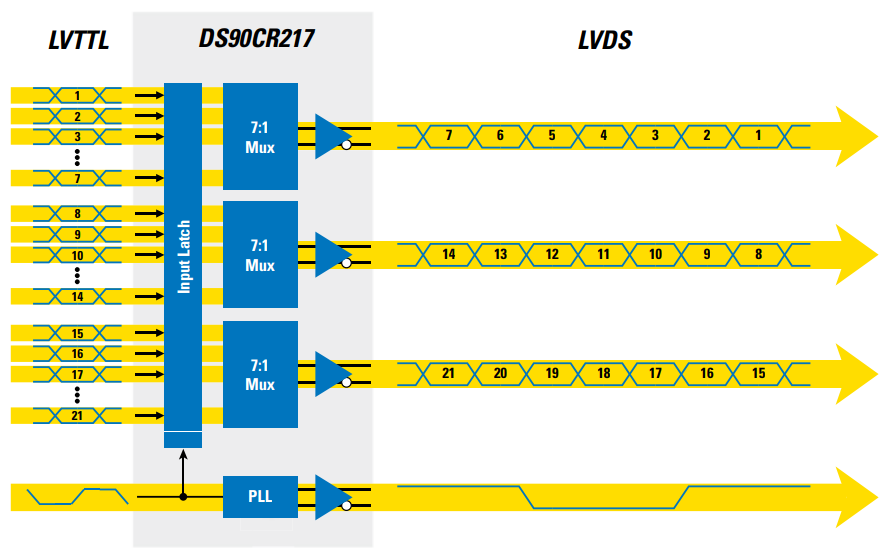

LVDS总线的一大特点就是,当一对差分信号无法提供充足的数据带宽时,可以增加同时工作的差分信号对,以并行的思路传输信号。如下两图所示,LVDS可以是根据场合选择相应的通道数和编码方式的,使用起来非常自由。这同时也造成实际设计中必须协商好LVDS上的上层协议,才能正确传达信息。

浙公网安备 33010602011771号

浙公网安备 33010602011771号