ChipScope——ISE软件的抓波形操作

Quartus II 下抓波形为 SignalTap,Vivado 下为 ila,而 ISE 下则为 ChipScope。目前 ISE 已经停止更新了,不再支持 Xilinx 的新芯片,但有些老的工程还是要用到 ISE 来开发维护,固在此以串口通信的工程为背景,记录一下 ChipScope 的使用过程。

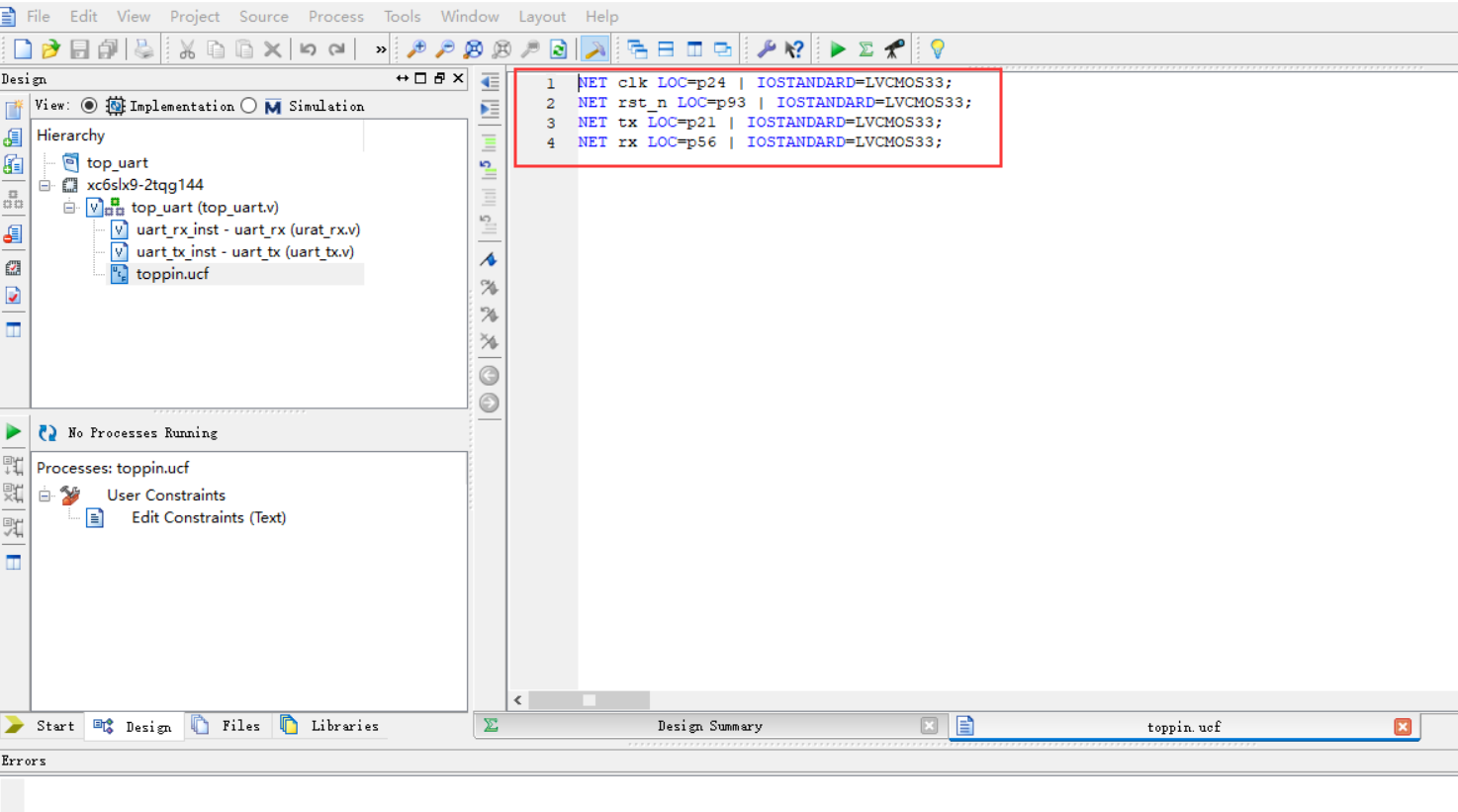

1、新建管脚约束文件

Next,Finish。

2、分配管脚

即完善“toppin.ucf”文件的内容。

可以复制粘贴到此处。也可以通过视频中的方法和步骤,查看net16文件中的pdf文档,查看管脚分配图。保存。

3、板子上电

查看计算机是否安装这个驱动:

我的电脑——属性——设备管理器——端口下的“Prolific USB-to-Serial Comm Port”这个串口的驱动。(文件net16_uart\tools\pl2303里,有Setup 32.64.exe串口的驱动程序,以管理员身份运行,一路next,install,finish即可,非常简单快捷。)

安装成功后,扫描一下(设备管理器——操作——扫描检测硬件改动;端口下的“Prolific USB-to-Serial Comm Port”,右键,扫描检测硬件改动。现在,此处前面就不再显示感叹号了,说明已经加载成功了,就可以使用串口了。)

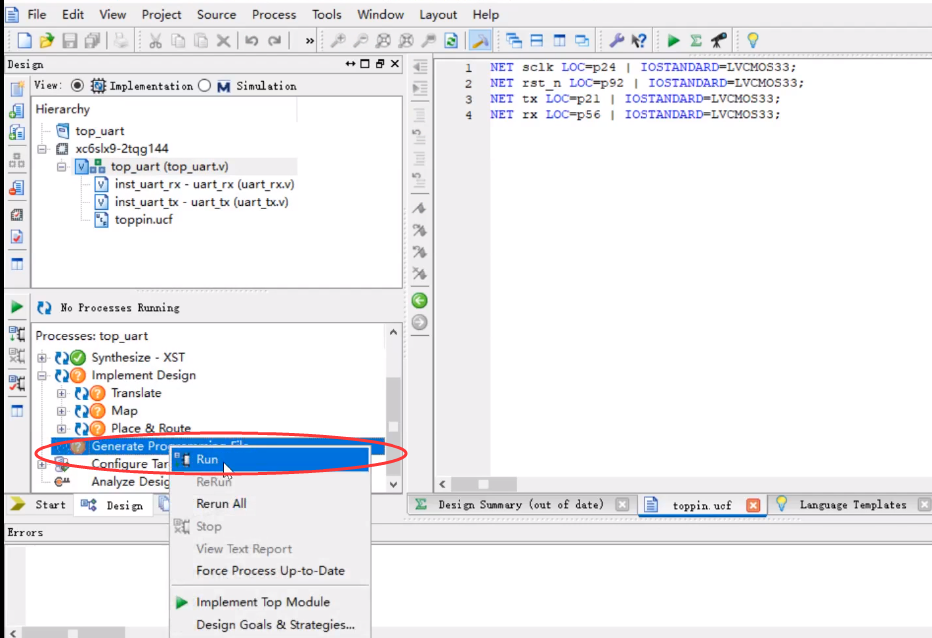

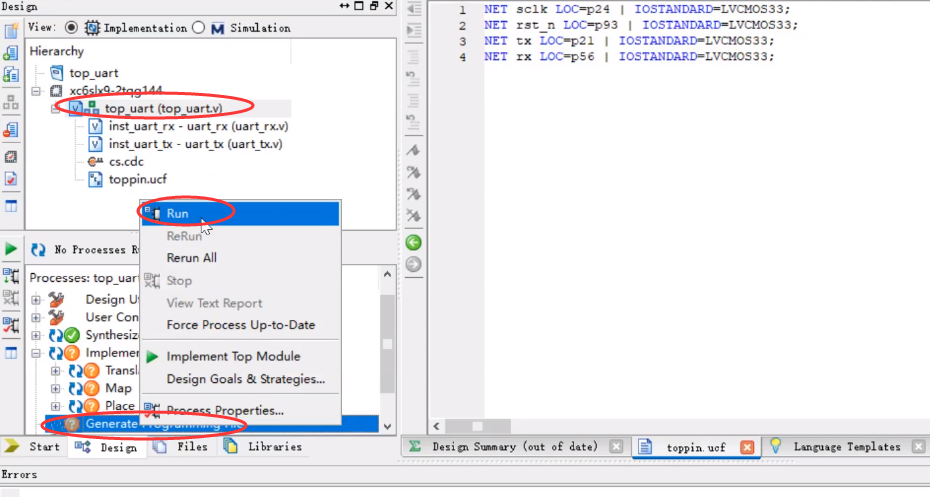

4、编译综合

等待编译成bit文件。

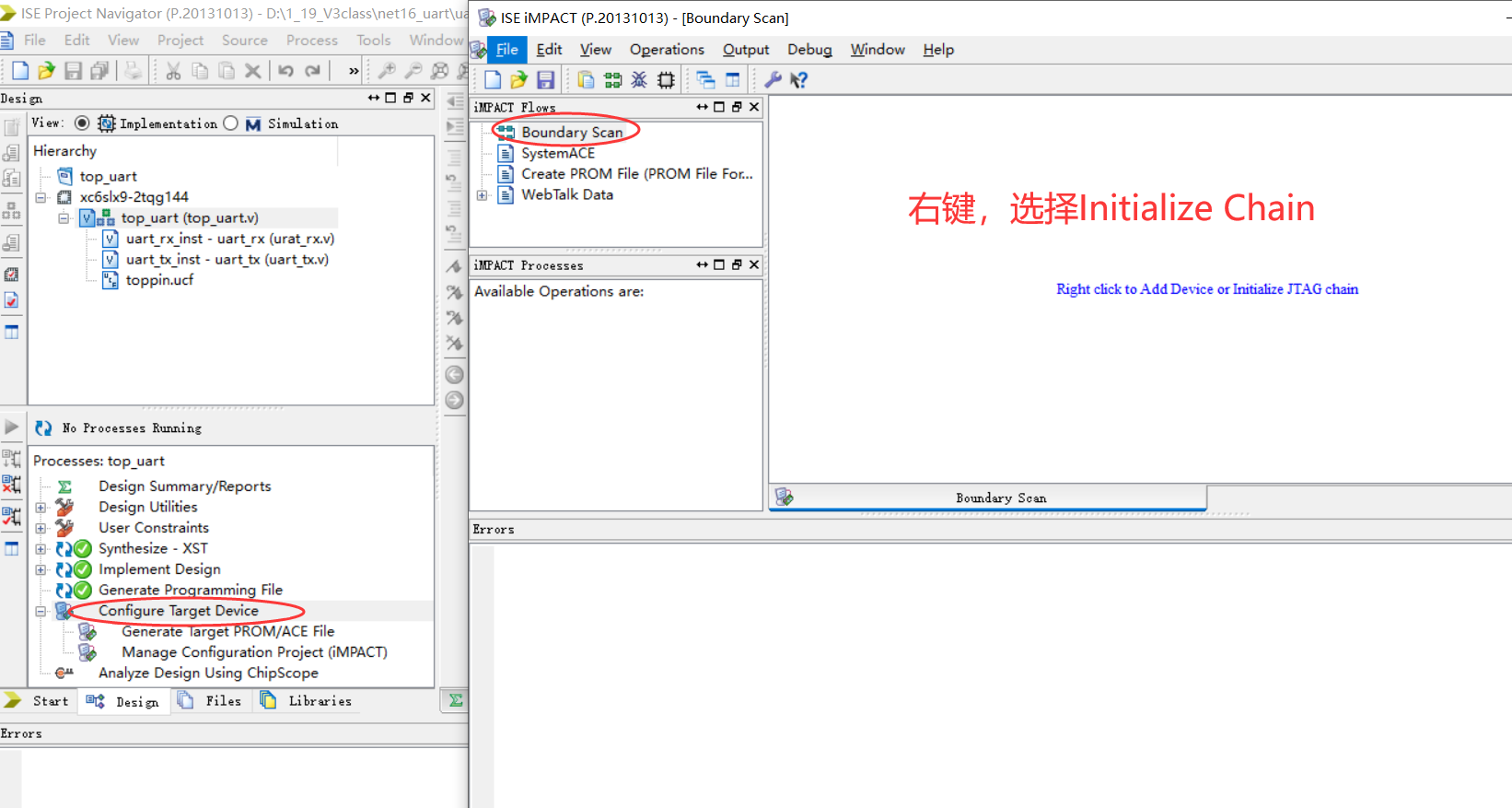

5、下载

双击“Configure Target Device”打开下载的工具(OK)

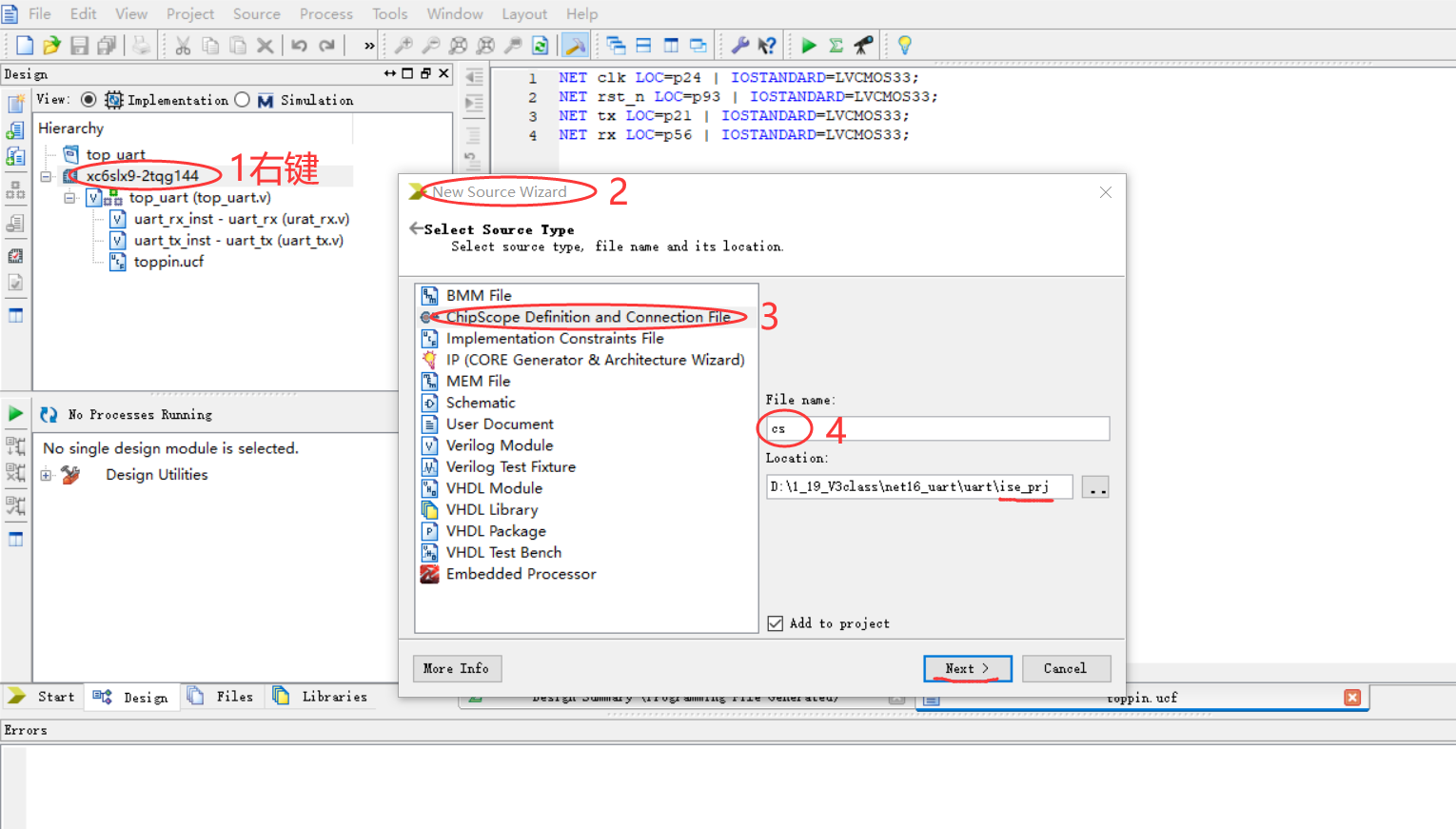

6、ChipScope在线逻辑分析仪

Next,Finish。

7、添加信号

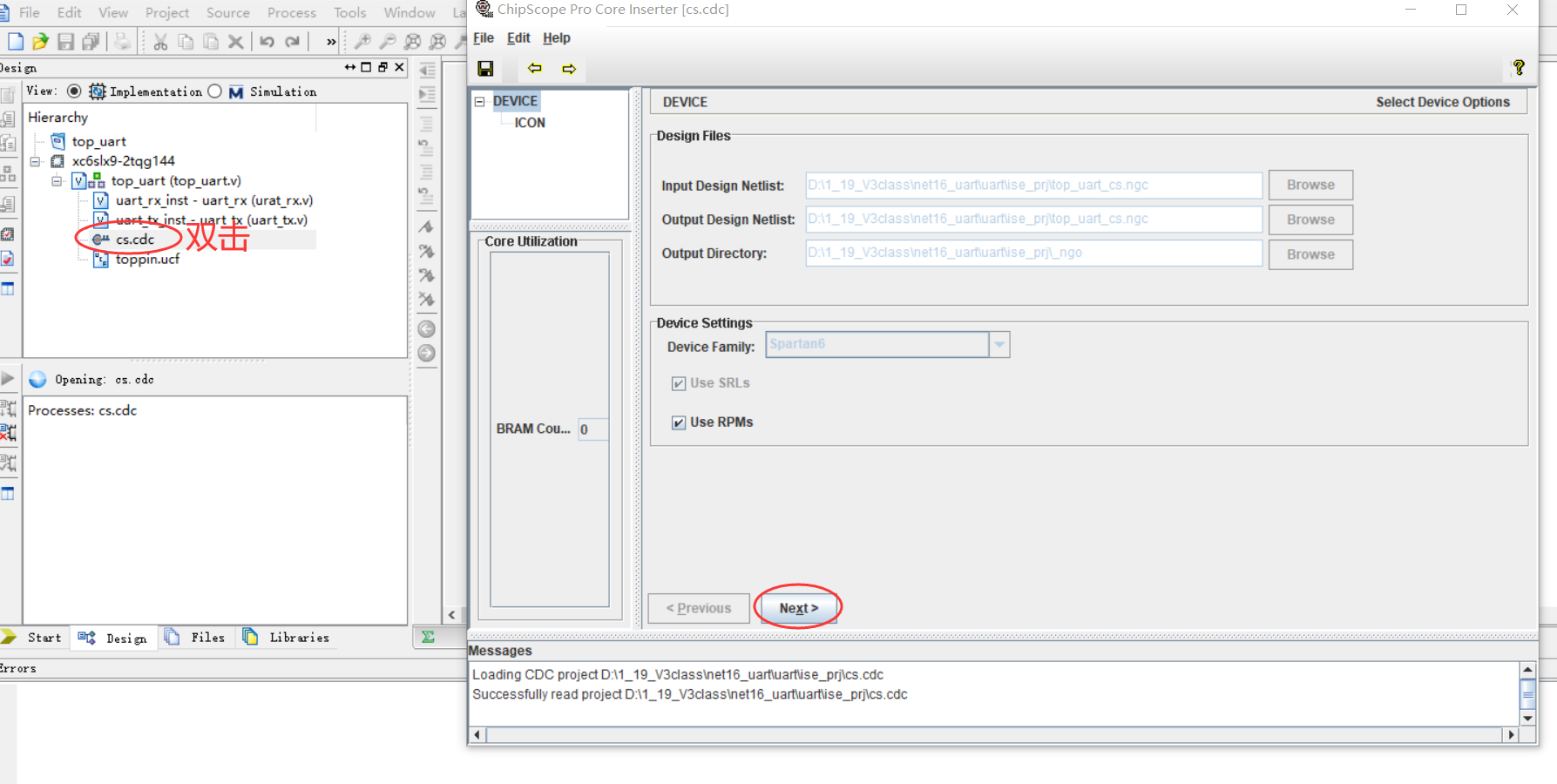

打开cs.cdc文件,把想看的信号加进来

第1-2页:Next,Next,

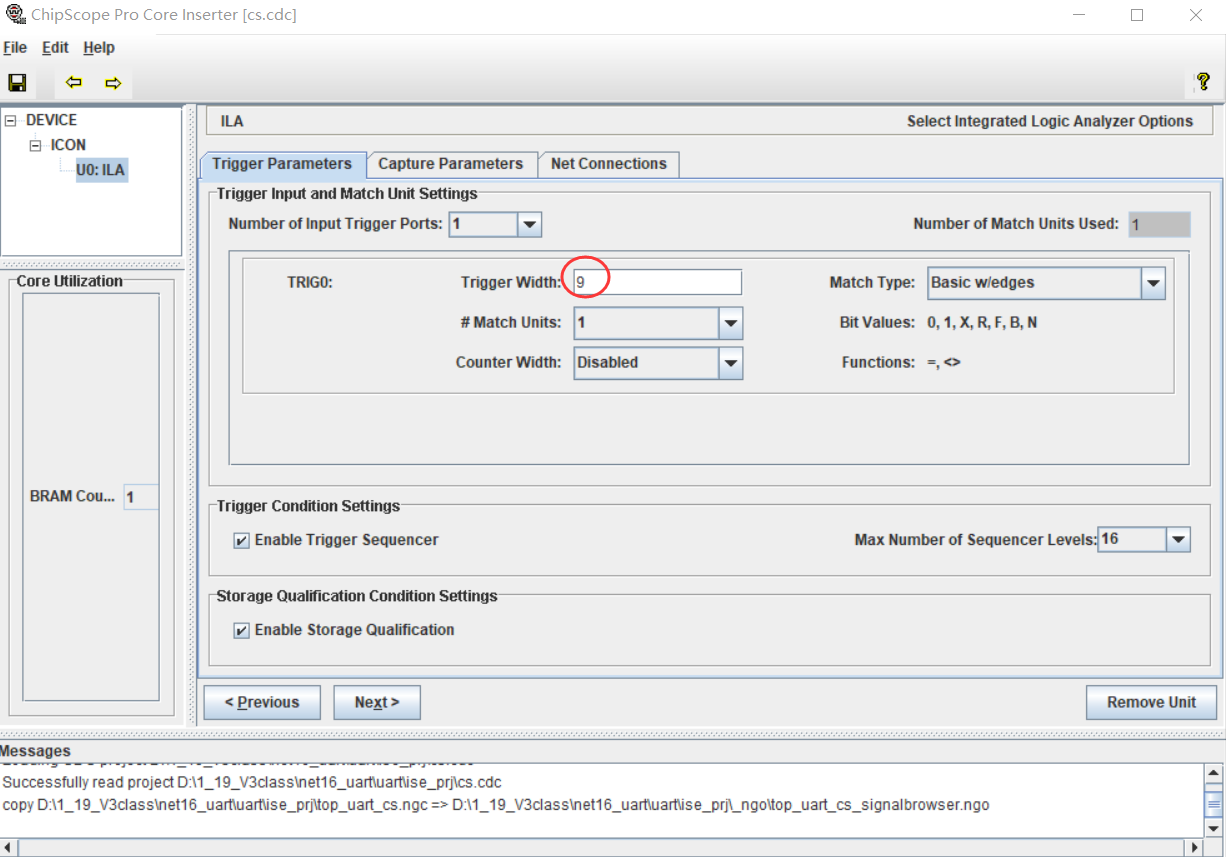

第3页:想看的信号总的位宽:输入9;Next。

(数据p_data和P_falg一共9位的位宽,所以 ,如下图所示。)

第4页:NEXT。

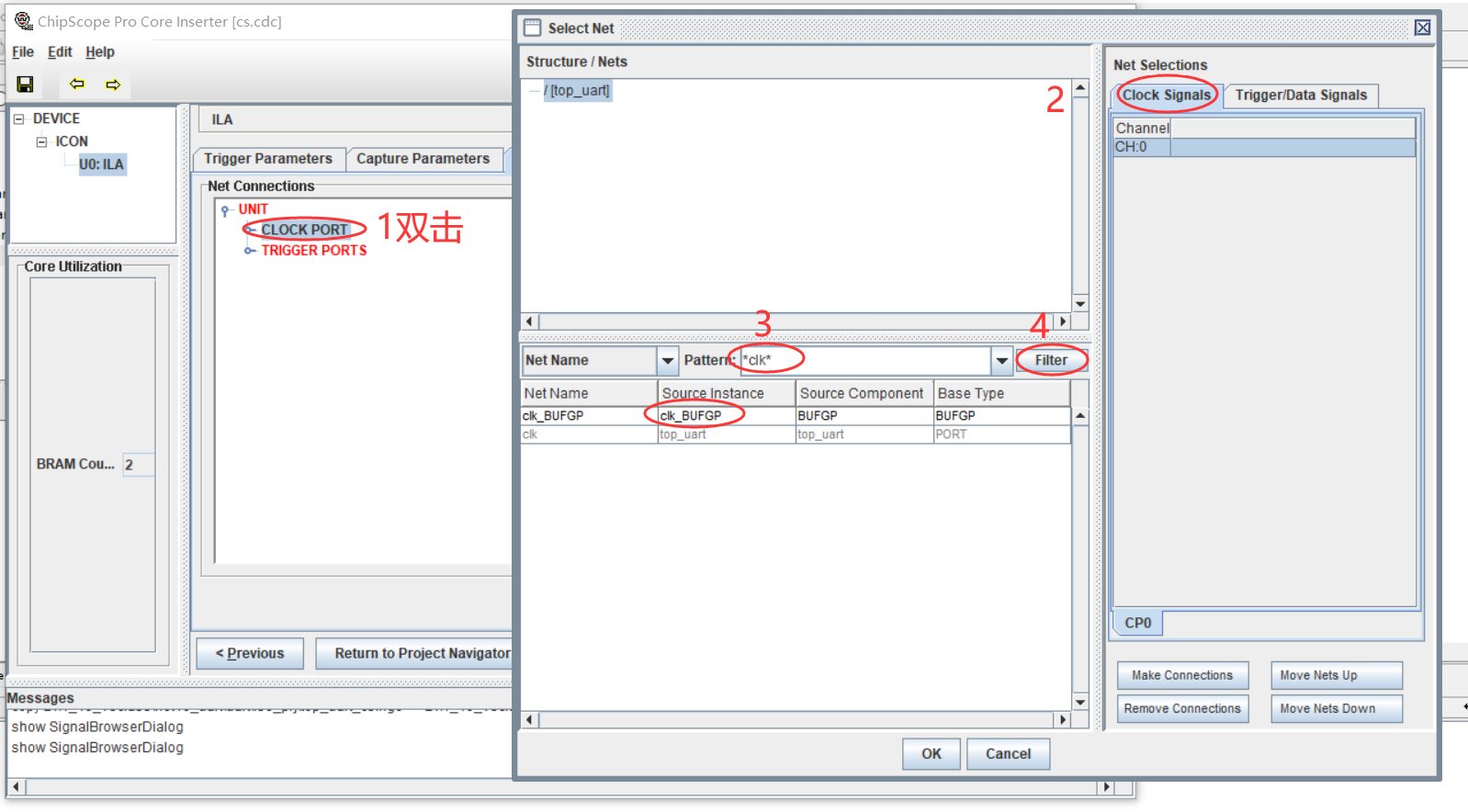

第5页:双击clock_port,输入:*clk*,fitter,选择表中的clk,make connection。切换到Trigger Signals,可展开看到CH0~CH8。

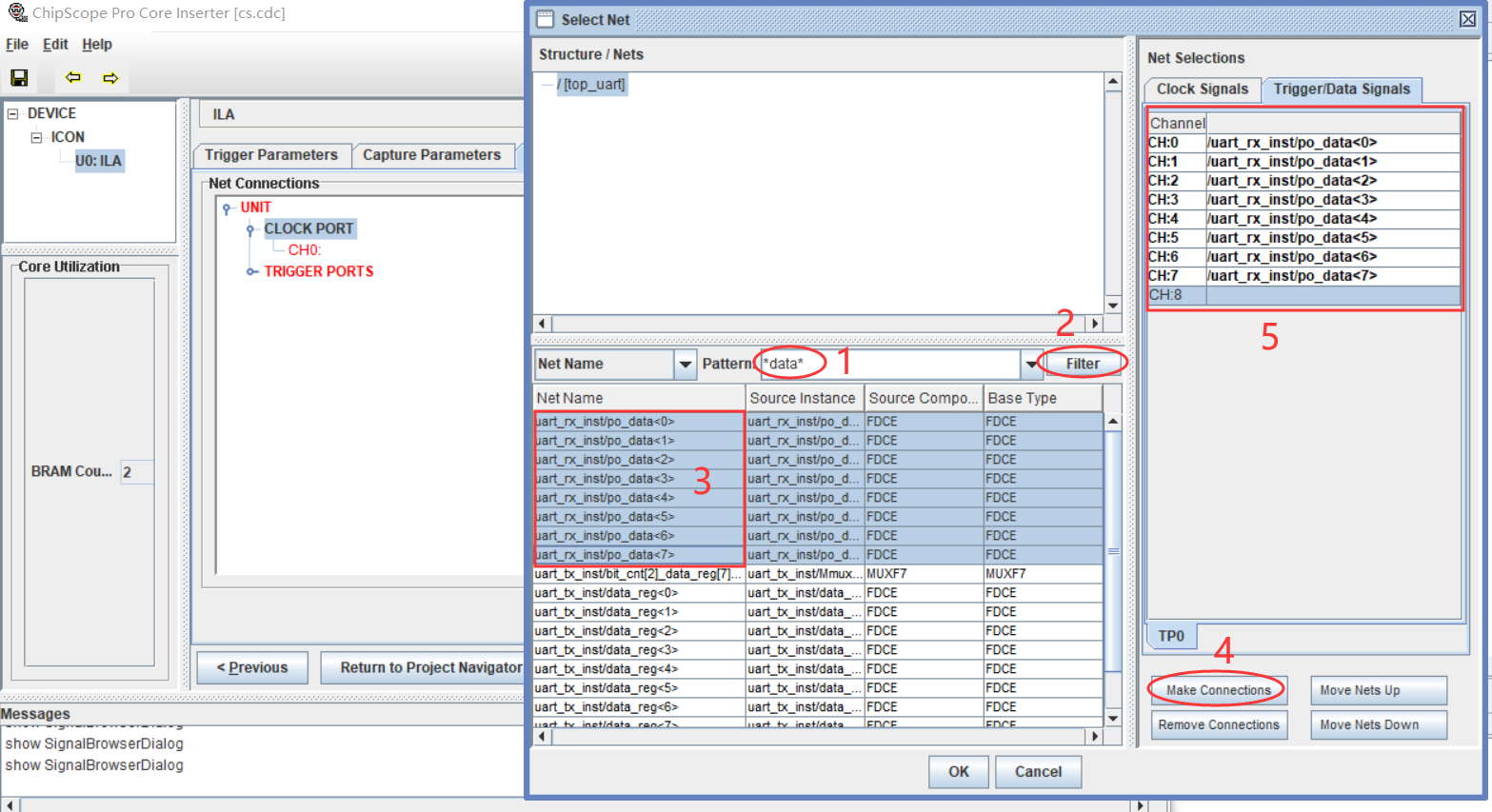

在“3”处,选中“data<0>”,按住shift键,选中“data<7>”,就选中了data0-7。点击“4”处,即可显示“5”处。

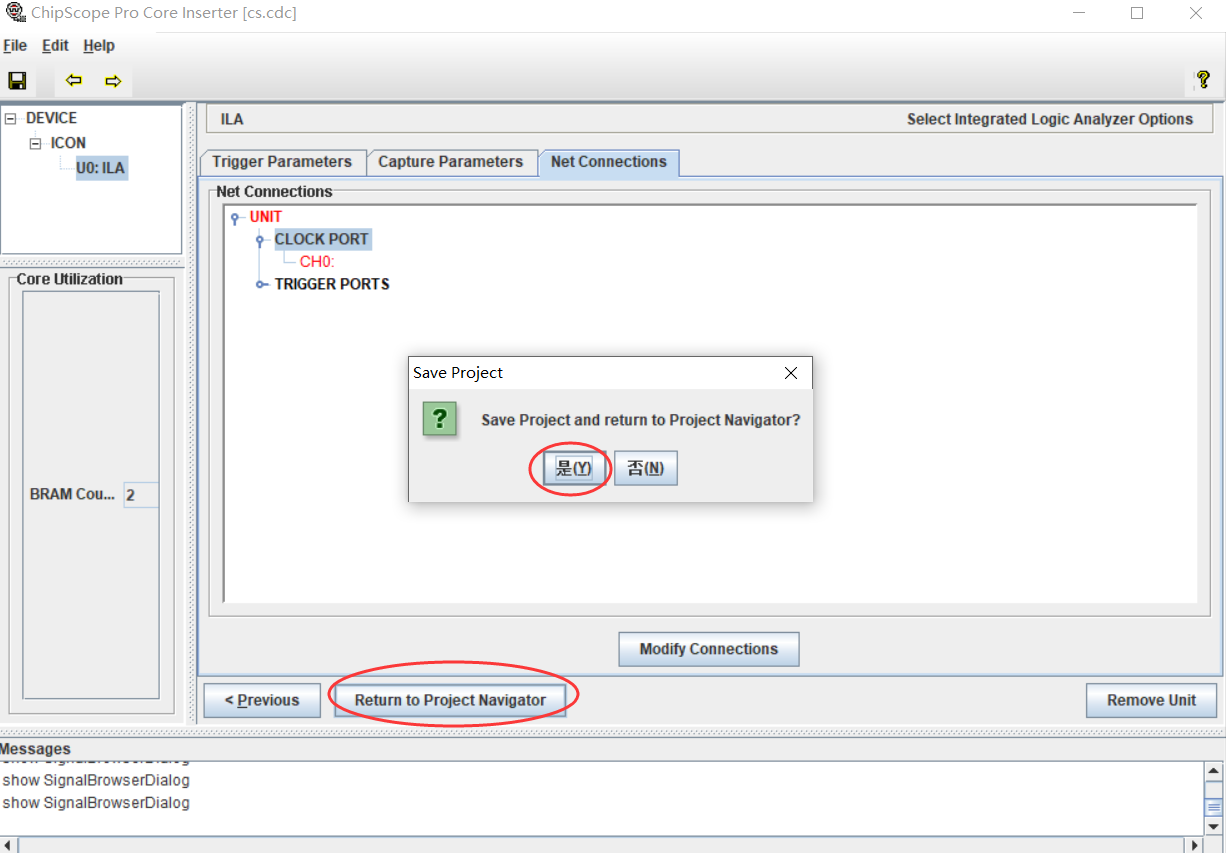

点击“Make Connection”,可见CH:8一行仍是空的,选中,在“1”处输入“flag”,选中“po_flag”,OK。Return to Project Navigator,是(yes)。

等待编译完成

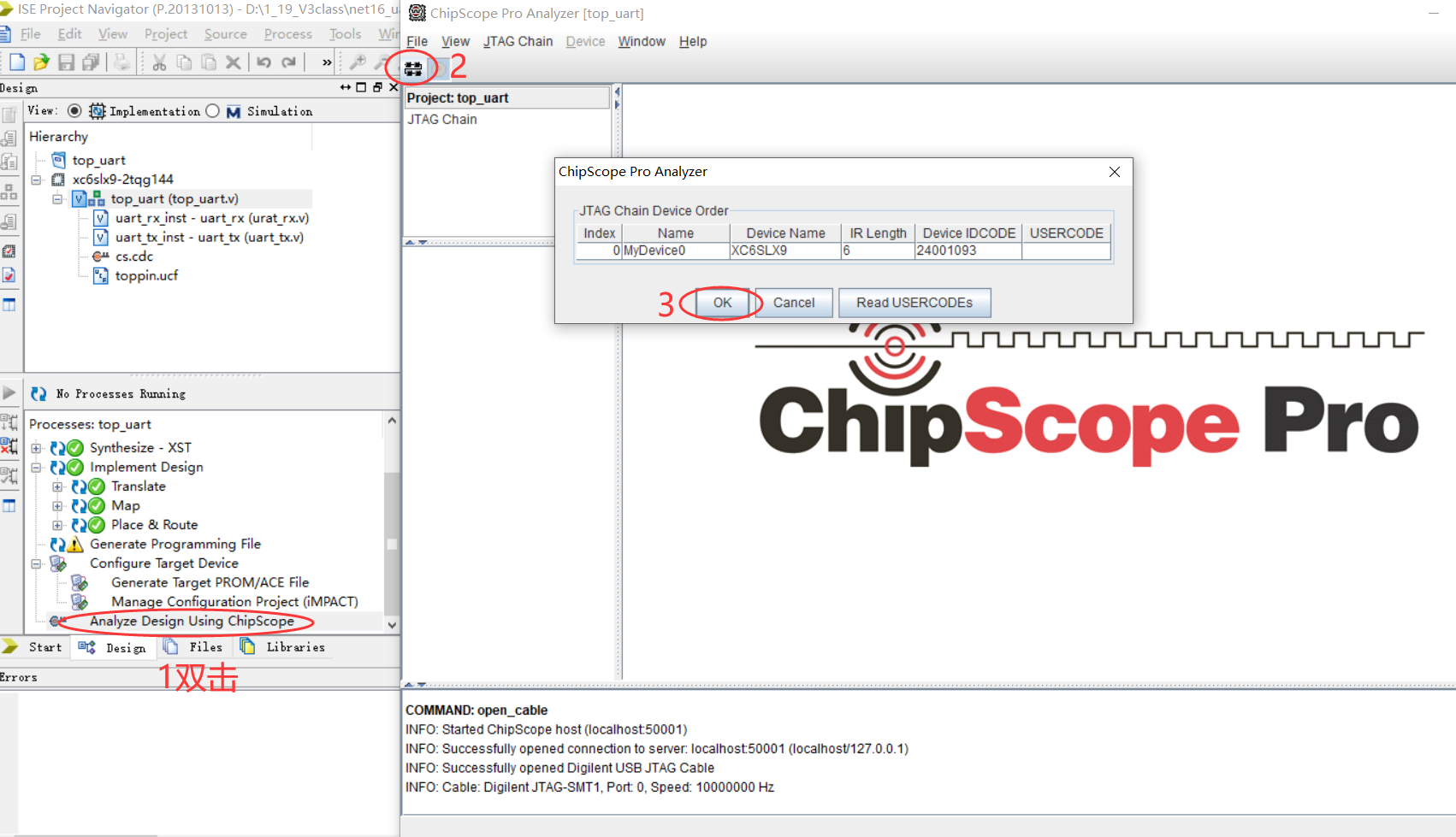

8、上板查看波形

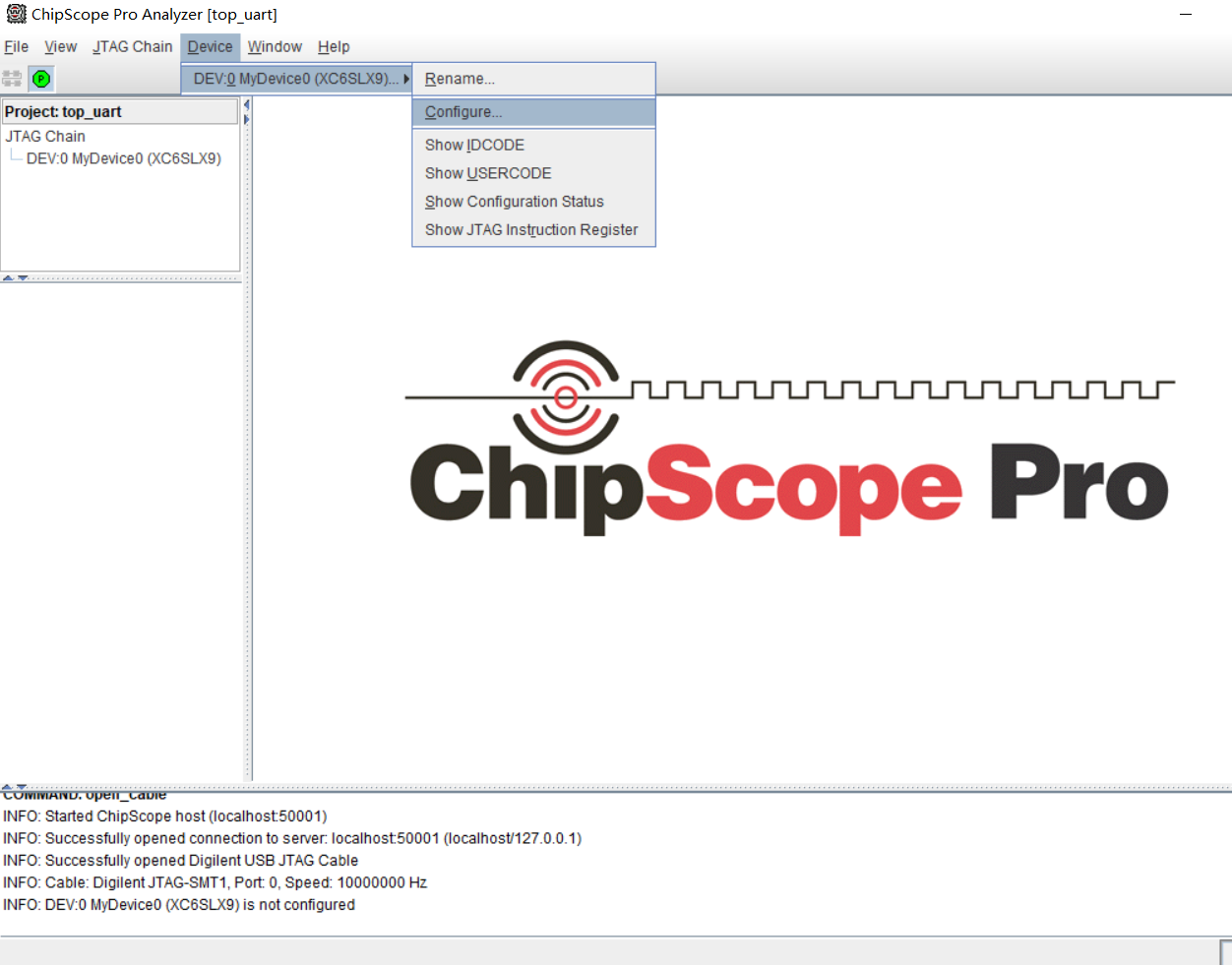

Device——My Device——Configure,OK。

Configure,刷新一下,这样,bit文件就download到板卡里去了。

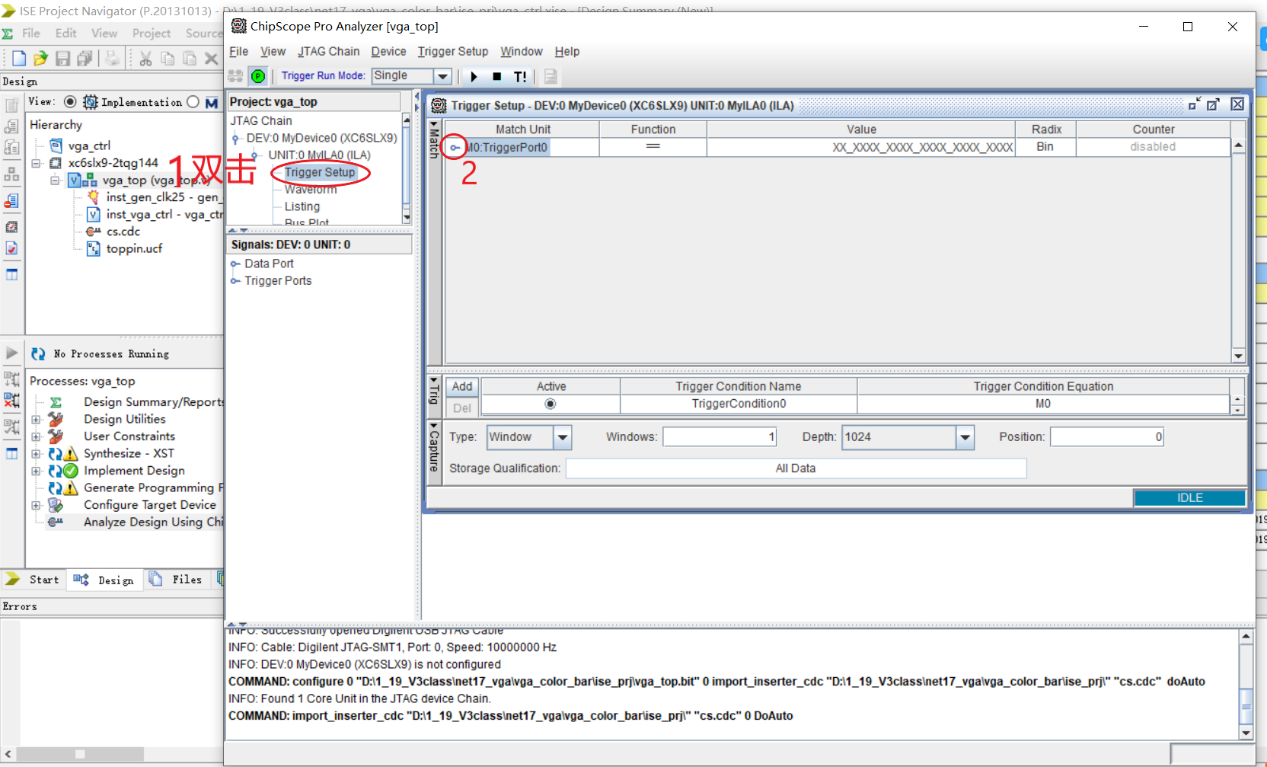

设置触发条件:

我们可以设置一个触发条件,

1.选中vsync, 2.改为R, 3.position设置为100, 4.△(ok)

我们可以设置触发条件为:场同步vsync的上升沿。Vsync是第21位,也就是最高位,R是上升沿,F是下降沿。

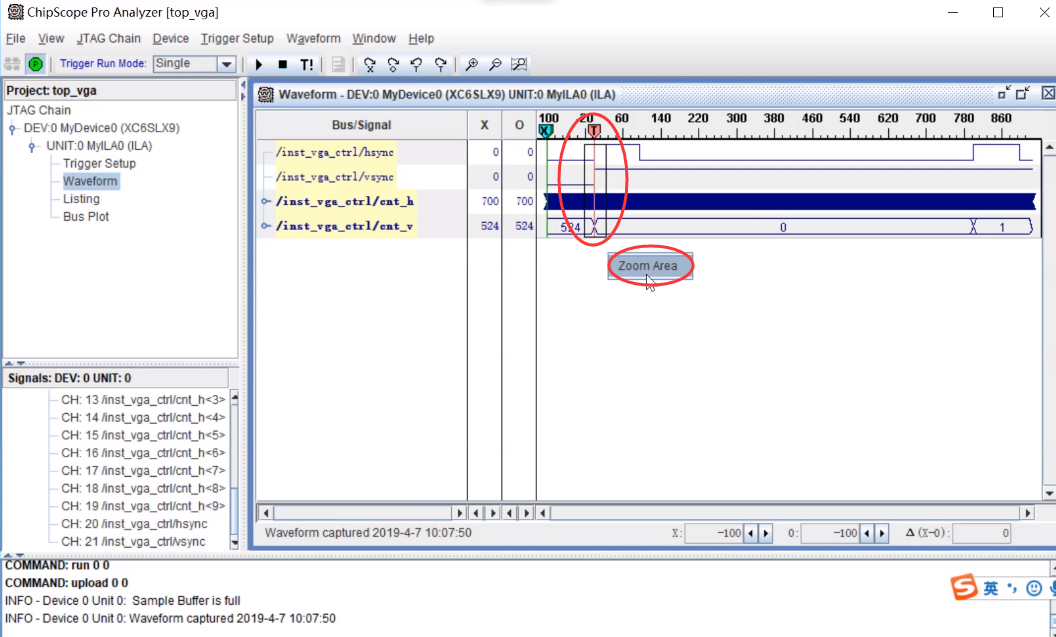

可见,Simple Buffer is full,说明采样到了。

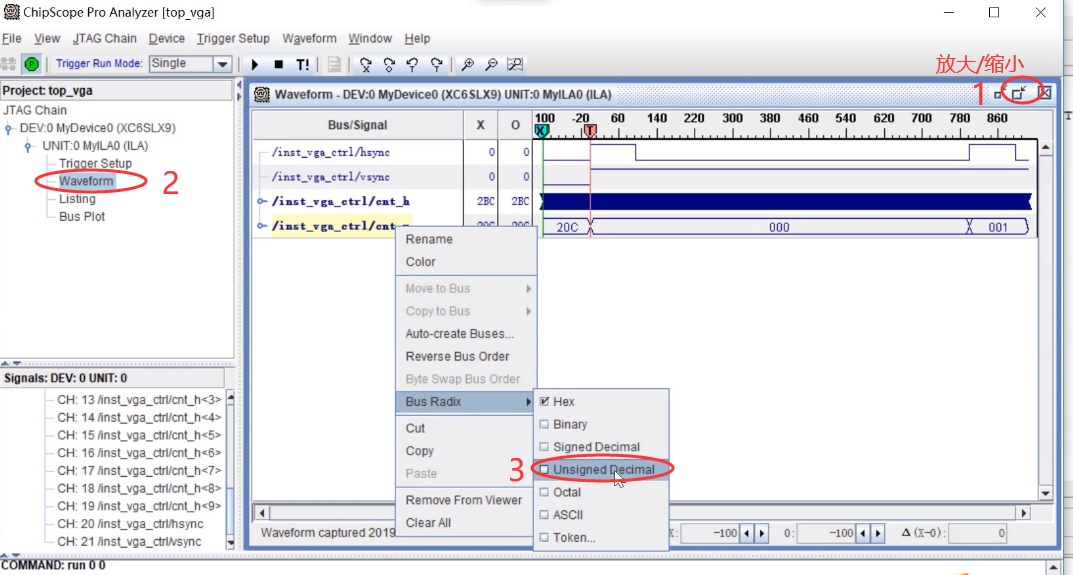

放大波形:

用鼠标画一个矩形,如图;点击Zoom Area。

9、上板实际现象

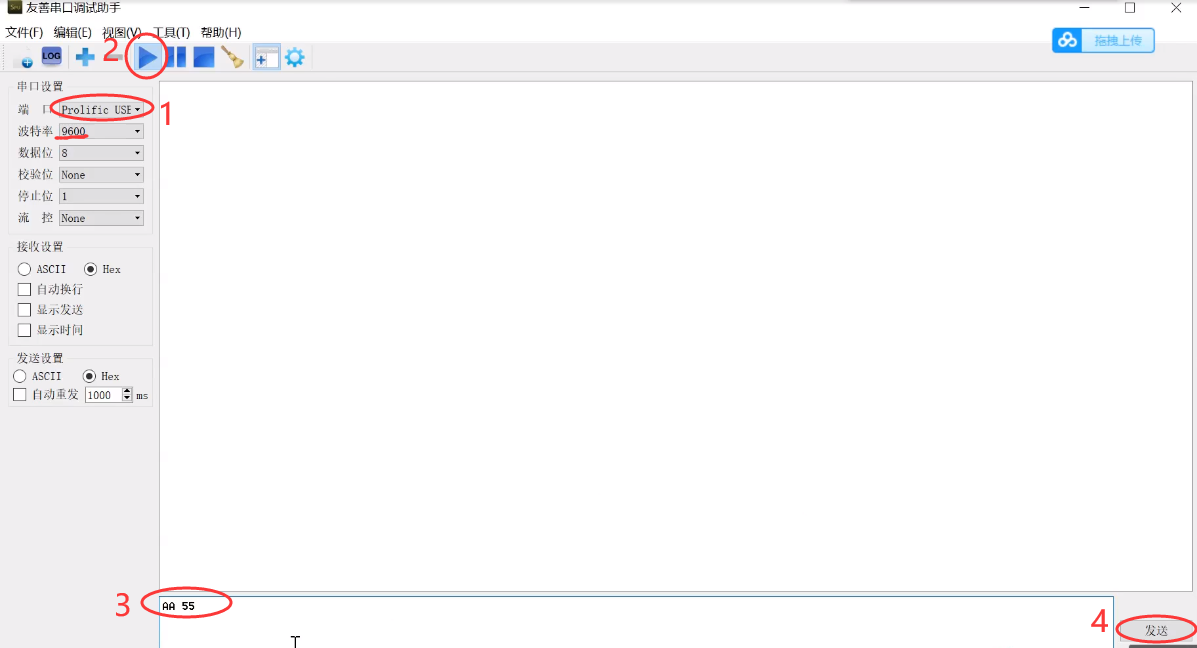

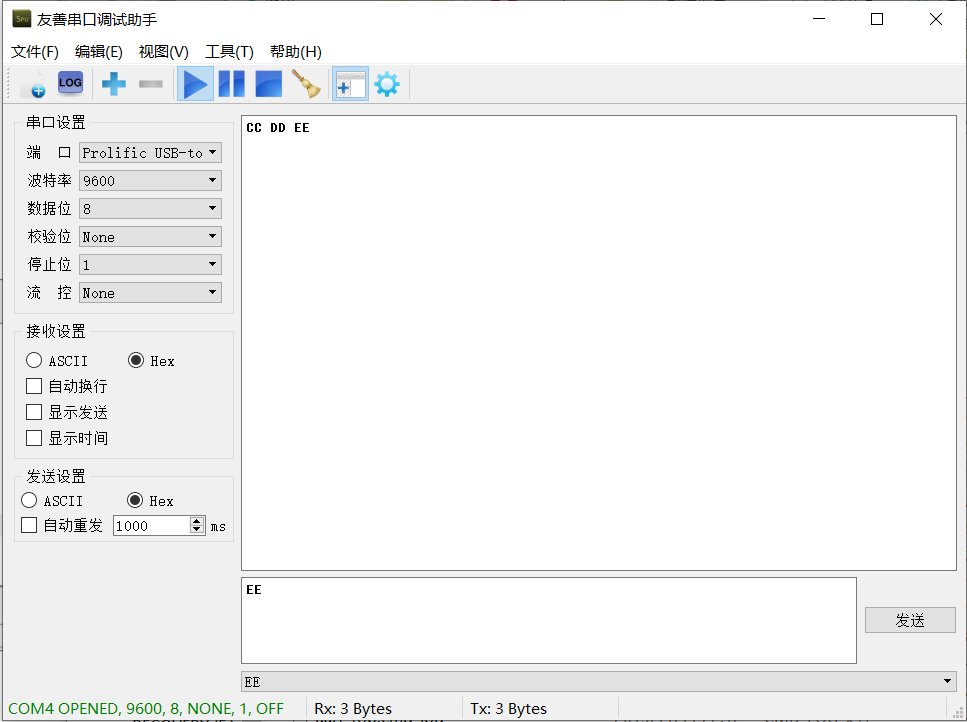

打开串口调试助手,

1.端口选择Pro…开头的 2.开始 3.输入 4.发送

发送CC,然后发送DD,最后发送 EE,结果如下:

参考资料:

[1] V3学院FPGA教程

[2] 蔡同学整理笔记

浙公网安备 33010602011771号

浙公网安备 33010602011771号