一文讲透芯片设计全流程:从想法到流片的完整旅程

微信视频号:sph0RgSyDYV47z6

快手号:4874645212

抖音号:dy0so323fq2w

小红书号:95619019828

B站1:UID:3546863642871878

B站2:UID: 3546955410049087

芯片是怎么“造”出来的?

在上一篇文章中,我们初步了解了什么是芯片、芯片的分类以及IC设计的基本概念。本文更深入一步,完整拆解一颗数字芯片的设计流程。

你是否好奇,那些动辄几十亿晶体管的芯片,究竟是如何从一个想法一步步变成真实可运行的硅片?这背后是一套高度系统化、环环相扣的工程流程,涉及成百上千名工程师的协作,以及海量EDA工具的支持。

芯片分为数字芯片、模拟芯片、数模混合芯片等多种类别。不同类别的设计流程也存在一些差异。

本文将以数字芯片为例,带你走完从“灵光一闪”到“交付制造”的全过程。无论你是初学者,还是对芯片行业感兴趣的非技术背景读者,相信都能从中获得清晰的认知。

添加图片注释,不超过 140 字(可选)

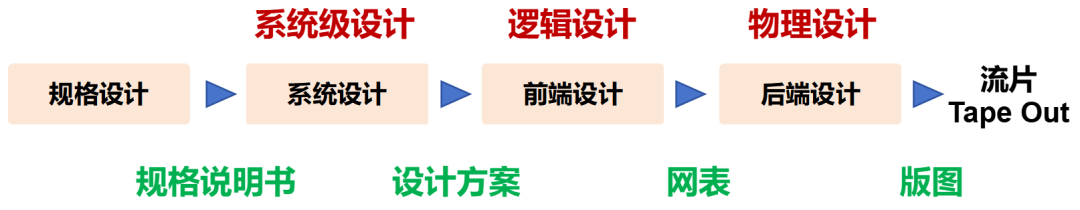

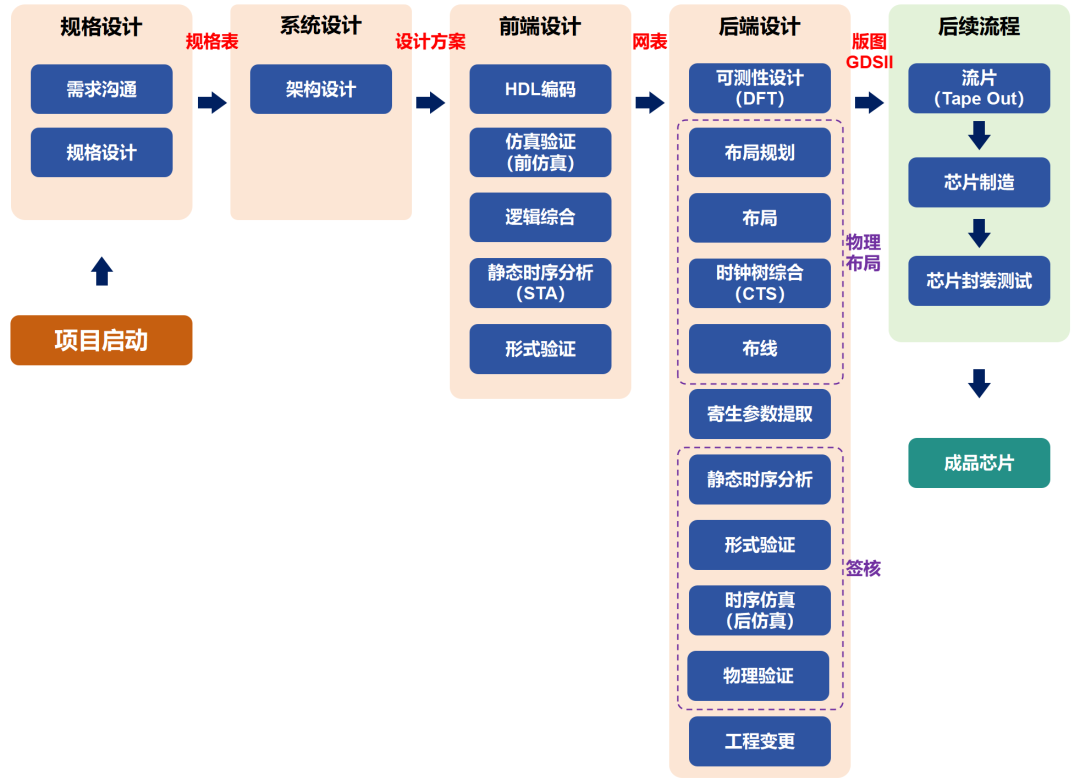

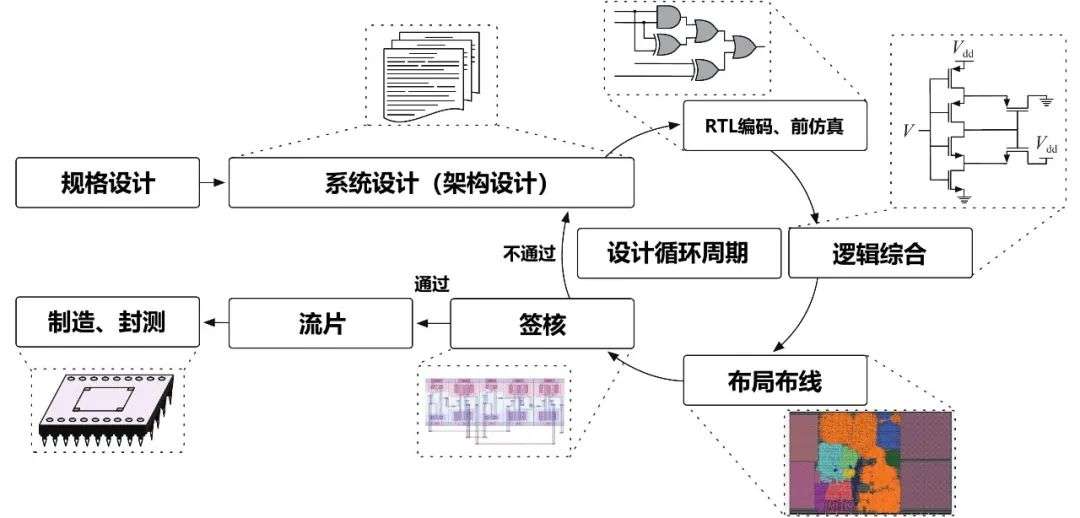

█ 芯片设计的整体框架

现代芯片设计遵循“自顶向下(Top-Down)”的设计哲学:先定义宏观目标,再逐层细化实现路径。

添加图片注释,不超过 140 字(可选)

整个流程大致可分为四大阶段:

-

规格定义(Specification)

-

系统架构设计(Architecture Design)

-

前端设计(Front-End Design)

-

后端设计(Back-End Design) 注:部分资料会将前两个阶段合并为“系统级设计”,或统称为“前端”。但为清晰起见,我们在此将其分开阐述。

这四个阶段并非线性推进,而是反复迭代、持续验证的过程。每一步都必须通过严格的仿真与检查,才能进入下一环节——因为一旦流片失败,代价可能是数千万甚至上亿美元。

添加图片注释,不超过 140 字(可选)

参考文章数字IC设计 | 入门到放弃指南

下面我们逐层展开。

█ 第一阶段:规格定义 —— 先问“做什么”,再谈“怎么做”

任何伟大的工程,都始于一个明确的目标。

芯片设计的第一步,不是写代码,也不是画电路图,而是搞清楚这颗芯片到底要解决什么问题。

这个过程需要多方协作:产品经理、客户代表、市场团队、应用工程师、研发主管等共同参与。他们要回答一系列关键问题:

-

这颗芯片用在哪儿?手机?服务器?汽车?IoT设备?

-

主要功能是什么?CPU?GPU?AI加速器?通信基带?

-

性能指标是多少?算力(TOPS)、主频(GHz)、延迟(ns)?

-

功耗预算多少?峰值功耗?待机功耗?

-

成本控制在哪一档?封装形式?是否支持国产工艺?

-

是否需要满足特定安全标准?如车规级(AEC-Q100)、工业级?

所有这些需求最终会被整理成一份正式文档——Spec(Specifications,规格说明书)。

这份文件就是整个项目的技术宪法,后续所有设计决策都要围绕它展开。如果后期发现Spec有误,轻则返工,重则项目终止。

✅ 关键产出:芯片规格说明书(Spec)

█ 第二阶段:系统架构设计 —— 搭建“骨架”与“蓝图”

有了明确目标后,接下来就是由架构师出马,绘制芯片的“作战地图”。

架构设计的核心任务是:如何用最优方式实现Spec中定义的功能和性能目标。

具体工作包括:

-

整体架构选型 是采用冯·诺依曼架构?还是哈佛架构?是否引入多核、异构计算(CPU+GPU+NPU)?是否使用片上网络(NoC)?

-

模块划分与接口定义 将复杂系统拆分为若干功能模块(如ALU、Cache、DMA、Memory Controller等),并明确各模块之间的通信协议(AXI、AHB、APB等)。

-

性能建模与资源分配 预估数据通路带宽、内存访问频率、缓存命中率等,确保瓶颈不集中在某一处。

-

软硬件协同设计 哪些功能由硬件实现(速度快、功耗低)?哪些交给软件处理(灵活、易升级)?

-

IP核选型与集成策略 是否复用已有的成熟IP?比如ARM Cortex系列CPU、Imagination GPU、Synopsys USB控制器等。自研还是外购,直接影响开发周期与成本。

添加图片注释,不超过 140 字(可选)

这一阶段的设计结果通常以架构框图(Block Diagram) 和 微架构文档(Micro-Architecture Document) 的形式呈现。

✅ 关键产出:系统架构图 + 微架构文档

█ 第三阶段:前端设计 —— 把想法变成“逻辑语言”

前端设计,也叫逻辑设计,目标是将抽象的架构方案转化为可执行的数字逻辑。

它不关心物理实现细节,只关注“功能是否正确”。整个过程像是一场精密的“代码—验证”循环。

1. HDL编码:用代码描述硬件

芯片工程师使用硬件描述语言(HDL),如Verilog或VHDL,在寄存器传输级(RTL) 上编写代码,描述每个模块的行为。

例如,一个32位加法器可以用几行Verilog代码完成:

verilog module adder_32bit ( input [31:0] a, input [31:0] b, output [31:0] sum ); assign sum = a + b; endmodule

虽然看起来像软件编程,但HDL的本质是描述硬件结构,每一行代码最终都会对应到具体的逻辑门和触发器。

⚠️ 提示:HDL编码需结合晶圆厂提供的标准单元库进行设计,避免写出无法综合的代码。

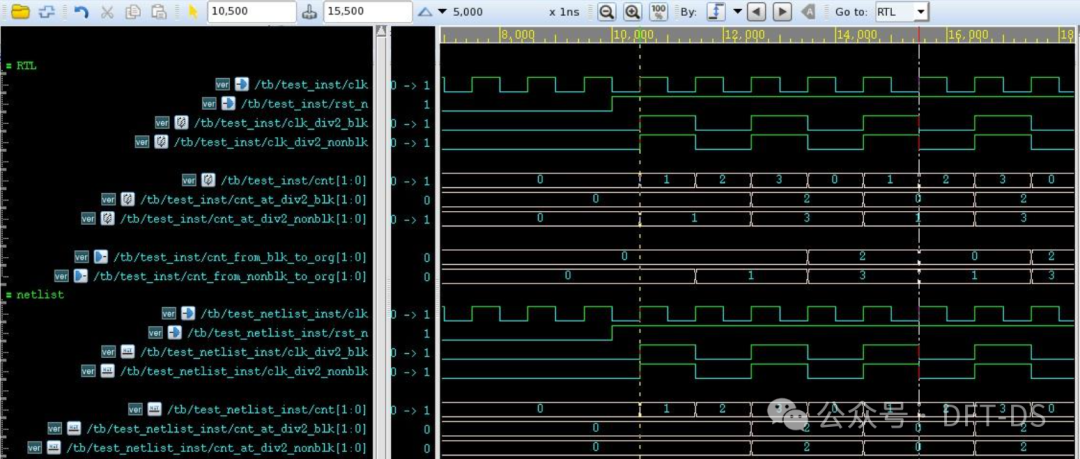

2. 功能仿真与验证

HDL编码完成之后,就要开始第一波验证(Verification)了。

前面我说过,芯片设计几乎每一步都要进行验证或仿真,就是为了确保不出错,因为出错的代价实在太大。

这一步的仿真验证,主要包括电路逻辑功能方面的验证,也就是证明设计的功能是否符合设计规格中的定义,是否存在逻辑实现错误。

如果发现错误,就需要返回上一步,进行修改,甚至要返回方案设计阶段进行修改。修改之后,再重新进行验证。

验证方法包括:(借助工具)通过在搭建的验证环境中输入激励(就是加输入信号),然后看检测输出波形是否和预期一样,以此来进行判断。

常用工具包括:

-

VCS/xrun(Synopsys)

-

QuestaSim(Cadence)

-

Verdi/simvison/indago(用于波形调试)

这个阶段的仿真称为“前仿真”或“功能仿真”,特点是忽略延迟,只验证逻辑正确性。

添加图片注释,不超过 140 字(可选)

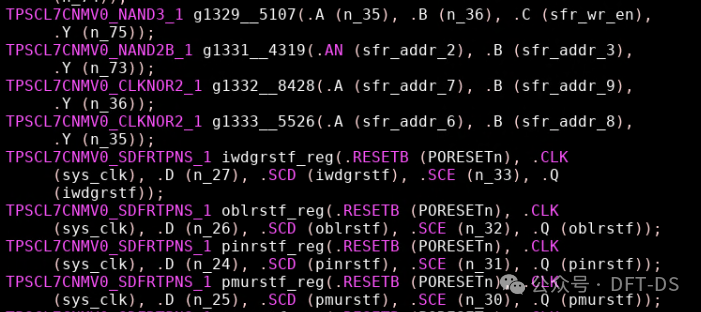

3. 逻辑综合(Synthesis)

当RTL代码通过验证后,就要交给EDA工具进行逻辑综合。

综合工具(如Design Compiler)会做三件事:

-

翻译:将RTL代码转为工艺无关的初级的、未优化的通用门级网表。

-

优化:根据面积、时序、功耗等约束进行逻辑重构。逻辑综合需要设定约束条件,也就是希望逻辑综合出来的电路在面积、时序、时延等(PPA)目标参数上达到的标准。优化,是根据约束条件和工艺库(由晶圆厂提供)参数,进行逻辑结构调整,去掉冗余单元,以此满足要求。

-

映射:将通用逻辑映射到目标工艺库中的标准单元(如NAND2_X1、DFFR)。需要注意的是,不同晶圆厂的工艺库,门电路基本标准单元(standard cell)的面积、时序参数是不一样的。所以,选用的库不一样,综合出来的电路在面积、时序上就不一样。

添加图片注释,不超过 140 字(可选)

最终输出的是一个门级网表(Netlist),也就是由与非门、或非门、寄存器等基本元件组成的连接关系图。

✅ 关键产出:门级网表(Gate-level Netlist)

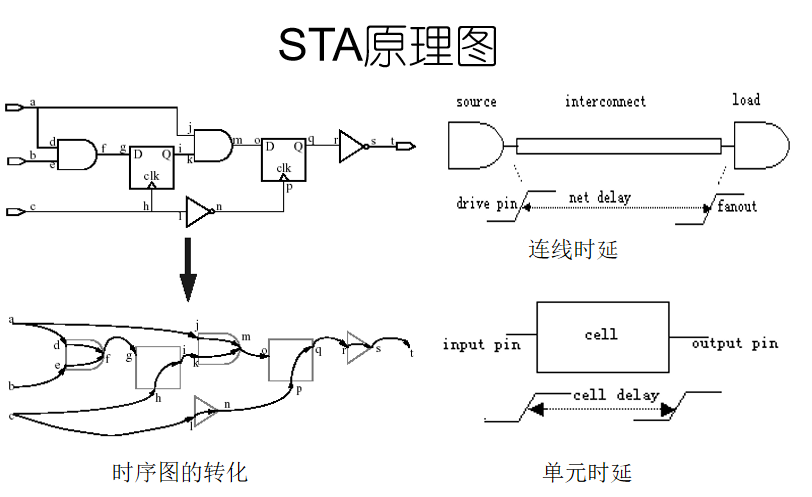

4. 静态时序分析(STA)

综合完成后,必须检查电路是否能在目标频率下稳定工作。综合后的STA还只是pre-sta, 不带延时信息的时序检查,等到后端物理设计完成后还需要带SDF的STA检查。

静态时序分析(Static Timing Analysis, STA) 就是用来验证这一点的。

它会分析所有可能的路径,找出是否存在“建立时间”(Setup Time)或“保持时间”(Hold Time)违例。

关键工具:PrimeTime(Synopsys)

STA的核心是识别“关键路径”——即信号传播最慢的那条路径,它决定了芯片的最高运行频率。

静态时序分析(STA)的作用,主要体现在以下几个方面:

首先,它能帮助我们确定芯片的最高工作频率。

通过详细的时序分析,工程师可以更好地控制工程的各个环节,从而减少延迟,尽可能地提升芯片的工作频率。

芯片的最高工作频率由网表(netlist)的关键路径决定。关键路径是网表中信号传播时延的最长路径。

其次,静态时序分析也是检查时序约束是否满足的重要手段。

在时序分析的过程中,我们可以查看目标模块是否满足预设的约束条件。如果不满足,分析结果将帮助我们精确地定位到问题点,并给出详细的改进建议。

最后,静态时序分析还能用于分析时钟质量。

时钟信号存在抖动、偏移和占空比失真等缺陷。通过时序分析,我们可以有效地验证这些缺陷对目标模块性能的影响。

STA工具,包括Synopsys的PT(Prime Time)工具等。

它可以分为三个基本步骤:

1、将netlist看成一个拓扑图;

2、进行时延计算(连线时延net delay、单元时延cell delay);

3、找到关键路径,并计算时延,进行判断。

添加图片注释,不超过 140 字(可选)

5. 形式验证(Formal Verification)

为了确保综合没有改变原始设计的功能,还需进行形式验证。

它通过数学方法,自动比对原始RTL设计与综合后的网表是否功能等价。

常见工具:Formality(Synopsys),Conformal LEC(Cadence)

6. 覆盖率分析

验证是否“足够”?需要用覆盖率来衡量。

主要包括:

-

代码覆盖率:所有代码是否都被执行过?

-

功能覆盖率:所有预设场景是否都被测试到?

只有当覆盖率达标(接近100%),才能认为验证充分。

✅ 前端设计完成标志:综合后的网表 + 通过STA与形式验证 + 覆盖率达标

几个主要阶段的输入和输出,如下表所示:

添加图片注释,不超过 140 字(可选)

█ 第四阶段:中/后端设计 —— 让逻辑落地为“物理实体”

如果说前端设计是在“纸上谈兵”,那么后端设计就是在“真枪实弹”地建造芯片。

它的任务是:把门级网表转化为可以在硅片上制造的物理版图。

这个过程极其复杂,涉及大量物理效应建模与工艺约束。

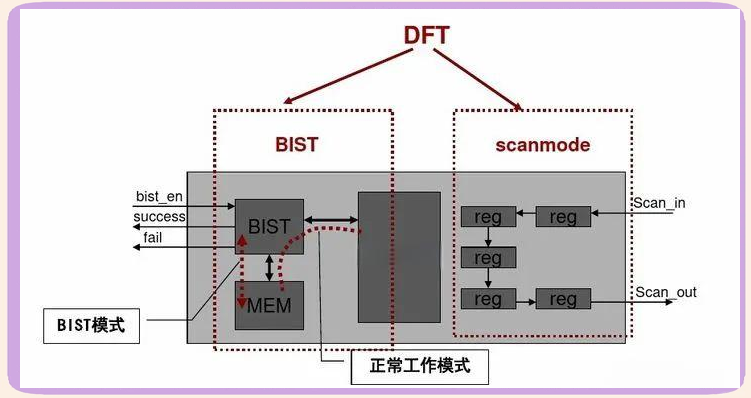

1. 可测性设计(DFT)

现代芯片内部有数十亿晶体管,一旦出问题很难定位。因此,在设计阶段就要加入自检机制。

常用技术:

-

扫描链(Scan Chain):把普通寄存器换成可扫描的,便于测试时注入激励和读取响应。

-

内建自测试(BIST):为内存等模块内置测试电路。

-

边界扫描(Boundary Scan):用于检测芯片引脚连接是否正常。

添加图片注释,不超过 140 字(可选)

DFT示例图 在测试时,在Scan-In阶段加载激励信号,在Capture阶段捕获组合逻辑响应,最终通过Scan-Out移出比对,就能得出结果。 可测性设计技术的基础评价指标包括可控性和可观测性。具体情况可以另行搜索网上资料,限于篇幅就不多介绍了。

DFT通常在综合前和综合过程中插入,但也有人将其归入后端流程。也有些公司,会将可测性设计归为前端设计或者中端实现的范畴。

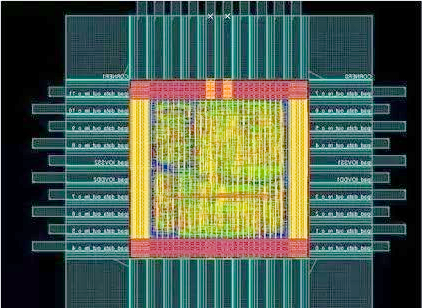

2. 物理实现四部曲

物理布局是芯片设计流程中从逻辑视图向物理视图的转换过程。

它需要考虑到元件的尺寸、形状、相互之间的间距,以及连线的长度和宽度等各种复杂因素。布局的好坏,直接影响到芯片的信号抗干扰能力、寄生电容和电感的大小,决定了芯片的整体性能和可靠性。

好的物理布局,是要实现空间利用率、总线长度、时序的完美平衡。也就是说,空间利用率要尽量高,总线要尽量短,时序要尽量收敛。

物理布局的主要步骤包括:布局规划、布局、时钟树综合、布线等。我们逐一来看:

(1)布局规划(Floorplanning)

确定芯片核心区域大小、I/O位置、宏模块(如RAM、PLL)摆放位置。

要考虑的因素包括:

-

模块间通信距离

-

热分布均衡

-

电源网络规划

工具会参考PDK(Process Design Kit) 中的工艺规则,确保设计可制造。PDK包含了工艺相关的各种参数和模型,比如晶体管尺寸、层间距、金属氧化层厚度等,就连线宽、线距等设计规则都与之相关。如果脱离PDK,你设计的东西,人家根本生产不了,就是白搭。

(2)布局(Placement)

将所有标准单元(standard cells)精确放置在芯片区域内。

目标是平衡:

-

面积利用率(通常70%~90%)

-

时序收敛

-

布线拥塞

(3)时钟树综合(CTS)

时钟树综合(Clock Tree Synthesis,CTS),简单说就是时钟的布线,构建时钟网络。构建时钟网络,使时钟信号尽可能同时到达所有寄存器,减少“时钟偏斜(Clock Skew)”。

理想情况下,时钟偏差应小于时钟周期的10%。

(4)布线(Routing)

连接所有单元之间的信号线,包括电源、地线和数据线。

布线需满足:

-

工艺设计规则(最小线宽、间距)

-

层数限制(现代工艺可达15层以上金属)

-

信号完整性要求(避免串扰、噪声)

工具:Innovus(Cadence)、ICC2(Synopsys)

添加图片注释,不超过 140 字(可选)

(5)寄生参数提取和信号完整性分析

物理布局不限完成之后,又要开始进行验证了。

导线本身的电阻、相邻导线间的互感及耦合电容等因素(寄生参数),会在芯片内部引发信号噪声、串扰和反射等问题,导致信号电压发生波动甚至失真。

因此,需要进行寄生参数的提取,以及信号完整性的分析验证。

(6)静态时序分析&形式验证

Post-STA:

参考文章:

在电路的每个单元位置和各项参数都已确定的情况下,需要再次进行带延时信息的静态时序分析,以确保最终物理设计结果的准确性。

Formal Check:

和前面一样。再做一次形式验证,确认一下电路功能是否与物理设计之前保持一致。

3. 后仿真(Post-layout Simulation)

参考文章:芯片后仿及SDF反标详解

物理布局完成后,要进行带寄生参数的仿真,称为“后仿真”或“时序仿真”。

此时加入了真实的:

-

导线电阻电容(RC parasitics)

-

电源噪声

-

温度效应

目的是验证芯片在真实环境下能否正常工作。

添加图片注释,不超过 140 字(可选)

4. 物理验证

这是流片前的最后一轮“体检”,主要包括:

物理验证,主要包括LVS、DRC、ERC等检查,目的是确保版图的正确性和一致性。

LVS(Layout vs. Schematic):版图对原理图一致性检查,就是版图与逻辑综合后的门级电路图的对比验证。

DRC(Design Rule Checking):版图设计规则检查,检查连线间距,连线宽度等是否满足工艺要求。规则通常都由晶圆厂提供,确保设计在制造过程中不会出现物理上的问题,例如短路、开路、间距不足等。

ERC(Electrical Rue Checking):电气规则检查,检查短路和开路等电气规则违例。

工具:Calibre(SIMENS EDA)

5. 功耗与可靠性分析

-

IR Drop分析:检查电源电压是否因电阻压降而不足。

-

EM(电迁移)分析:长期大电流是否会烧毁金属线?

-

热分析:局部热点是否会导致性能下降或损坏?

工具:RedHawk(Ansys)、Voltus(Cadence)

6. 签核(Sign-off)

注意!布局布线完成后的这几个步骤,包括物理验证、静态时序分析、功耗和可靠性分析等,都属于签核(Sign-off)检查。

签核是流片前的最后一道“守门关”。

如果不满足,就要回到物理设计做修改。如果还是不满足,就需要返到电路设计和验证环节。

如果全都满足,那这个版图就可以送去晶圆厂流片

签核意味着设计团队正式确认:“这个设计可以送去制造了。”

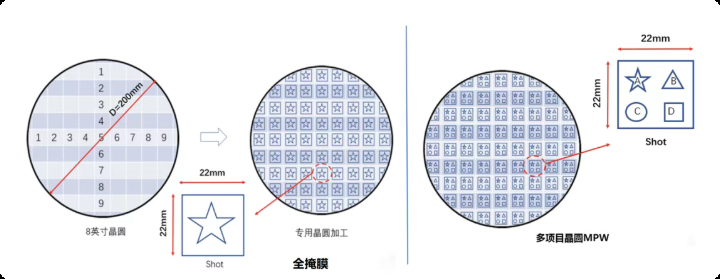

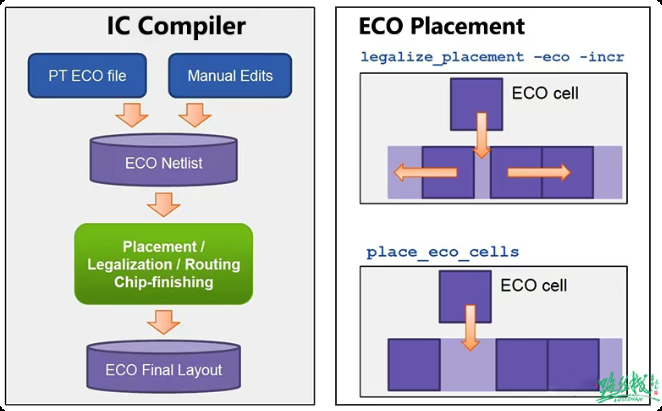

一旦签核,任何修改都需要走工程变更单(ECO) 流程,避免推倒重来。

芯片设计有时候还会进行工程变更(Engineering Change Order,ECO)。

也就是局部修改单元位置或布线或者修改少量逻辑(网表级的),解决STA或后仿真发现的违例问题。通过工程变更,可以避免重新设计和需要重新走完以上所有流程。

添加图片注释,不超过 140 字(可选)

签核也要采用EDA工具,包括了IR分析签核工具、时序分析签核工具、物理验证签核工具等。

对于目前越来越复杂的工艺,实现签核收敛(即所有检查均通过)变得越来越困难。这主要是因为多种物理效应(如工艺偏差OCV、信号完整性SI、电源完整性PI、热效应等)之间存在复杂的相互作用。

以上,就是后端设计的主要流程。在实际项目中,其实还包括了附加流程,例如填充单元插入,以及随着制造工艺不断演进产生的DFM(可制造性设计)等。大家有兴趣可以另外研究。

后端设计几个主要阶段的输入和输出,如下表所示:

添加图片注释,不超过 140 字(可选)

后端设计全部完成之后,就可以输出最终的GDSⅡ文件了。文件包含以下信息:

层次结构和顶层结构:芯片的不同层和顶层结构,包括金属层、多晶硅层、掩膜层、胶片层等。

几何信息:包括芯片各个部位的尺寸、形状、位置以及与其他部位的连接方式等。

特殊功能区域:如联排、防抖动区域、纹理区、DPJ (Diffusion Pocket Junction) 等。

材料属性信息:描述每个层的材料类型、介电常数、厚度等。

✅ 关键产出:GDSII 文件(最终版图数据)

█ 最终一步:流片(Tape-out)

“流片”是芯片设计的里程碑事件。

所谓Tape-out,原意是把设计数据写到磁带上送厂(现已数字化),意为“冻结设计,准备制造”。

添加图片注释,不超过 140 字(可选)

流程如下:

-

将GDSII文件交付晶圆厂(如台积电、中芯国际)。

-

晶圆厂根据版图制作光刻掩模版(Photomask)。

-

使用掩模版进行多次光刻、刻蚀、沉积等工艺,制造出晶圆。

-

经过封装测试,得到成品芯片。

首批制造的芯片称为“工程样品”,需进行全面测试:

-

功能是否正常?

-

频率能否达标?

-

功耗是否超标?

如果一切顺利,恭喜!项目成功。若有问题,则需分析原因,可能返工甚至放弃。

流片结束后,芯片进入测试调试阶段,需进行功能、性能及可靠性验证。若发现问题,则需启动post-mask ECO(Engineering Change Order,工程改变命令)。

添加图片注释,不超过 140 字(可选)

ECO可在流片前、中、后多个阶段发生。若在流片后检查出缺陷,视问题严重程度,可能只需修改少数金属层(Metal Layer),也可能要变动十几层,甚至完全重新流片。ECO是在原设计基础上做局部修正,以避免全部推倒重来,节省时间与经济成本。

尽管ECO提供补救机会,但反复修改仍会显著拉长开发周期、增加不确定性,因此企业必须在设计验证环节力求精准,最大限度降低流片后修改的需求。

█ 总结:一张图看懂全流程

█ 写在最后

芯片设计是一项集科学、工程与艺术于一体的复杂系统工程。它不仅考验技术深度,更依赖团队协作、流程管理和工具链支持。

从一行Verilog代码,到一块指甲盖大小却蕴含百亿晶体管的芯片,背后是无数工程师的心血与智慧。

正如有人所说:“软件改变了世界,而硬件承载了这一切。”

希望这篇文章,能让你对“芯片是如何设计出来的”有一个完整、清晰的认知。

微信视频号:sph0RgSyDYV47z6

快手号:4874645212

抖音号:dy0so323fq2w

小红书号:95619019828

B站1:UID:3546863642871878

B站2:UID: 3546955410049087

参考文献链接

人工智能芯片与自动驾驶

浙公网安备 33010602011771号

浙公网安备 33010602011771号