半导体微缩化的技术突围与光刻革命

随着半导体的发展,我们的生活在过去几十年中发生了巨大变化。50年前,研究人员家中的电器只有收音机和电视机,通信设备也只有电话。即使在办公室,打字机和计算机也并不普遍,只有一些大型企业能够使用大型计算机。而如今,个人计算机几乎已经成为普通家庭的必备之物,性能远超当年的大型计算机,不仅具备计算能力,还能进行通信,另外,只有手掌大小的智能手机也早已在社会生活中普及开来。这一切背后的支撑技术之一就是半导体。

微缩化的指导原则及其效果

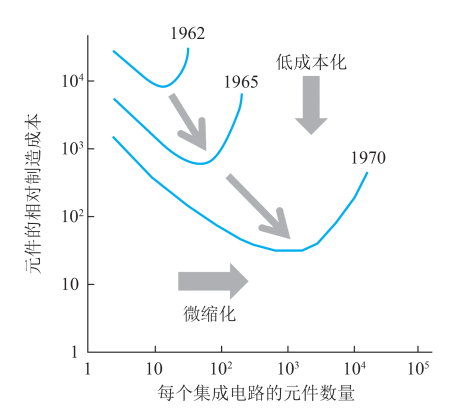

1965年4月,英特尔的创始人之一戈登·摩尔(Gordon Moore)在仙童(Fairchild)公司的研发部门工作期间,在 Electronics 杂志上发表了一篇指导半导体技术发展方向的论文。这篇文章提出了著名的摩尔定律1)。 图 1 展示的就是摩尔定律的内容(箭头是笔者添加的)。这幅图显示: 随着时间的推移,半导体微加工技术的发展将使芯片上的半导体元件数量增加,晶体管的平均成本将会降低。文章预测,成本的降低必将使计算机进入普通家庭。

添加图片注释,不超过 140 字(可选)

图1.摩尔定律1

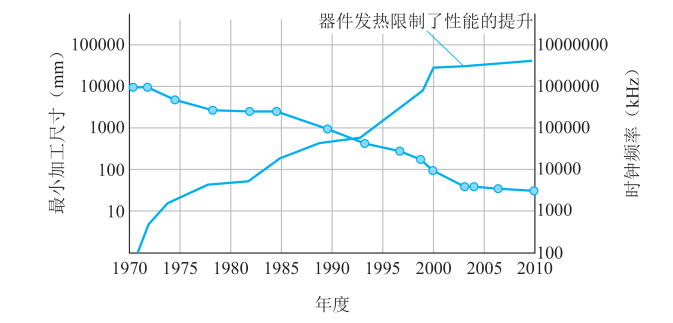

图2展示了半导体中最小加工尺寸及微处理器工作频率的发展历程。如图2所示,尽管元件尺寸不断缩小,但由于器件发热带来的限制,时钟频率已经出现了饱和趋势。

添加图片注释,不超过 140 字(可选)

图2.最小加工尺寸的微缩化与微处理器工作频率的提高

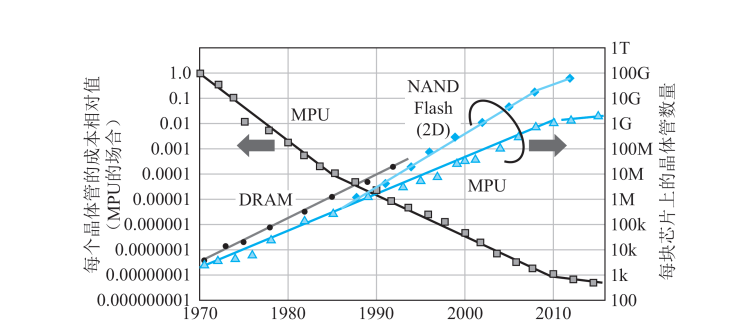

但从系统的角度来看,研究人员对处理器速度的要求仍然不断提高,于是采用了多核并行工作的技术来加快计算速度。因此,芯片上的晶体管数量至今仍在持续增加。另一方面,微缩化带来的最大好处是降低成本。 图3显示了随着微缩化的推进,每个晶体管的成本以及每块芯片上晶体管的数量变化2)。从图中我们看出,每个晶体管的成本相比于最初已经骤减了1亿倍,如前所述,这正是高性能计算机普及到普通家庭的推动力。晶体管的尺寸从10μm级别缩小了1000倍,来到了10nm级别,而面积缩小了1百万倍。当然,除了微缩化(即光刻技术)以外,其他工艺技术、器件技术,以及晶圆尺寸的增大、芯片尺寸的增大等,也为降低成本做出了贡献,但总的来说有一点是非常清楚的:面积的缩小带来的贡献是最大的。这样看来,摩尔定律所具有的经济意义,远超其技术意义。但早年间,光刻技术主要采用接触式曝光技术,微缩化并没有明确的指导原则,而是由材料技术发展所带来的工艺进步来支撑。

添加图片注释,不超过 140 字(可选)

图3. 集成电路芯片上晶体管数量增加,微处理器(MPU)中每个晶体管的成本下降

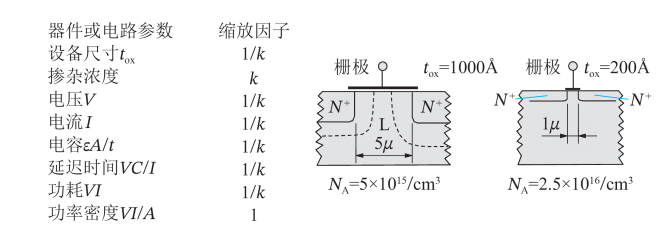

相比之下,IBM 的罗伯特·丹纳德(Robert Dennard)在1974年提出的缩放定律(ScalingLaw)为金属氧化物半导体场效应晶体管(MOSFET)的微缩化提供了明确的技术指导原则,如图4所示。这个时代,光刻技术也发生了重大变化,从接触式曝光发展到投影式曝光,尤其是缩微投影曝光技术的开发,为器件的微缩化提供了明确的指导原则。

添加图片注释,不超过 140 字(可选)

图4.Dennard缩放定律3)

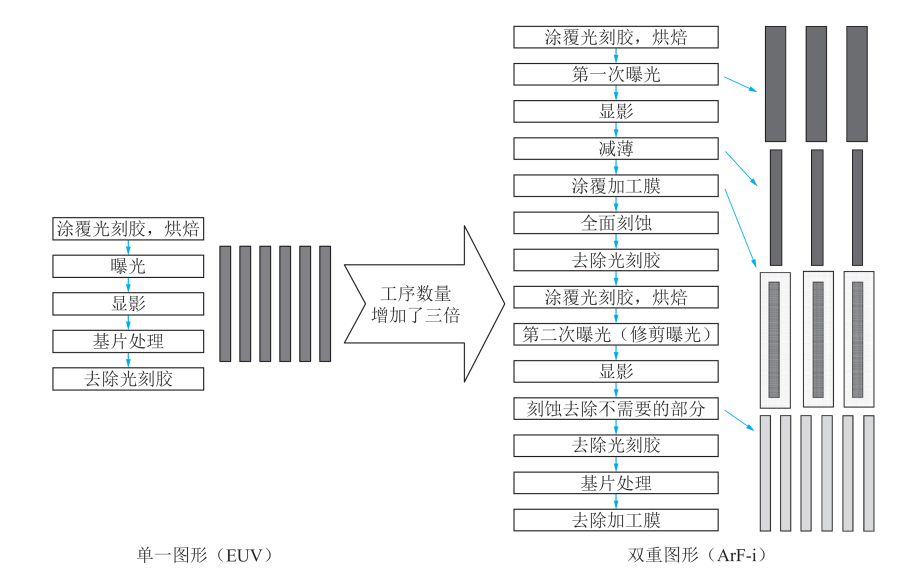

根据瑞利判据(Rayleigh Criterion),分辨率取决于曝光波长和投影光学系统的数值孔径(NA)。

添加图片注释,不超过 140 字(可选)

这里,R代表分辨率,λ代表曝光波长,NA是投影光学系统的数值孔径,K1是由光刻胶材料和曝光方式决定的工艺因子。根据这个公式,我们可以看出,要提高分辨率R,就需要增大数值孔径NA,缩短曝光波长λ,缩小工艺因子K1。因此,缩放法则和瑞利准则提供了提高分辨率的明确指导,从而使微缩化真正成为可能。这种微缩化使摩尔定律得以实现,也为半导体的高度集成化、高性能化、低成本化和低功耗化提供了原动力。各种工艺技术和器件技术支持着高度的集成化,但光刻技术的发展是其中最核心的要素。这里的光刻技术是一个综合的概念,包含了光刻机技术、光源技术、光刻胶技术、掩膜技术、掩膜版制作技术,以及加工后的图形评估技术等一系列基础技术。此外,将光刻胶图形转移到基板上的干法刻蚀技术也为微缩化做出了重要贡献。时至今日,多重图形化技术已经成为微缩加工的核心。

光刻技术的发展及其困难

在过去50年中,光刻技术多次遇到分辨率的瓶颈,解决办法都是通过提高数值孔径(NA)缩短波长等手段,来提升分辨率。然而近年来,数值孔径和缩短波长这两种手段也已经用到了极限,虽然研究人员尝试了各种方法来提升分辨率,但在过去几年并没有明显的进展。

半导体器件微缩化的需求还在提高。为了解决困难,研究人员引入了多重图形化技术,以应对器件的微缩化需求。多重图形化的方法大致可以分为分割法(PitchSplit)和间隔法(Sidewall Spacer)两种。

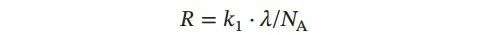

分割法,我们以双重图形化为例来讲解。首先将图形中的条纹根据相邻关系分成两组,然后按照图5(a)所示的方式将其分割成两个层次的图形。如果无法分割,就需要调整部分图形的形状以实现分割。工艺流程如图5(b)所示。首先在硅基片上形成加工层和牺牲层, 并涂覆光刻胶。然后进行第一层图形的曝光和显影,并对其进行减薄处理(即缩小条纹尺寸), 再将得到的图形刻蚀到牺牲层上。接着,再次涂覆光刻胶并进行第二层图形的曝光和显影。在这个过程中,需要非常精准地把第二层图形套刻在第一层图形上,这对于实现高精度的微缩化来说非常重要。再对第二层图形进行减薄处理。最后,把第二层图形和之前加工完成的第一层牺牲层图形一起刻蚀到加工层上,整个工艺就完成了。这项技术的特点在于它仍然适用于传统的二维图形,但套刻精度和减薄精度对条纹尺寸(条纹间隔)有很大的影响,这是一个困难所在。这里展示的工艺是双重图形化技术的一个简单示例,实际生产中有许多不同的样式。另外,重复这种思路,研究人员还可以实现更精细的工艺,例如四重图形化、八重图形化等。

添加图片注释,不超过 140 字(可选)

图5.分割法双重图形化工艺

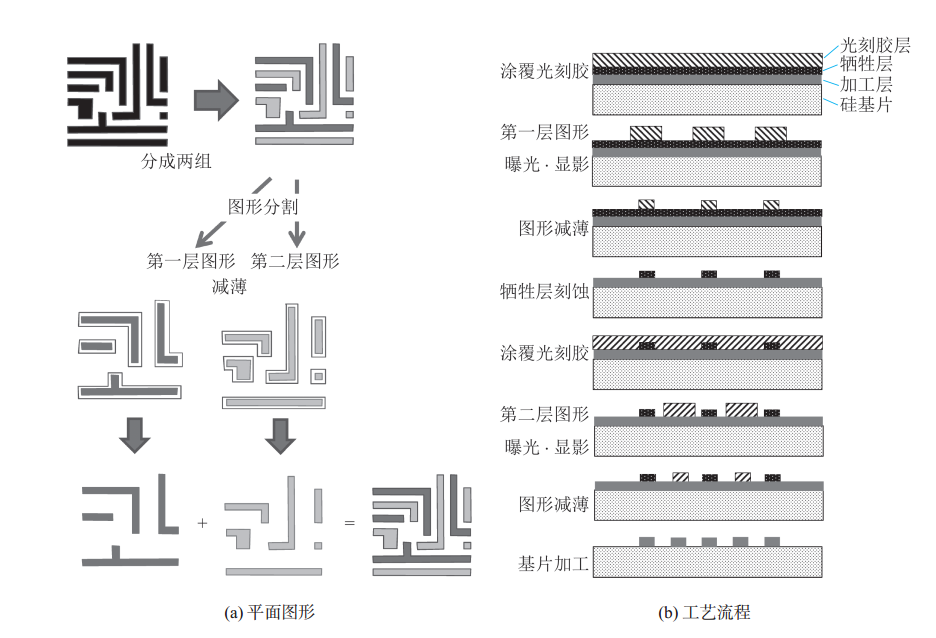

接下来对于间隔法, 我们也用双重图形化为例来解释。该方法适用于简单的条纹/沟槽(Line and Space)图形。首先,用传统工艺加工出一定尺寸和间隔的光刻胶图形,如图6所示。然后对该图形进行减薄,使得条纹间隔与条纹宽度之比为3∶1。然后涂覆一层加工膜,使其在条纹的两侧都形成侧壁。这里需要调整侧壁的膜厚,使其与条纹宽度相同。然后进行全面刻蚀, 直接露出光刻胶层,基片上只保留光刻胶条纹以及侧壁。除去光刻胶, 基片上只保留侧壁,其尺寸和间距都等于前面减薄后的条纹宽度。 最后再次通过涂胶、 曝光和刻蚀在硅片上刻出图形,然后除去侧壁, 并获得所需的图形。这种技术的特点是不需要在微小的区域进行套刻曝光,因此不需要提高套刻精度。通过重复上述思路,可以推广到四重图形化、八重图形化等。

添加图片注释,不超过 140 字(可选)

图6.间隔法双重图形化工艺

这两个例子都证明,多重图形化技术可以实现传统工艺难以达到的分辨率。但问题是工艺变得非常复杂,制造成本非常高。此外,在分割法中,光刻机的套刻精度限制着整体图形的精度,因此提高光刻机的套刻精度也就变得非常重要。

下一代光刻技术及未来发展

各种尚在探索和研发中的下一代光刻技术(NGL:Next Generation Lithography),也叫后光刻技术,包括: EUV 光刻技术,以无掩膜光刻技术(ML2:Maskless Lithograpny)为代表的电子束刻蚀技术, 纳米压印光刻技术(NIL: Nano Imprint Lithography),以及定向自组装(DSA:Directed Self-Assembly)技术等。电子束刻蚀技术不仅适用于晶圆加工,还广泛应用于掩膜版绘制,并形成了一个技术体系。电子束刻蚀技术的挑战在于其绘制速度较慢,因此量产应用尚未实现。在掩膜版的绘制方面也面临着同样的挑战,近年来出现了许多复杂的掩膜,甚至一整天都无法绘制完成一张掩膜版。为了解决这个问题, 研究人员正在努力研发各种多电子束刻蚀技术。通过多电子束刻蚀技术,即使是以前需要很长时间绘制的复杂的掩膜版图形,例如以前必须使用反演光刻技术(ILT:Inverse Lithography Technology)才能得到的掩膜,现在也可以在短时间内绘制完成,因此这项技术可能会促进新的光刻技术的改革。

此外,作为半导体微加工技术的发展,以MEMS为首的各种加工技术正在发展。

参考文献链接

人工智能芯片与自动驾驶

浙公网安备 33010602011771号

浙公网安备 33010602011771号