Verilog-格雷码加法器

1、概述

格雷码执行加1操作最多只会变1位,可用在多位地址指针中消除毛刺。

2、verilog代码

1 `timescale 1ns / 1ps 2 3 module gray_adder 4 #(parameter length = 5) 5 ( 6 input clk, 7 input rstn, 8 input inc, 9 output [length-1:0] Gray 10 ); 11 12 reg [length-1:0] Gray_reg; 13 reg [length-1:0] Gray_next_reg; 14 15 reg [length-1:0] Bin_reg; 16 reg [length-1:0] Bin_next_reg; 17 18 integer i; 19 20 always @(posedge clk or negedge rstn) begin 21 if(!rstn) begin 22 Gray_reg <= 0; 23 end 24 else begin 25 Gray_reg <= Gray_next_reg; 26 end 27 end 28 29 30 always @(*) begin 31 Bin_reg[length-1] = Gray_reg[length-1]; // 格雷码转二进制码 32 for(i=length-2;i>=0;i=i-1) 33 Bin_reg[i] = Bin_reg[i+1]^Gray_reg[i]; 34 Bin_next_reg = Bin_reg + inc; // 二进制码加1 35 Gray_next_reg = (Bin_next_reg>>1)^Bin_next_reg; // 二进制码转回格雷码 36 end 37 38 assign Gray = Gray_reg; 39 40 endmodule

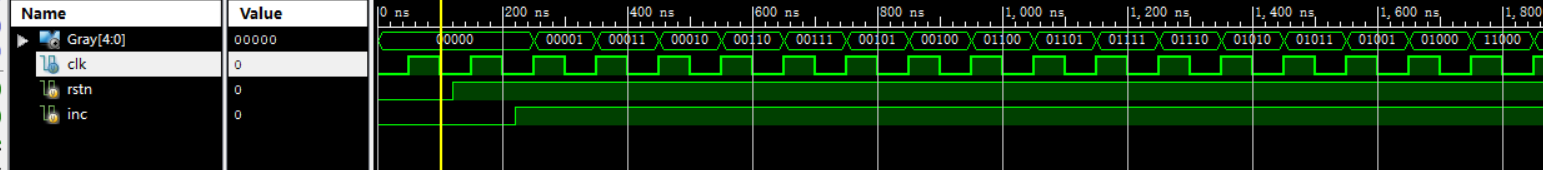

3、仿真波形

浙公网安备 33010602011771号

浙公网安备 33010602011771号