第五章第1节 存储系统的层次结构

一、层次结构概述

1、存储器的性能指标

存储容量

SM=w·l·m,w、l、m为存储体的字长、字数、个数

存取速度

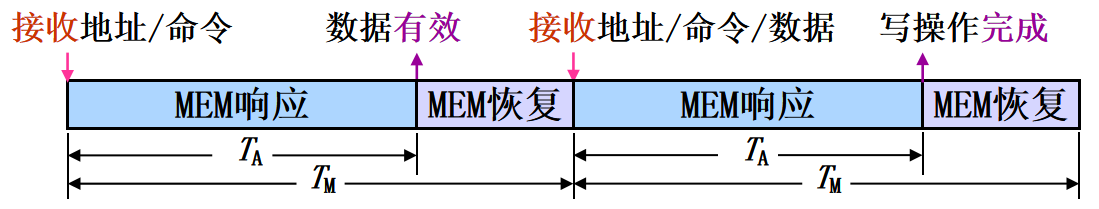

访问时间(TA)—接收命令-操作完成的时间

存取周期(TM)—两次操作请求的最短间隔时间

TM=TA+T恢复,如DRAM刷新∈T恢复

传输速度

MEM带宽(BM)—最大数据传输率(最小数据间隔的倒数)

BM=m·w/TM

2、层次结构的引入

MEM的用户需求为大容量、高速度、低价格。

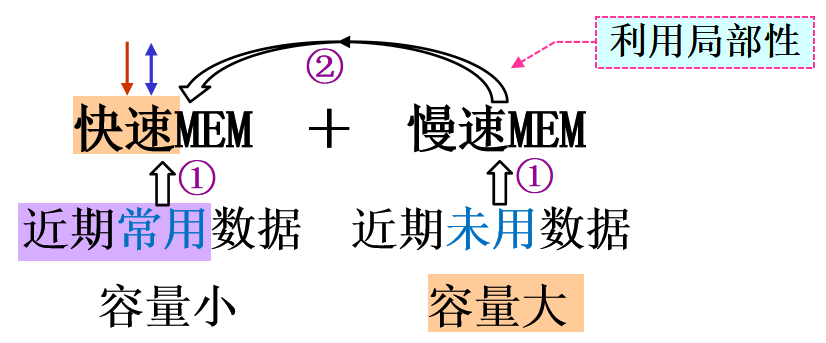

程序访问的局部性原理:程序运行时,指令和数据访问所呈现出的相对簇聚现象有时间局部性和空间局部性。

时间局部性—最近访问过的信息,将再次被访问。

空间局部性—最近访问信息的相邻信息,将很快被访问。

通过层次结构的小容量快速MEM和大容量慢速MEM来解决用户需求。根据局部性原理,将近期常用数据放快速MEM中,近期未用数据放在慢速MEM。

3、存储系统的层次结构

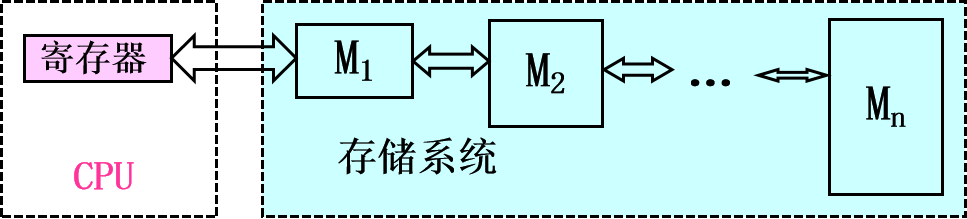

结构与组成

多种MEM级联,按速度分层、协调工作。

工作方式

信息存储—上级MEM中信息为下级MEM中信息的副本

信息传递—外部只访问M1,内部各级MEM间透明地传递信息

预期目标

① c≈cn ② TA≈TA1

注:—目标①和②实现后,容量S与TA及c已无矛盾

4、存储系统的性能参数

存储容量

有效容量S=S_{M_n }

每位平均价格(c )

c=(c1SM1+c2SM2+…+cnSMn)/(SM1+SM2+…+SMn)

命中率H

H=N1/(N1+N2+…+Nn),Ni为Mi中访问到的次数

缺失率(F)— F=1-H

平均访问时间(TA )

TA=H·T1+(1-H)(TA2+T1)=T1+(1-H)TA2

=T命中+F·T缺失

层次结构的实现要求

目标①要求—SM1<<SM2<<…<<SMn,TM1<<TM2<<…<<TMn

目标②要求—H 较大

二、层次结构组织

1、存储系统的层次数量

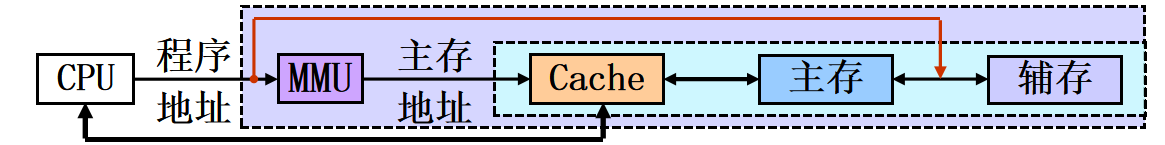

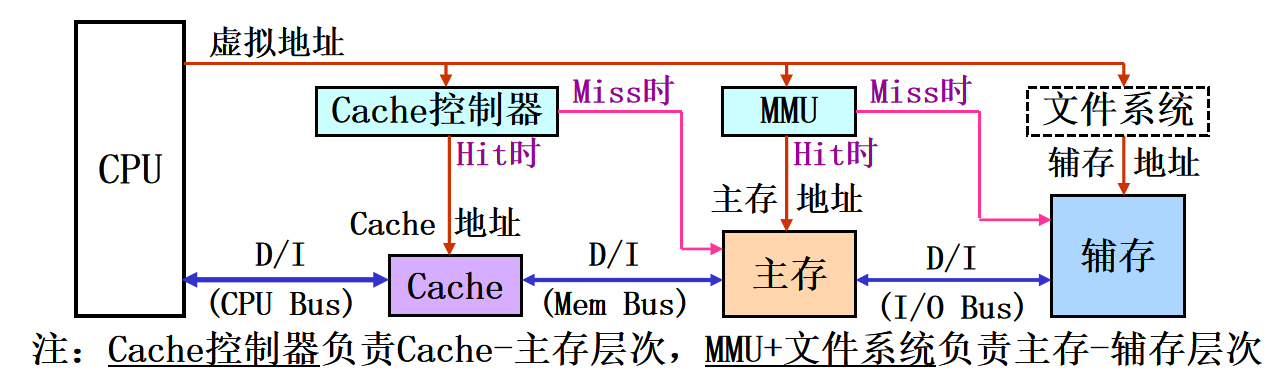

常见的层次数量—Cache-主存-辅存,以主存为中心。

Cache-主存层次

解决主存速度问题。层次管理、地址变换全部由硬件实现。

主存-辅存层次

解决主存容量问题。层次管理由软件实现,地址变换由硬件实现

常实现虚拟存储器(CPU按程序MEM顺序执行 含访问主存)

2、层次管理单元的组织

主要功能:实现层次管理、地址变换。

存储器访问地址类型

主存、辅存为虚地址,Cache可为实地址或虚地址。

采用虚拟Cache的话,虽然可以减少一次地址变换,但是进程切换需清空Cache、数据共享困难、I/O麻烦。故Cache常为物理地址。

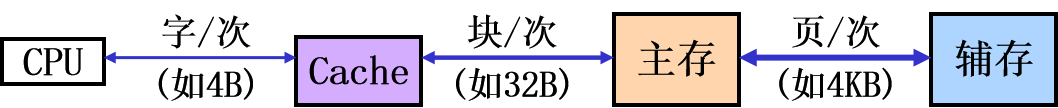

层间信息的交换单位

一次交换多个字,采用猝发传送(成组传送)。

Tn个字=T地址+T存取+n*T传输。MEM离CPU越远,n越大;n通过量化分析得到。

层次管理的实现方式

Cache-主存用硬件实现,主存-辅存用软件实现,地址变换均用硬件实现。

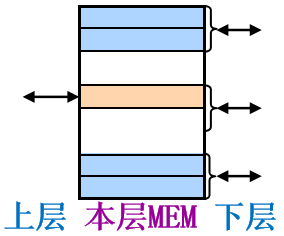

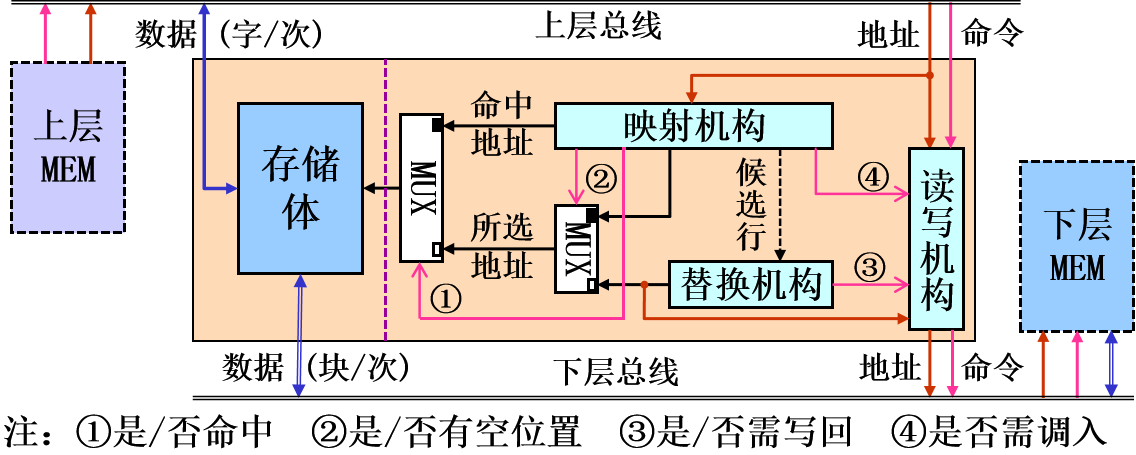

3、层次MEM的结构

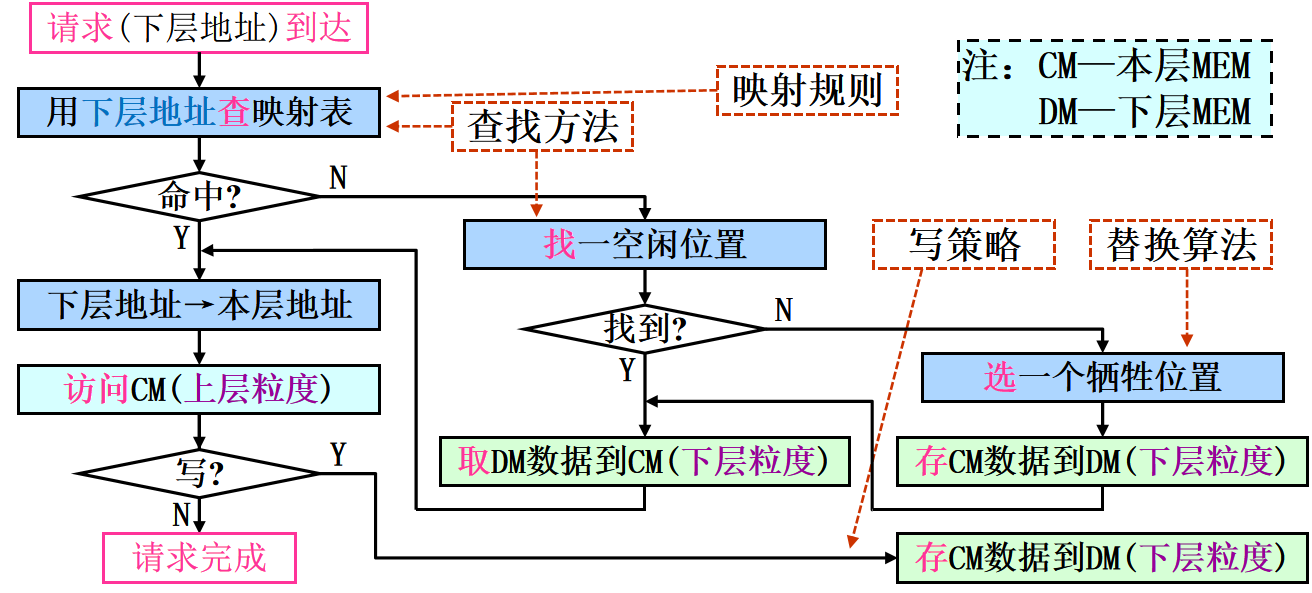

MEM空间管理

编址单位为上层访问的最小粒度 ,交换粒度有两种(面向上层、下层)。

要解决映射规则、查找方法、替换算法、写策略这些问题。

硬件组成

存储体和控制器。

性能优化

TA=T命中+F·T缺失,T命中= T查找+T访问,T缺失≥ T调入

在cache中从三个方面讨论性能优化。

本文来自博客园,作者:流云轻响,转载请注明原文链接:https://www.cnblogs.com/wozra/p/16250456.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号