FPGA Interchange Format

目前 FPGA 厂商提供的开发工具多数为闭源的二进制形式,这极大限制了研究人员对 FPGA 后端工具(如布局布线)进行创新,许多研究人员倾向于在理论架构而不是商业架构上评估他们的算法。

FPGA 工具链的组成比较复杂,将硬件描述语言编译到目标 FPGA 二进制的流程可以分为三个阶段:综合、布局布线、比特流生成。FPGA 交换格式(FPGA Interchange Format,FPGAIF)是由 CHIPS Alliance 主持的一个开源项目,旨在为 FPGA 工具链的三个阶段之间提供标准的信息交换格式,以降低对 FPGA 后端工具进行创新的门槛。

FPGAIF 的组成

FPGAIF 提供了三种关键的 FPGA 供应商无关且 FPGA 设备无关的格式用以在不同工具之间进行信息交换:

- 设备资源:用以定义 FPGA 内部结构以及描述 FPGA 逻辑块的技术单元库。

- 逻辑网表:用于存放综合工具生成的后综合网络信息。

- 物理网表:用于存放布局布线工具生成的布局位置和布线连接。

为了在描述设备的泛化性和异化性之间得到权衡,FPGAIF 偏向于使用当今市场上主流使用的架构,即岛式架构:由可重构逻辑块、硬化逻辑块、信号交换块、输入输出块构成的二维阵列。这么做使得该标准拥有更好的通用性和简洁性,开发人员更易于使用和部署。

FPGAIF 的实现

由于 FPGA 设备拥有大量的单元和单元之间连接的信息需要存储在数据库中,使用文本存储会占用大量的存储空间。FPGAIF 选择使用开源序列化工具 Cap'n Proto 作为实现格式,以提升在运行时和磁盘内存占用方面具的效率。

CHIPS Alliance 提供的基于 Cap'n Proto Schema 的 FPGAIF 官方实现:fpga-interchange-schema。

CHIPS Alliance 还提供了一个 Python 工具用于读写设备数据库、逻辑网表和物理网表:python-fpga-interchange。

FPGAIF 的架构

下面我们分别对设备资源、逻辑网表和物理网表的架构进行详细介绍。

设备资源

设备资源模式旨在完整描述基于孤岛的 FPGA 设计,其所遵循的层次关系为“ Device > Tile > Site > BEL ”。

基本逻辑单元(Basic Element of Logic,BEL)是 FPGA 中最基本的不可分割的原子组件,包括逻辑 BEL 和布线 BEL 两种类别。逻辑 BEL 是一个可编程的逻辑部件,可以用于实现设计单元,如 LUT、CARRY、FF 等。在 Vivado 中,place_design 操作会将网表中的叶子节点映射到逻辑 BEL 上。布线 BEL 是一个可编程的多路复用器,可以用于不同 BEL 之间的信号布线,如 FFMUX、OUTMUX 等。在 Vivado 中,route_design 操作会根据设计要求在 BEL 之间建立信号通道。

特别地,还有一种站点端口 BEL ,用于连接信号到站点端口上。

每个 BEL 都有可配置的连接将输入管脚连接到输出管脚上,这种连接被称为可编程互联点(Programmable Interconnect Point,PIP)。逻辑 BEL 和布线 BEL 都可以实现 PIP。当使用一个逻辑 BEL 实现 PIP 时,该逻辑 BEL 必须是空闲的,即未被网表的叶子节点占用,这种操作在布线操作中被称为“布线直通”。

站点(Site)由一组相关的基本逻辑单元与它们相关的内部连线和输入输出管脚构成,如 SLICE、DSP、BRAM 等。每个站点都拥有一个唯一的 _X#Y# 后缀来表示它们在网格中的位置。SLICE 是赛灵思 FPGA 中最常见的站点,一个 SLICE 包含4个函数发生器(或查找表)、8个存储单元、3个多路复用器、1个进位逻辑。SLICE 分为 SLICEL(SLICE for Logic)和 SLICEM(SLICE for Menory)两种,二者都可以提供算数逻辑功能和存储功能,后者能额外提供分布式 RAM 存储和 32 位移位寄存器功能。

分块(Tile)是比站点更高一级的抽象,也是构成 FPGA 设备的基本单元。一个分块可以不包含站点,也可以包含一个或多个站点。分块没有用户可见的管脚,而是使用独立命名的信号线通过 PIP 来连接不同的站点。在赛灵思 FPGA 架构中,设备中的资源按列进行组织,每一列中的所有分块都是相同类型的。CLB 是赛灵思 FPGA 中数量最多的分块,一个结构子区域中的一列资源一般包含 50-60 个 CLB,一个 CLB 可以包含一个 SLICEL 和一个 SLICEM 或两个 SLICEL。

结构子区域(Fabric Sub Region,FSR)或称为时钟区域(Clock Region),是由多个不同资源分片组成的一个 2D 区域。一个结构子区域内拥有独立的时钟布线和分发轨道,并与相邻结构子区域中的轨道相接,形成设备时钟网络资源集。

超级逻辑区域(Super Logic Region,SLR)是使用赛灵思堆叠硅片互联(Stacked Silicon Interconnect,SSI)技术的多晶片 FPGA 设备所特有的结构,单片上拥有一个超级逻辑区域,由 2D 结构子区域阵列组成。多个晶片之间通过特殊的 Laguna 分块来替换 CLB 进行通信。

设备(Device)是最高层次的概念,通常由 2D 结构子区域阵列或数个纵向排列的超级逻辑区域组成。上述的层次关系可以总结为下图。

回到我们的 FPGAIF 的架构中。FPGAIF 的设备资源模型定义了必要的 FPGA 设备中的资源种类和资源连接方式,以服务布局布线工具,同时也为综合工具和比特流生成工具提供了统一的信息交换格式。在 FPGAIF 官方实现中的 fpga-interchange-schema/interchange/DeviceResources.capnp 文件可以得到设备资源模型定义,其层次关系如下图所示。

布局相关的定义对象和实例对象

为了减少设备资源模型中的数据重复,分块和站点都有一个类型。大多数分块和站点的定义都在类型中,而不是在每个实例中重复。这确实会导致一些更复杂的间接问题,在下面会提供一些额外的解释。

大多数站点类型定义是独立于和分块类型定义的,可以从“SiteType”结构体看到站点类型的定义。站点类型提供了以下几种资源描述:基本逻辑单元的管脚、站点的管脚、基本逻辑单元的实例、站点内的可编程互联点、站点内的硬连接。

分块类型的定义中,除了对分块内部的硬连接和可编程互联点进行描述外,还使用“SiteTypeInTileType”与分块内的站点建立联系,可以从“TileType”结构体看到分块类型的定义。在大多数现实情况下,一个分块会包含一个或多个相同类型的站点,但分块类型仍然提供了分块包含不同站点的方式。在“SiteTypeInTileType”结构体中,会使用“primaryType”指定分块内主要的站点类型,使用“primaryPinsToTileWires”指定连接到分块硬连接的主要站点的管脚,再使用“altPinsToPrimaryPins”将其他类型站点的管脚映射到主要站点的管脚上。

布线相关资源

在站点内部,可能会使用四种布线资源:基本逻辑单元的管脚(BELPin)、站点的导线(SiteWire)、站点的可编程互联点(SitePIP)、站点的管脚(SitePin)。一个完全布线的网络总是从一个基本逻辑单元的输出管脚开始,该管脚会被连接到一个站点导线。如果一个网络的汇点在当前站点可达,则会使用站点可编程互联点连接到一个站点导线,以到达目的基本逻辑单元的输入管脚。

在站点之间,可能会使用三种布线资源:分块的导线(Wire)、分块的节点(Node)、分块的可编程互联点(PIP)。分块的导线是分块内部的一段金属线,其两端是可编程互联点或站点管脚等。分块的节点是多个分块导线的集合,它们被物理连接在一起,而且可能横跨多个分块。分块的可编程互联点是可编程的多路复用器,用于决定是否将其输入端连接到输出端,从而将节点连接在一起,形成设计中特定网络所需的布线。

时序模型

即使没有严格的标准来定义一个给定的架构需要定义多少工艺角模型,一个时序延迟模型通常包括一个“快”和一个“慢”工艺角,每个工艺角都有三个典型的延迟度量,即“最小/典型/最大”。

有三个主要的位置必须定义时间延迟:

- 基本逻辑单元的管脚。这些延迟可以是时序的(与时钟引脚相关联)或组合的(与输入/输出对相关联),至少有四种类型的管脚延迟需要考虑:

- 组合逻辑延迟时间(comb):输入到输出的延迟时间。

- 建立时间(setup):时钟沿到来之前输入信号必须保持稳定的最小时间。

- 保持时间(hold):时钟沿到来之后输入信号必须保持稳定的最小时间。

- 触发器延迟时间(clock2q):输入满足 setup/hold 时序要求,从时钟沿到来时刻到输出端 Q 变化至稳定的时间。

- (站点或分块)导线:导线的传输延迟,使用 RC 模型建模。

- (站点或分块)可编程互联点:两根导线连接的传输延迟。

逻辑网表

综合工具的输出是逻辑网表,实际上是由网络连接的逻辑原语所构成的图,这些逻辑原语在单元实例中被定义。这些逻辑原语或单元实例并没有被指定其在 FPGA 上的物理位置,需要布局工具进行映射。逻辑原语之间的网络连接只是逻辑上的连接,需要布线工具进行导通。下面我们介绍逻辑网表中的几个逻辑对象,其关系如下图所示。

单元(Cell)是网表中逻辑对象的实例,按照树状结构组织。叶单元是一个原语或原语宏(如 LUT、CARRY、FF 等),在逻辑网表中没有进一步的逻辑细节。非叶单元是包含一个或多个逻辑对象实例的模块,并总是以叶单元结束。在布局操作中,叶单元会被映射到 FPGA 上的设备资源,有可能是基本逻辑单元,也有可能是站点。

引脚(Pin)是逻辑原语或非叶单元上的逻辑连接点。引脚可以是包含单个连接的标量引脚,也可以被定义为将多个信号分组在一起的总线引脚。

端口(Port)是一种特殊类型的引脚,为顶层模块提供外部连接,或为非叶节点提供内部连接点,以连接内部多个逻辑模块或逻辑原语。端口可以是包含单个连接的标量端口,也可以是将多个信号组合在一起的总线端口。

网络(Net)是一组相互连接的引脚、端口和导线,在逻辑网表中,这种连接时逻辑上的,用于为布线工具指定哪些引脚、端口和导线之间需要布线导通。网络可以是带有单一信号的标量网,也可以是带有多个信号的标量网组的总线网络。

在 FPGAIF 官方实现中的 fpga-interchange-schema/interchange/LogicalNetlist.capnp 文件可以得到逻辑网表模型定义,其层次关系如下图所示。

物理网表

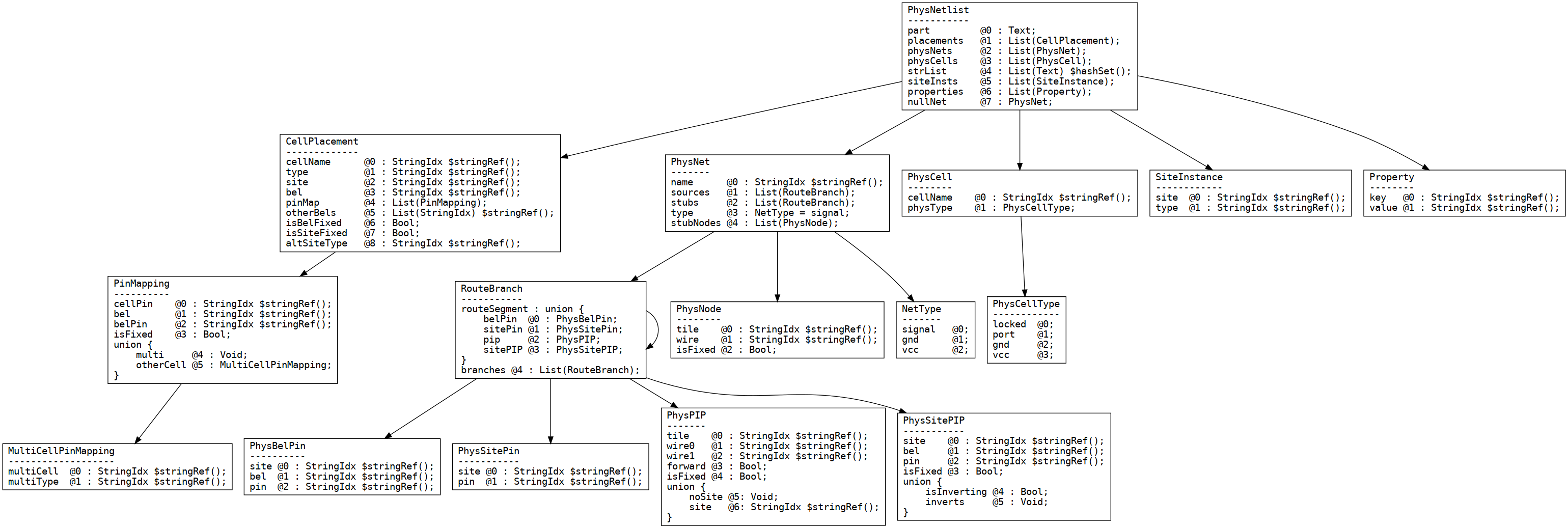

物理网表是布局布线工具的输出,用于描述逻辑网表到设备资源的映射,它包含逻辑原语到硬件上基本逻辑单元的映射,以及逻辑网络到可编程互联资源的映射,其关系如下图所示。

在物理网表中,单元(Cell)将会被映射到一个基本逻辑单元或一个站点,指定其所在的基本逻辑单元或站点的物理位置(在设备资源中的坐标),单元的引脚会被映射到指定基本逻辑单元的引脚上。

在物理网表中,网络(Net)将会被映射到设备上的实际布线资源(如导线、节点、可编程互联点等),并通过引脚连接到基本逻辑单元和站点。一个网络由一个或多个源节点与一个或多个汇节点组成,中间由基本逻辑单元和站点的可编程互联点和引脚进行导通。一个网络根据树状结构组织多个布线分支,一个布线分支可以由一个基本逻辑单元或站点的可编程逻辑点或引脚,以及多个布线分支构成。下图分别是逻辑网表中的逻辑网络连接和物理网表中的物理网络连接。

下图是布线操作中各个对象之间的连接关系。

在 FPGAIF 官方实现中的 fpga-interchange-schema/interchange/PhysicalNetlist.capnp 文件可以得到物理网表模型定义,其层次关系如下图所示。

浙公网安备 33010602011771号

浙公网安备 33010602011771号