数字IC题

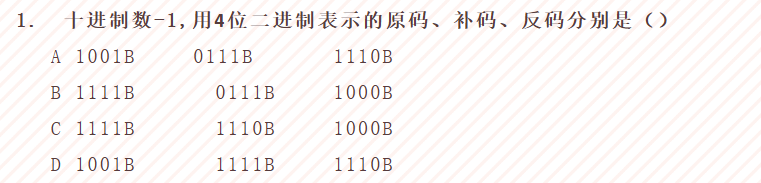

单选

解:C

-1的源码为4‘b1001,反码为符号位不变,其他位取反4’b1110,补码为反码加1,4‘b1111。

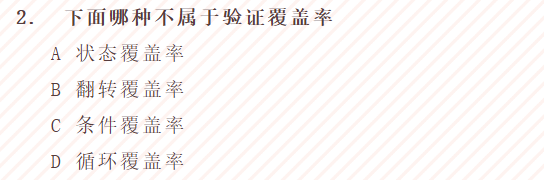

解:D

验证覆盖率包括:代码覆盖率+功能覆盖率

代码覆盖率有:语句覆盖率(行覆盖率),状态(FSM)覆盖率,翻转覆盖率,条件覆盖率、分支覆盖率等

功能覆盖率:又称黑盒测试覆盖率,只关心功能,不关心具体的代码是如何实现的。通过测试用例覆盖,实现方式主要分为覆盖点(coverage points)和断言(arrertion)。

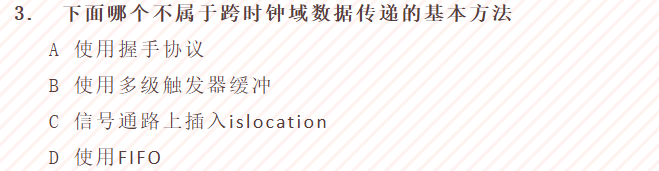

解:C

A:异步握手协议是跨时钟传递数据的常用方法。通过请求(req)和应答(ack)等信号交互,确保数据在时钟域间的可靠传递。

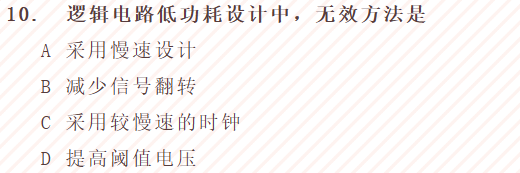

B:对于单bit信号的跨时钟同步,通常会打多拍进行缓存,利用触发器的同步特性减少亚稳态的影响。多bit时则需要格雷码等措施避免多位发生变化导致的竞争冒险。

C:有误。信号通路上的 isolation(隔离)主要用于电源域的隔离,服务于低功耗设计。当芯片存在不同电源域(部分区域断电、部分区域供电时),隔离单元可避免断电域的异常信号传递到供电域,保障电路在低功耗模式下的信号可靠性,防止因电源状态变化导致的逻辑错误或功能异常。

D:FIFO(先进先出队列)是多 bit 数据流跨时钟域传递的经典方法(如高速时钟域到低速时钟域的数据流缓冲),通过异步 FIFO 实现不同时钟域间的数据 “暂存 - 转发”,保证数据完整性。

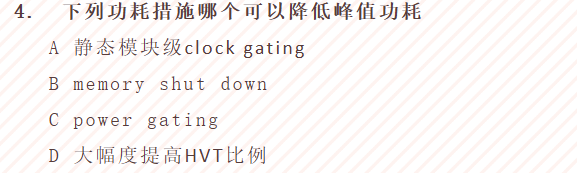

解:C

静态功耗:又称泄漏功耗或待机功耗,是电路无逻辑翻转、处于待机 / 部分关闭但未完全断电状态下的功耗。核心来源是漏电流,受温度和制程影响显著,制程越先进,晶体管尺寸缩小,漏电流占比越高;温度升高时,漏电流呈指数级增长,静态功耗会大幅上升。

动态功耗:是电路执行逻辑操作(如信号翻转、数据传输)过程中产生的功耗。\(P_{switch}=CV^2f\),与电压的平方、工作频率、负载电容成正比 。

峰值功耗:电路在短时间内(如纳秒至微秒级)达到的最大功耗。

A:时钟门控通过关闭空闲模块的时钟,减少动态功耗,但 “静态模块级” 意味着门控针对 “长期不活跃” 的模块,而非峰值时刻动态调整活跃模块数量。

B:关闭存储器可减少该模块的功耗,但峰值功耗通常由多个模块(如运算单元、高速接口等)同时高速工作主导.

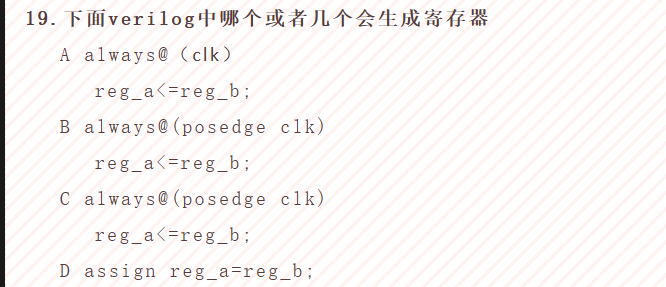

C:正确,电源门控可动态切断部分模块的电源,使这些模块完全不消耗功耗(动态 + 静态)。在 “峰值功耗出现时”,若能关闭暂时不需要的模块,可直接减少 “同时活跃的模块数量”,从而有效降低整体峰值功耗。

D:HVT 高阈值晶体管的泄漏功耗低(利于降低静态功耗),但开关速度慢、驱动能力弱,对 “动态功耗主导的峰值功耗” 帮助极小.

解:C

注意,输入数据模式是固定的,也就是说不考虑“背靠背”的数据输入情况。计算公式为\(800-800\times\frac{80}{100}=160\)

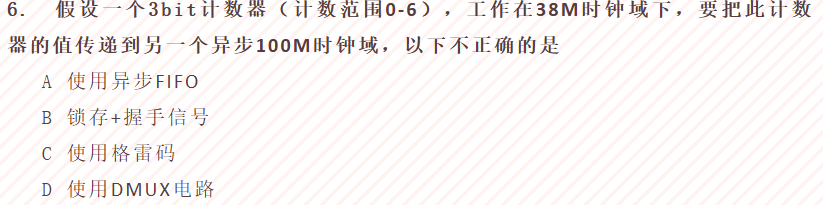

解:C

3bit总共有\(2^3=8\),实际计数范围为0-7,所以使用格雷码时从6-0时会不止一个bit位发生变化,从而导致CDC(Clock Domain Crossing)时多位变化导致亚稳态。

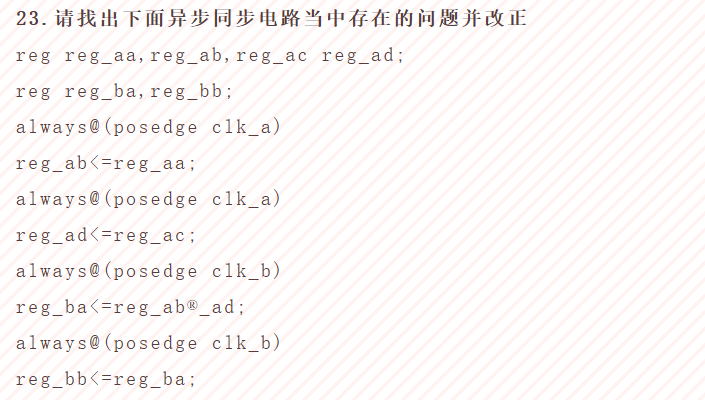

二进制转化为格雷码:二进制的最高位与格雷码的最高位相同,格雷码其余各位为二进制对应位与前一位异或(XOR):

![在这里插入图片描述]()

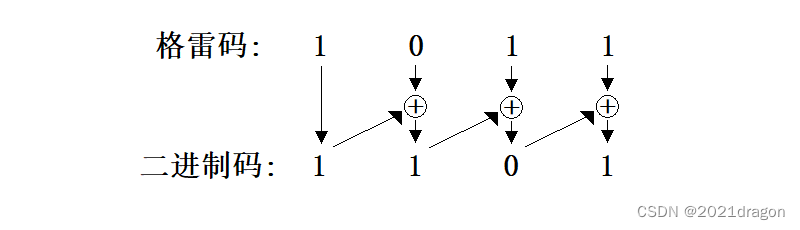

格雷码转化为二进制:格雷码最高位与二进制最高位相同,二进制其余位为格雷码对应位与二进制上一位异或(XOR):

![在这里插入图片描述]()

A. 使用异步FIFO:正确。异步 FIFO(First-In, First-Out)是处理多比特、异步数据流的最常见、最稳健的方法。它使用写时钟域的指针(wptr)和读时钟域的指针(rptr),并通过格雷码同步这些指针,来安全地处理数据跨时钟域传输。

B. 锁存+握手信号:正确。这种方法通常用于传输单次事件或非连续数据。当发送方(38M)有数据准备好时,会发出一个数据有效信号;接收方(100M)看到有效信号后,会锁存数据,并回传一个确认信号。这种方法能确保数据被正确接收,但会牺牲一定的带宽。

D.使用计数器 + DMUX + One-Hot 编码 的方法,DMUX (Demultiplexer) = 解复用器。功能:

- 有一个输入端(一般是数据输入 D)

- 通过选择信号 S

- 把输入送到其中一个输出端 Y[i],其余输出为 0

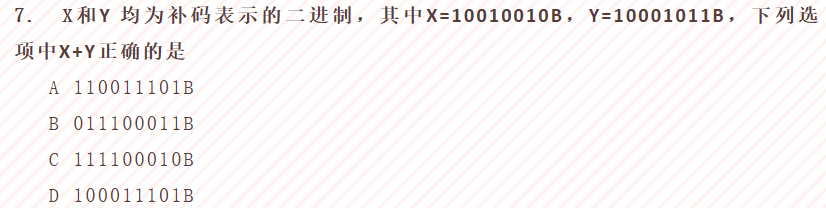

解:D

110010010 (X = -110)

+ 110001011 (Y = -117)

-------------

1100111101

符号位扩展,遇到加法溢出,要 符号位扩展到足够宽度(通常 1 位以上)。扩展时复制符号位,高位补 0 或 1。

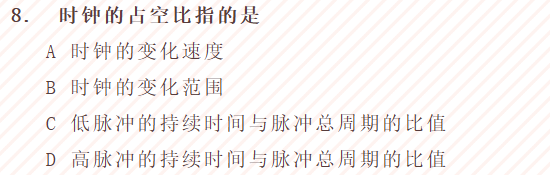

解:D

时钟的占空比指的是:周期性时钟信号中,高电平持续时间与时钟周期总时长的比例。

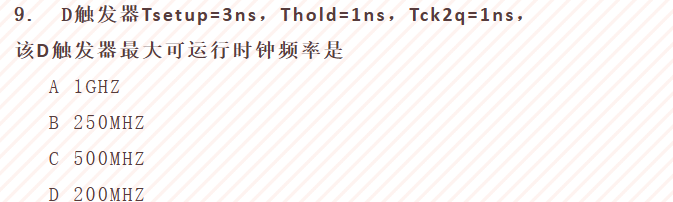

解:B

考虑到建立时间(数据需要比时钟提前达到的时间),\(T_{clk}>T_{ck2q}+T_{setup},T_{clk}>4ns\),所以最大为250MHz。考虑到保持时间(下个数据来的时间比时钟晚到达),\(T_{hold}>T_{ck2q}+T_{comb}\)

解:A

低功耗设计的核心目标为:

-

较低动态功耗(Dynamic Power):减少电路翻转切换次数和切换电容

-

降低静态功耗(Static/Leakage Power):减少晶体管关断时的漏电流

PPA是性能、功耗、面积(Performance、Power、Area)间的权衡。

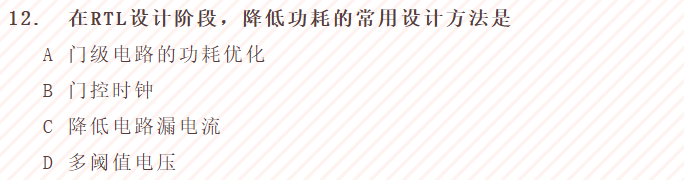

解:A

解:B

因为是在RTL设计阶段,所以可以在编写Verilog阶段可以通过寄存器时钟使能来实现门控时钟。

数字电路功耗主要取决于动态功耗:

其中时钟是全局翻转、活动率几乎为100%的信号,它驱动大量触发器的输入端,即使数据不更新,时钟翻转也会导致触发器和是中暑的动态功耗。门控时钟(Clock Gating)的作用是在电路不需要工作时,直接阻断时钟信号,降低翻转率。

在RTL阶段可以通过时钟使能(Clock Enable,CE)信号:

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

q <= 0;

else if (en)

q <= d;

end

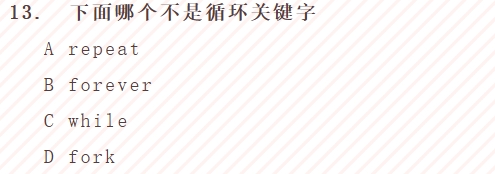

解:D

fork用于并行执行(在Verilog中是并发进程块的开始)。

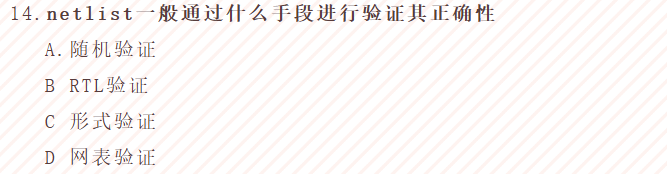

解:C

netlist是综合(Synthesis)之后生成的门级网表文件。为了确保综合后的网表和RTL设计在功能上等价。在行业中通常采用形式验证(Formal Verification)的方法,例如使用等价性检查(LEC,Logic Equivalence Check)。

- A 随机验证 ❌ 这是动态仿真的一种方法,主要用于功能验证,不是验证 netlist 功能等价的主要手段。

- B RTL验证 ❌ RTL验证是在综合前验证设计逻辑,不直接验证 综合后的网表。

- C 形式验证 ✅ 常用的方法,用数学手段自动比较 RTL 和 netlist 的功能是否完全一致,例如 Synopsys Formality、Cadence Conformal。

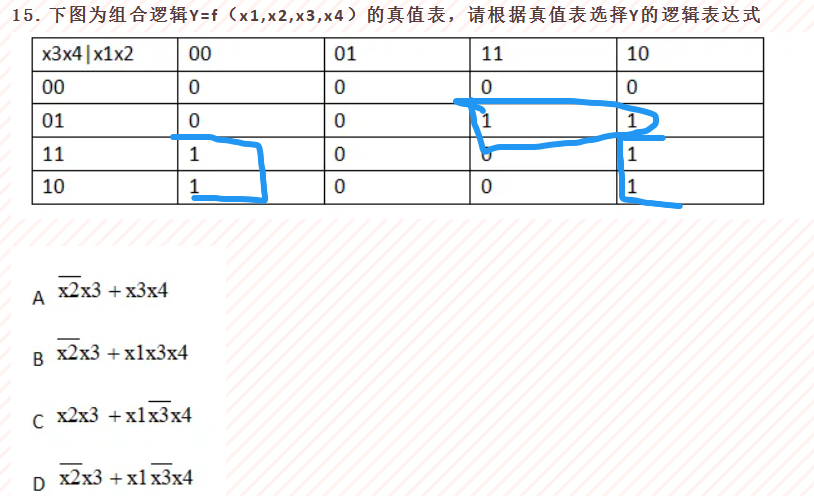

解:D

卡诺图:\(\overline{x_2}x_{3}+x_{1}\overline{x_3}x_4\)

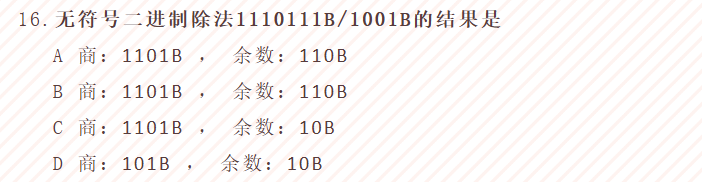

解:C

使用长除法进行计算。

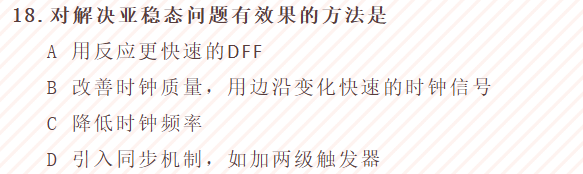

解:B

在组合逻辑电路中,冒险现象(Hazard)是指输入信号变化时,电路的理想输出本应该保持不变,但由于信号传播延时不一致而产生的瞬时错误脉冲。根本原因是:逻辑门存在传播延迟,不同信号路径的延时不同。

多选

解:ABCD

亚稳态产生的原因是:当异步信号在触发器采样的时间窗口(建立/保持时间)内发生变化时,触发器可能无法在一个时钟周期内稳定到 0 或 1,进入不确定的中间状态,这就是亚稳态。

A.有效。 更“快”的触发器通常具有更短的时间常数 \(\tau\),也就是说能更快地从亚稳态恢复到稳定态,从而在给定的等待时间内降低未恢复的概率。

B.有效。 时钟沿越陡(上升/下降时间越短),对建立/保持窗口的不确定性越小,从而减少样本在不稳定时刻被采样的概率。良好的抖动和干净的时钟也能降低亚稳态发生率。

C.有效。降低接收端或发送端的活动频率,会直接减少“有问题的采样事件”发生的速率,进而降低亚稳态发生的频率。

D.有效。在接收时钟域对异步信号使用两级或多级 DFF 串联的同步器,可以将亚稳态传播到下一级并指数级降低未恢复的概率:这是工程实践中的标准做法。

解:BC

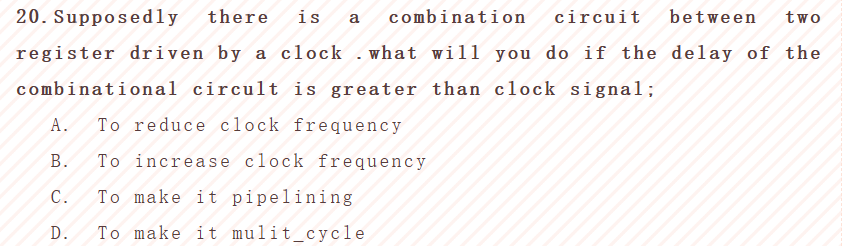

解:ACD

A. To reduce clock frequency (降低时钟频率) ✅

- 降低频率 = 增加时钟周期,可以让组合逻辑延迟小于等于一个时钟周期。

- 代价:系统性能下降。

B. To increase clock frequency ❌

- 增加频率将缩短时钟周期,反而加重时序违例,更不可能。

C. To make it pipelining (流水线化) ✅

- 在组合逻辑中间加寄存器,分成多个时钟周期完成,减少每级组合延迟。

- 性能提高(频率可更高),但延迟(latency)增加。

D. To make it multi_cycle (多周期路径) ✅(在特定场景下)

- 如果逻辑本身不需要每个周期都出结果,可以允许该路径跨多个时钟周期完成。

- 常用于非关键实时数据通路

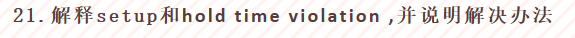

简答

解:数字电路里,触发器对输入信号有时序要求:

- 建立时间(setup time):D输入必须在时钟上升沿到来前保持稳定一段时间,否则触发器可能触发错误数据或进行亚稳态。

- 保持时间(hold time):D输入在时钟沿到来后,仍需保持稳定一段时间。

| 类型 | 发生条件 | 常见原因 | 解决办法 |

|---|---|---|---|

| Setup violation | 数据太慢,采样时数据未稳定 | 组合逻辑太长、频率过高、时钟偏斜 | 降频、优化逻辑、加流水线、更快单元、调时钟 |

| Hold violation | 数据太快,采样后立刻改变 | 路径过短、负时钟偏斜 | 加延时 buffer、调整布线、调时钟、用慢单元 |

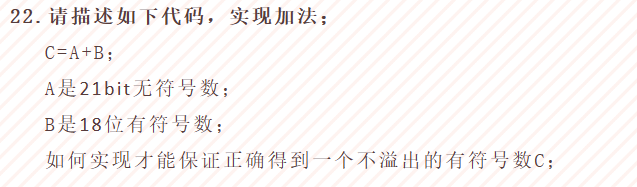

解:

- 对齐位宽:A(21位无符号数)扩展到22位,并在高位补0;B(18位有符号数)扩展到22位,并在高位做符号扩展(即复制符号位)。

- 加法运算

wire [20:0] A; // 21-bit unsigned

wire signed [17:0] B; // 18-bit signed

// 扩展

wire signed [21:0] A_ext = {1'b0, A}; // A 扩展为 22 位,最高位补 0

wire signed [21:0] B_ext = { {4{B[17]}}, B }; // B 扩展为 22 位,符号扩展

// 加法

wire signed [21:0] C = A_ext + B_ext;

解:

跨时钟域直接取信号 → 存在亚稳态风险

reg_ab和reg_ad位于clk_a时钟域- 你直接在

clk_b时钟域里读取reg_ab和reg_ad,这样会导致亚稳态(metastability)问题,因为clk_a和clk_b没有固定相位关系,取到的数据可能在建立/保持时间内变化,导致寄存器输出不稳定,从而在仿真和硬件中出现不可预测错误。

在 FPGA/ASIC 设计中,跨时钟域的数据必须经过多级寄存器同步。

- 单比特信号 → 两级打拍同步器

- 多比特信号 → 需用握手协议(FIFO、Gray code 等)

// 声明

reg reg_aa, reg_ab, reg_ac, reg_ad;

reg reg_ba, reg_bb;

reg reg_ab_sync1, reg_ab_sync2;

reg reg_ad_sync1, reg_ad_sync2;

// clk_a 域(源信号)寄存

always @(posedge clk_a) begin

reg_ab <= reg_aa;

reg_ad <= reg_ac;

end

// 跨域同步 (clk_b 域) — 两级同步器

always @(posedge clk_b) begin

reg_ab_sync1 <= reg_ab;

reg_ab_sync2 <= reg_ab_sync1;

reg_ad_sync1 <= reg_ad;

reg_ad_sync2 <= reg_ad_sync1;

end

// clk_b 域逻辑

always @(posedge clk_b) begin

// 假设这里是异或操作

reg_ba <= reg_ab_sync2 ^ reg_ad_sync2;

reg_bb <= reg_ba;

end

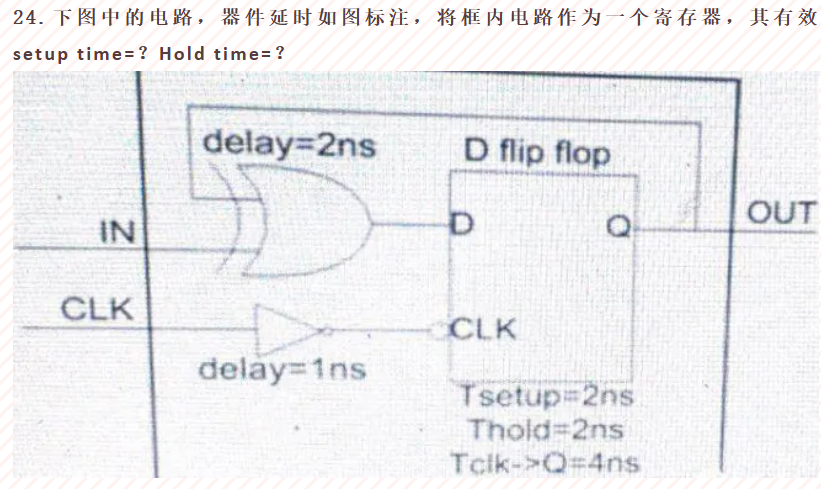

解:

setup time时间:数据需要比时钟早到达的时间\(T_{clk}+T_{skew}>T_{c2q}+T_{comb}+T_{setup}\),对于原D触发器而言,数据信号需要比时钟信号提前2ns到达,时钟延时1ns,数据延迟2ns,所以外部需要更大的保持时间裕量,所以\(T_{setup}=2+2-1=3ns\)

hold time时间:同理,下一个时钟比数据晚的时间\(T_{hold}=2+1-2=1ns\)

浙公网安备 33010602011771号

浙公网安备 33010602011771号