规范化操作 中兴使用Allegro来高效完成复杂服务器主板的案例(转)

转载于 : https://www.mr-wu.cn/zte-zhong-xing-shi-yong-allegro-lai-gao-xiao-wan-cheng-fu-za-fu-wu-qi-zhu-ban-de-an-li/

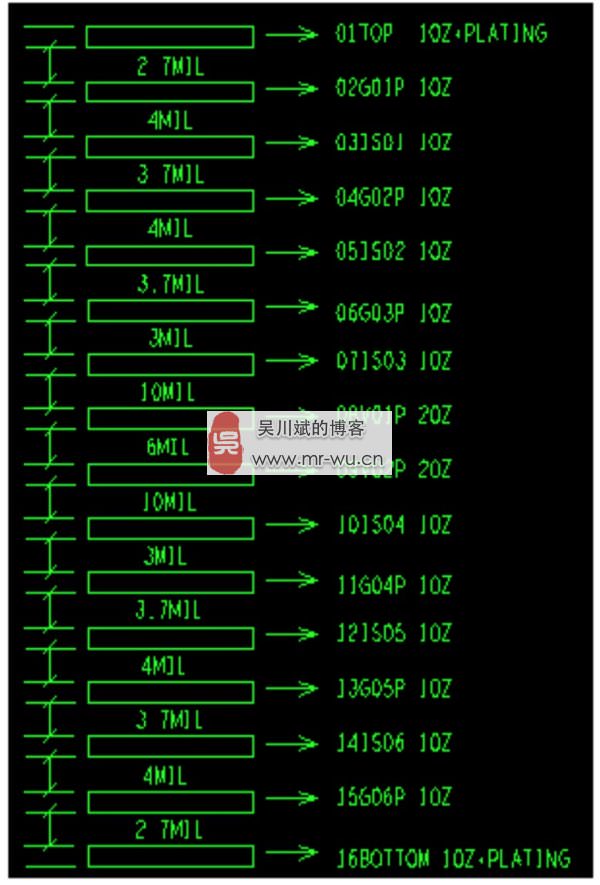

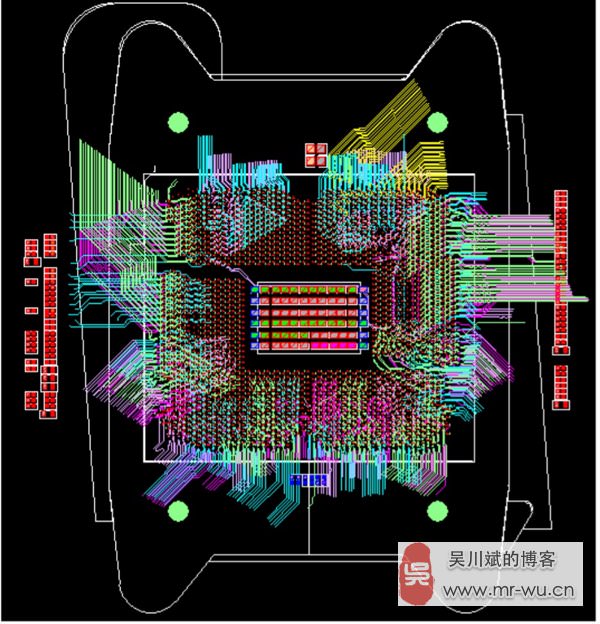

中兴RAST服务器主板采用4片最新的INTEL Brickland 芯片设计,器件数量达到6000多个,焊盘数量超过 30000多个,单板设计为16层,是一块极为复杂的 服务器板。ALLEGRO针对复杂单板的各个设计阶段 都提供了方便有效的设计工具,让我们的设计更加 简便高效,整个设计过程如行云流水一般流畅。

布局阶段

使用快速布局工具提高设计效率

自动布局前期设置

使用自动布局功能前,需要进行一些设置。

导入网表

。。。

放置器件

所有器件放置在板框外面

。。。

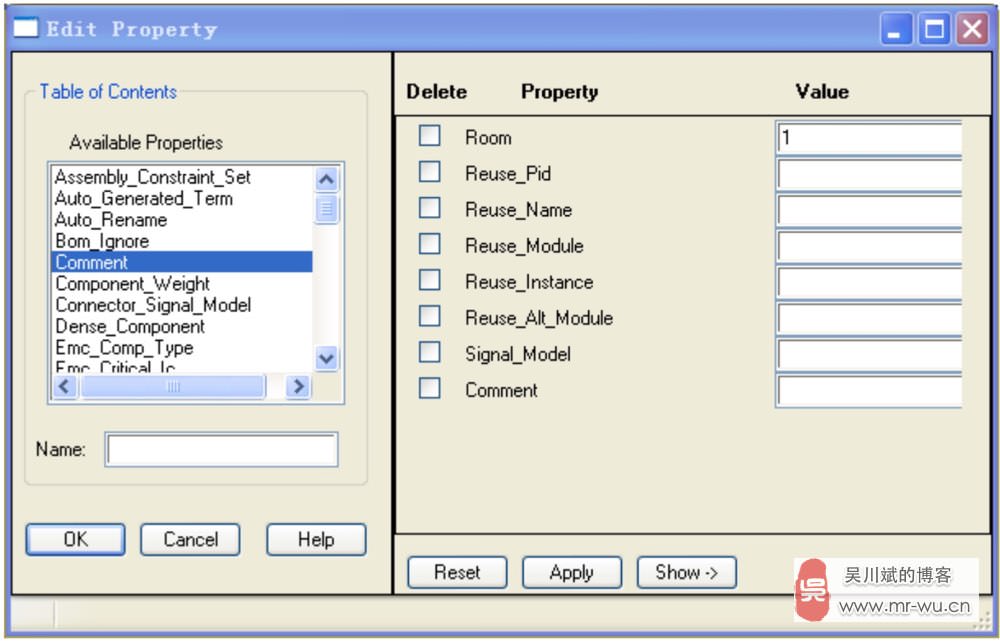

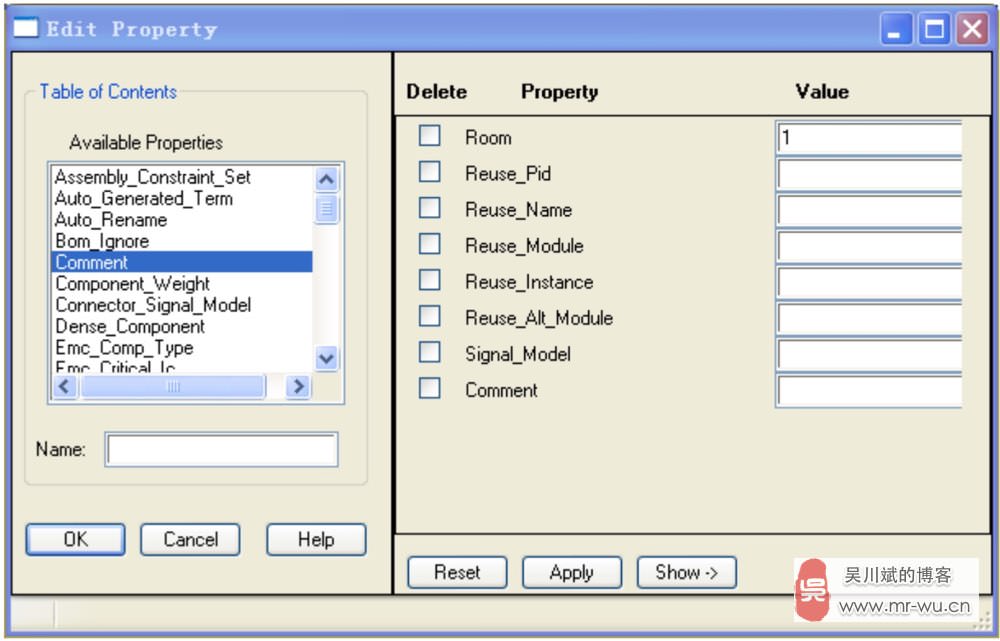

添加room属性

选中所有器件,给Comps添加room值为1

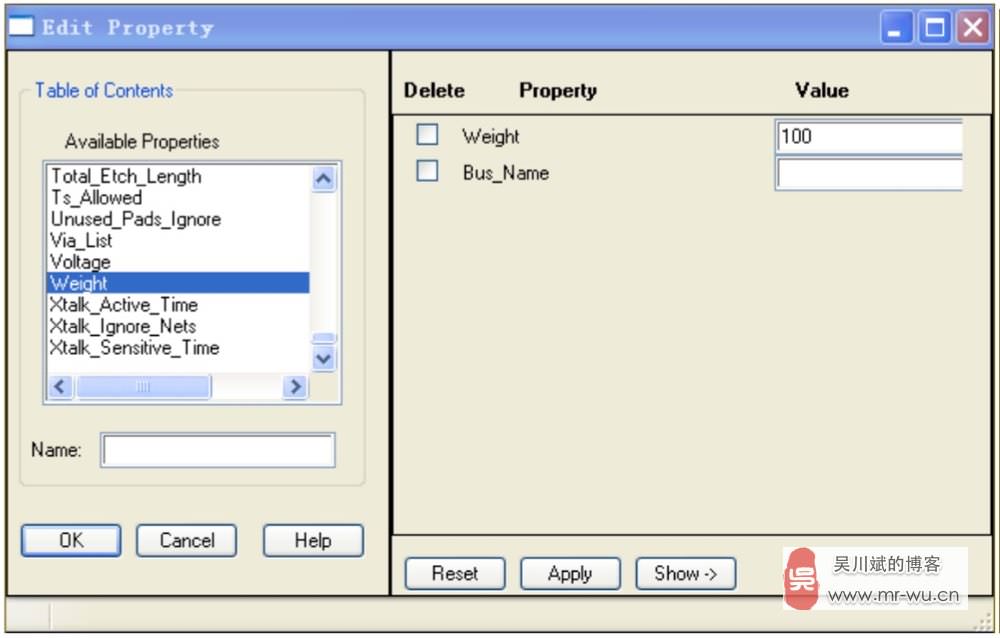

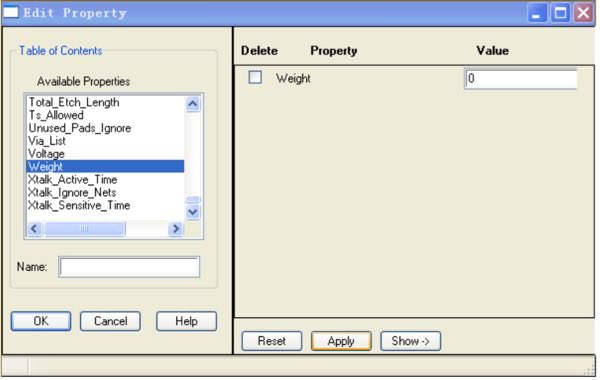

设置weight

选中所有的网络,添加weight属性,值为100,添加后挑出所有的电源、地网络,weight值 设置为0。自动布局时,weight值越大,越优先放置最近。

添加room属性

选中所有器件,给Comps添加room值为1

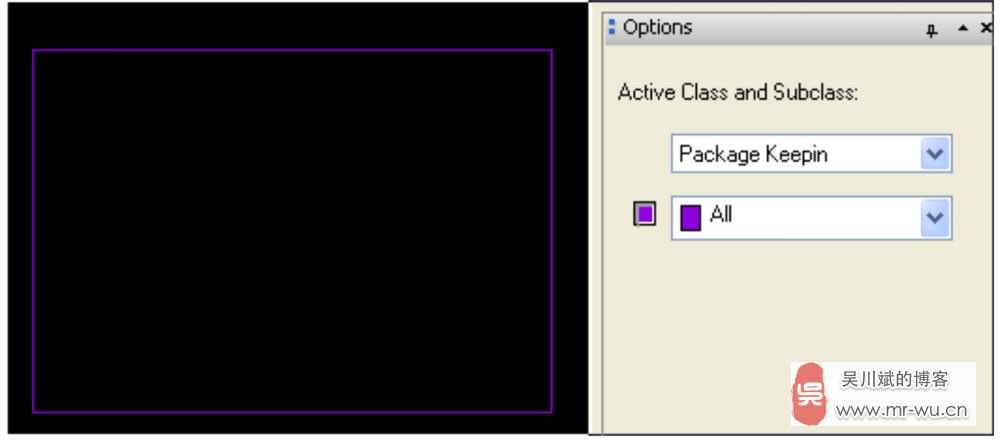

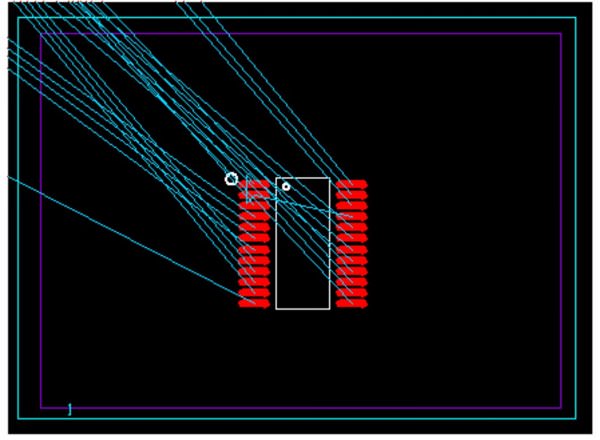

添加自动布局区域

在板框外面添加PackageKeepin属性的外框,作为自动布局的有效区域

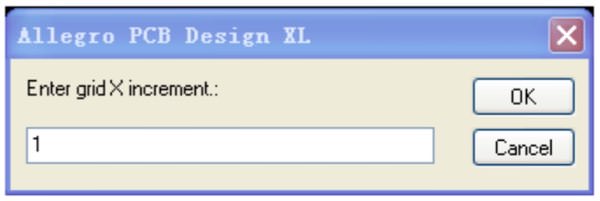

设置栅格

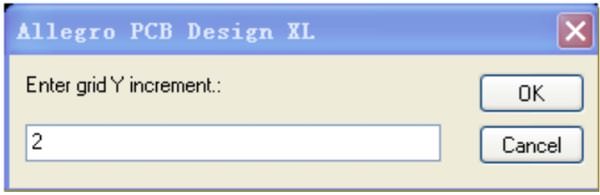

设置自动布局栅格,控制自动布局时的器件间距,栅格的大小根据器件的大小选择,布局过 程中可以根据需要修改。设置路径Place—>Autoplace—>Top Grids(Bottom Grids),出现如下 对话框:

完成栅格设置之后,命令输入栏会提示 Enter a gridpoint,鼠标点击自动布局 区域的左下角,选择原点。设置好的 栅格可以选择显示,也可以不显示。

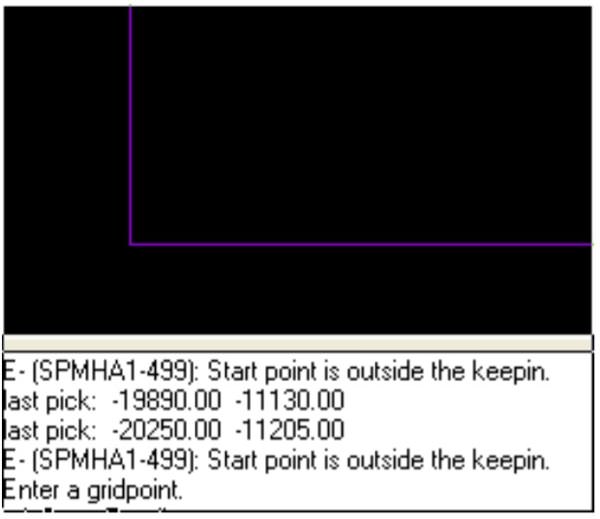

给room区域添加属性

在top_room层画一个比Package Keepin略大一些的区域。然后命名该区域,命名路径 Add->Text,点击该room边框,然后输入room的名字1。跟前面的设置Comps添加room值1, 两处相一致。至此,完成了自动布局前的设置,在整个自动布局期间不需要再做其他设置了, 这个设置好了可以反复使用。这一点设置时间对于具有6000多个器件的服务器单板来说可以 忽略不计

使用自动布局实现快速布局

挑选需要布局的器件

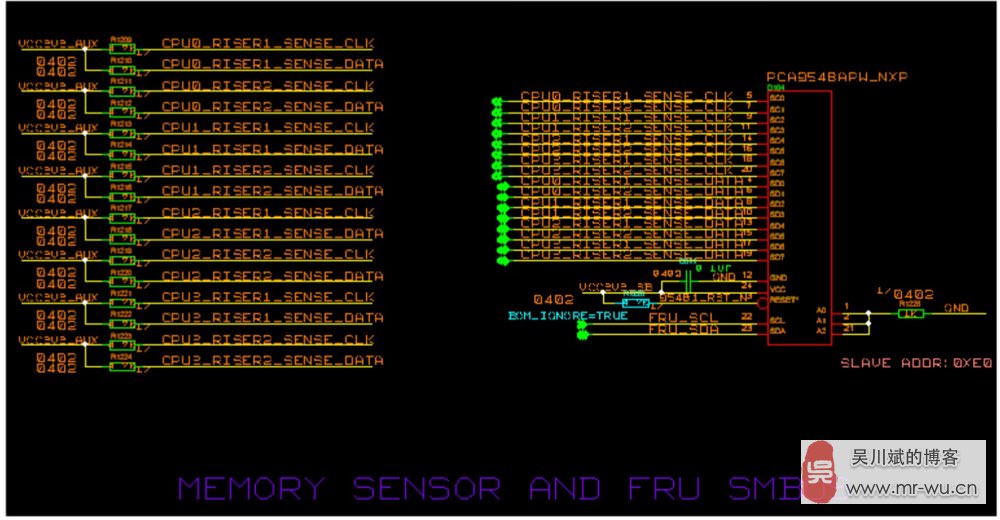

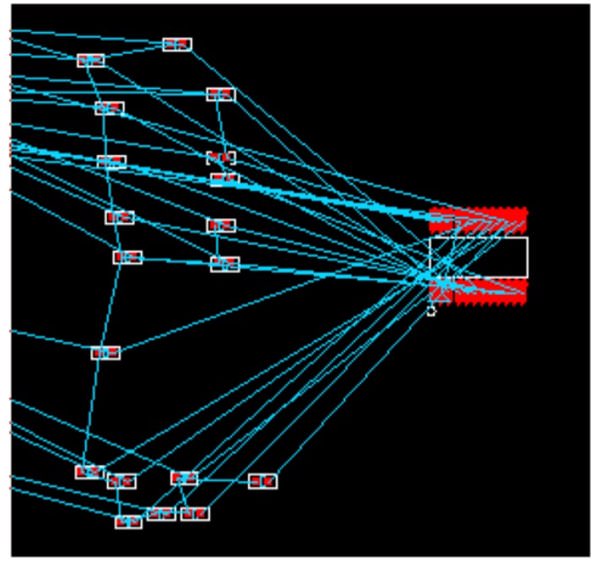

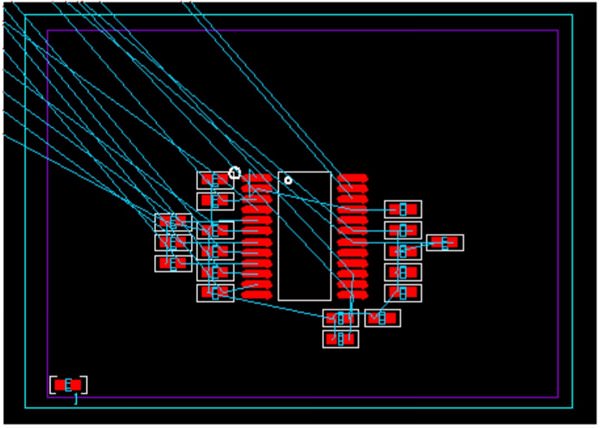

用Project Manager把原理图和PCB相关联,进行交互操作。在原理图中把要进行布局的芯 片及其周边阻容器件按照Group或者Module模式选中。

移动器件

把原理图中选中的器件整体在PCB里面从其他期间当中移出来。

摆放主要芯片

在移出的那些器件中,主要的芯片移动到自动布局区域,其他阻容器件从PCB中删掉

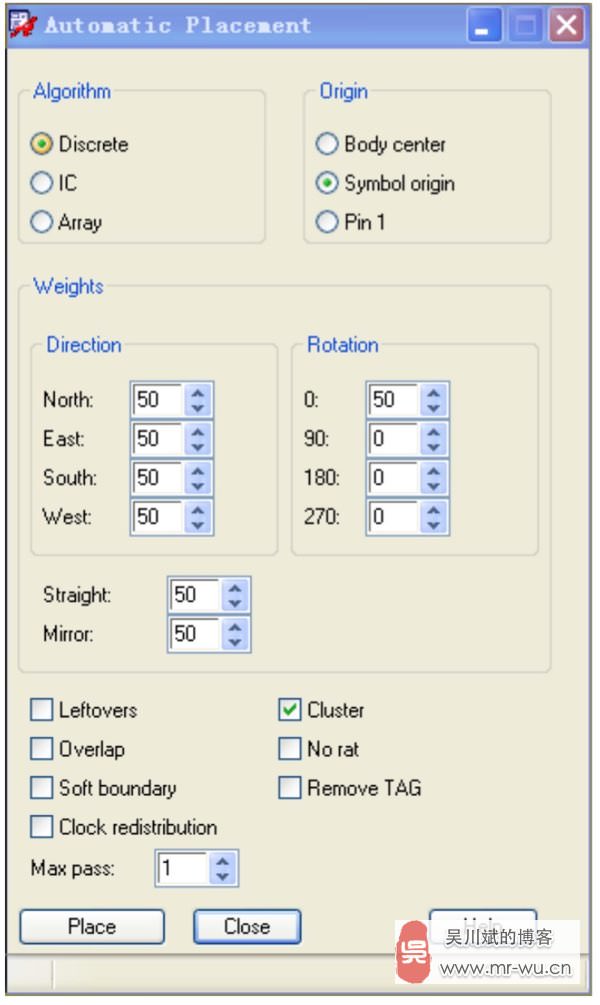

设置自动布局参数

接下来设置布局参数,这里的参数设置一次,后面就 能直接使用,也可以根据自动布局的主芯片不同, 改变参数。参数设置路径为Place—>Autoplace—> Parameters,出现如下对话框。

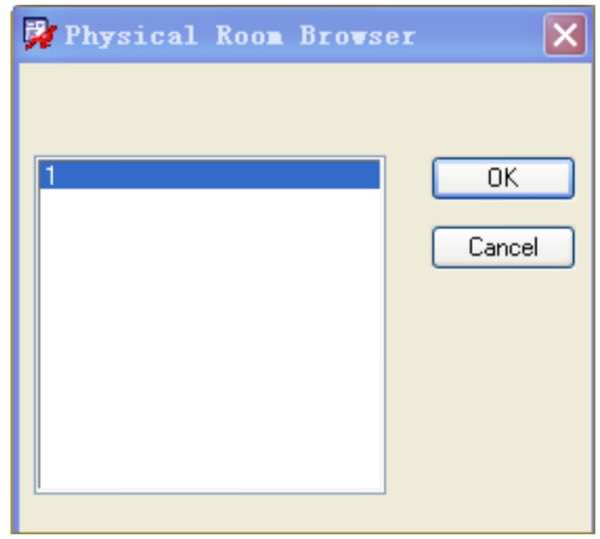

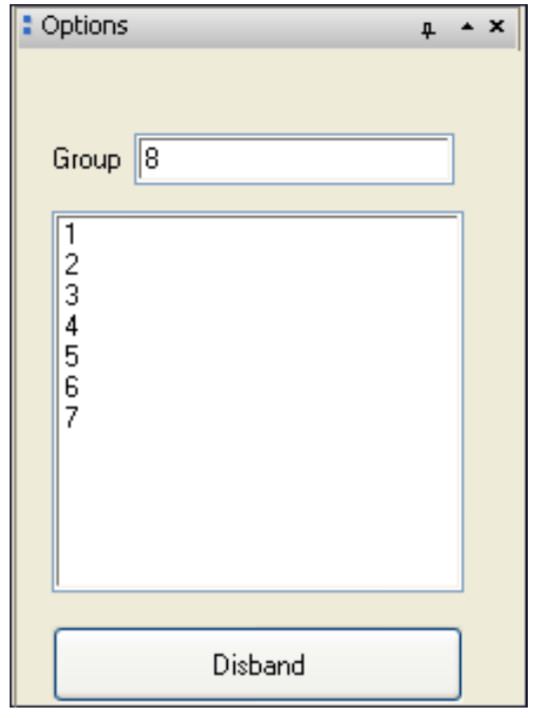

选择自动布局Room

参数设置完成之后,就可以按照Room方式布局了。 Place—>Autoplace—>Room,图11 按照room自动布局路径。

布局优化

对一块电路完成自动布局后,根据需要进行优化,然后做成一个Group,放进板框里面。 设置Group的路径为Edit—>Groups,为当前要创建的Group起一个名字,选择需要的器件, 就完成一个Group的创建了。做成Group后不但可以整体移动,确保不会混淆不同电路之间的器件;采用User Pick方式移动,无论如何旋转, 同一Group里面的器件相对位置都不会发生 变化,对高密度复杂服务器主板的设计作用非常大。

自动对齐

自动布局后,如果芯片附近的阻容器件比较多,手动调整可能比较费时间,这个时候采用自动对齐的功能,可以大幅节省时间。执行Setup->Application Mode->Placement Edit,进入布局模式,点住鼠标左键框选需要对齐的器件,然后点击鼠标右键弹出命令选项,再用鼠标左键点击Align components,选中的器件就会自动对齐。

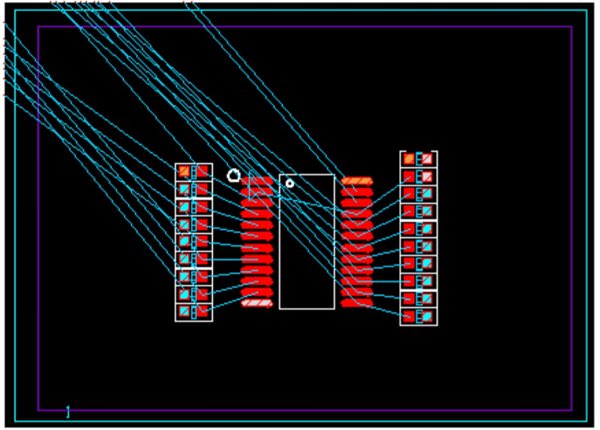

相同模块拷贝

经过自动布局、自动对齐、手工调整完成一个一组器件的布局,然后把这组器件做成一个 Group,方便整体移动。如果相同的电路模块有多个,那么我们就不需要对每个电路模块都重 复这个过程。采用布局拷贝的功能,可以轻松完成多个相同模块的拷贝,极大地提高布局效率。

- 创建模板

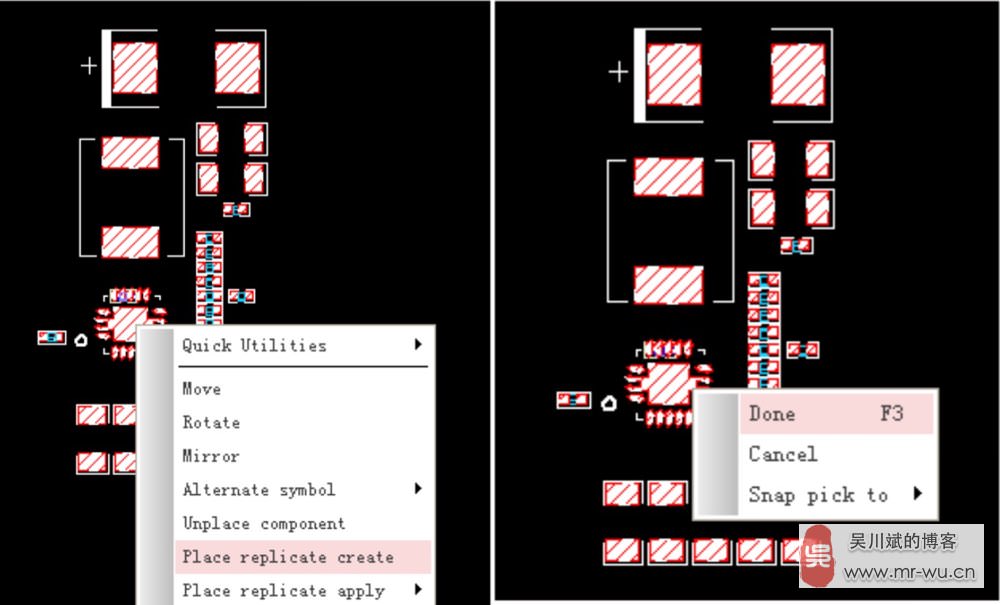

选择器件

用鼠标左键框选需要创建模板的一组器件,然后点击鼠标右键弹出命令选项,再用鼠标左键选择Place replicate create命令 ,再次点击右键弹出命令选项,再用鼠标左键选择Done命令 ,完成器件选择。

选择原点

完成器件选择后,命令输入栏会提示Pick origin or use RMB for Snap to,点击左键选择电路 模块的原点‘

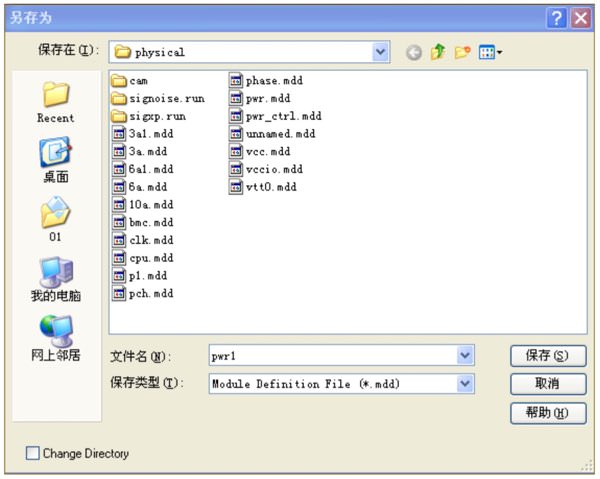

保存模块

选择好模块原点后软件会弹出一个对话框,输入模块名称后保存到需要的路径下,以便后续 调用。

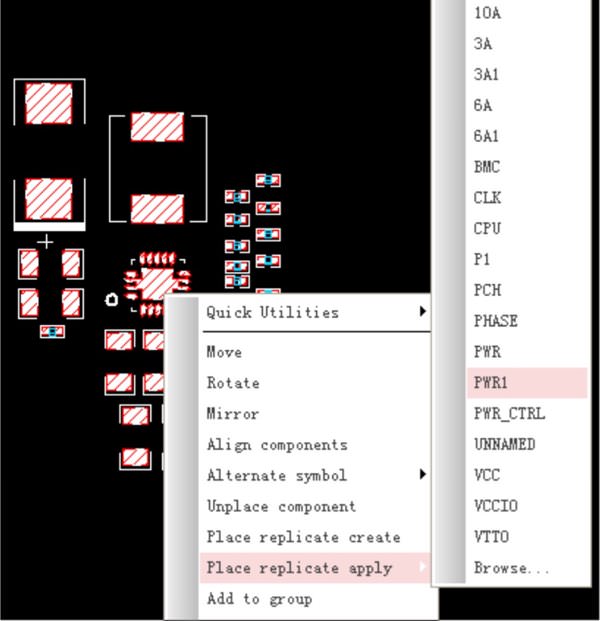

- 拷贝模块

在布局模式下,左键框选待拷贝的一组器件,点击右键弹出命令选项,左键点击Place replicate apply在可选模板中选择需要使用的模板,点击左键即可得到与模板一致的布 局。如果所选择的模板已经完成布线,可以连通布线一起拷贝,不但成倍提高

设计效率,还对设计标准化非常有利。

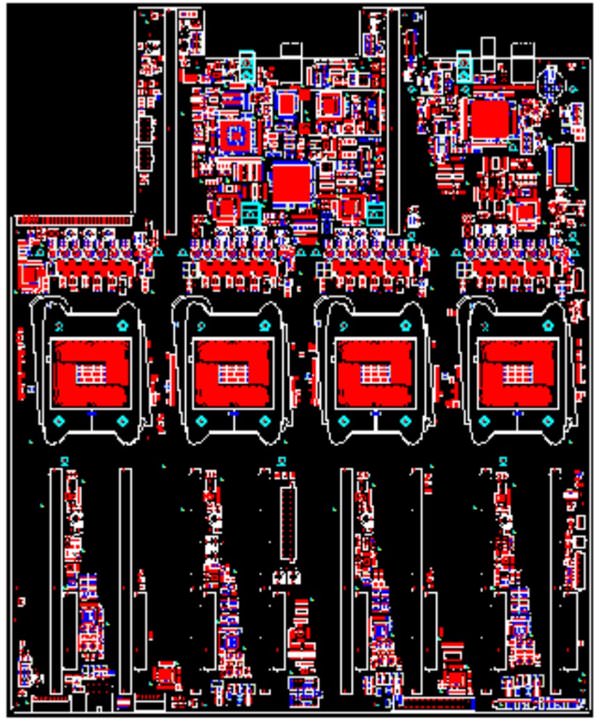

由于服务器主板上存在四个相同的CPU、 八个相同的内存子卡插座、大量相同的电源模块,通过布局拷贝可以成倍地提高设计效率,极大地提高设计质量。

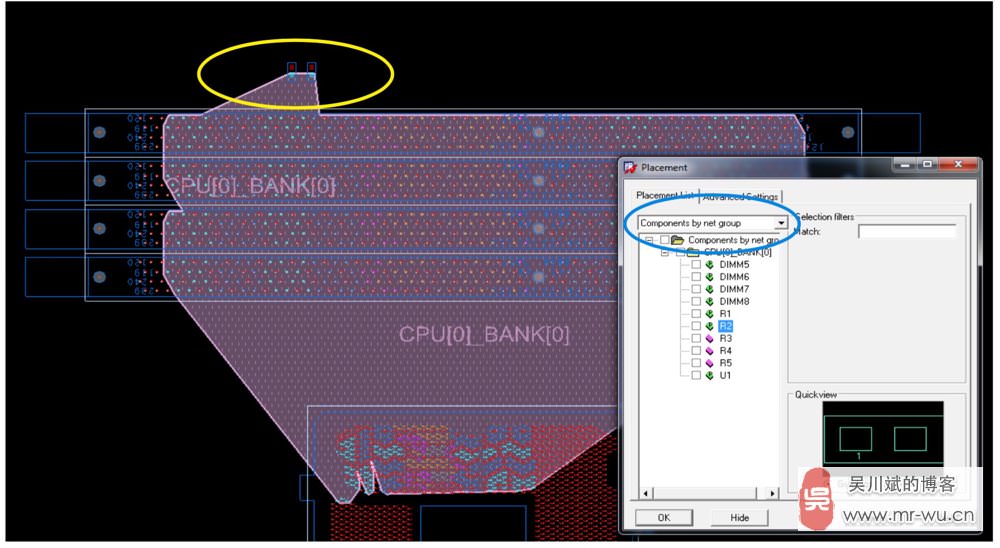

布局阶段 Net Group功能探索

- Cadence最新的16.6版本中的Net Group也可以帮助提高布局&布线的质量和效率

- Net Group能够在PCB设计界面中,直观的看到原理图设计意图的功能

- Net Group是一种新的属性可以在原理图设计中设置,同样也可以在Allegro中的CM中进行设置

- Net Group能够帮助提高布局的准确性和效率

- Net Group同样能够帮助提高布线的合理性及加速走线规划

- Net Group能够在PCB设计界面中,直观的看到原理图设计意图的功能

Net Group能够帮助提高 布局的准确性和效率

布局小结

针对具有6000多个器件的复杂服务器主板的布局,如果软件没有提供一系列高效的设计工具,布局工作量是非常庞大的。

ALLEGRO提供了自动布局、自动对齐、相同模块拷贝、创建Group等大量方便高效的设计工具,这些设计工具互相配合、环环相扣,不但成倍地提高了设计效率、极大地提高的单板的整洁性,对提高设计质量也非常有利。

新的Net Group的功能在以后的布局设计中也能够提升我们的布局的质量及效率。能使PCB工程师更加合理的有效的进行布局布线

布线阶段

- 过孔扇出

Allegro提供了丰富多样的过孔扇出功能,能够有效满足各种BGA的扇出需求,对于提高设计效率十分有重要。

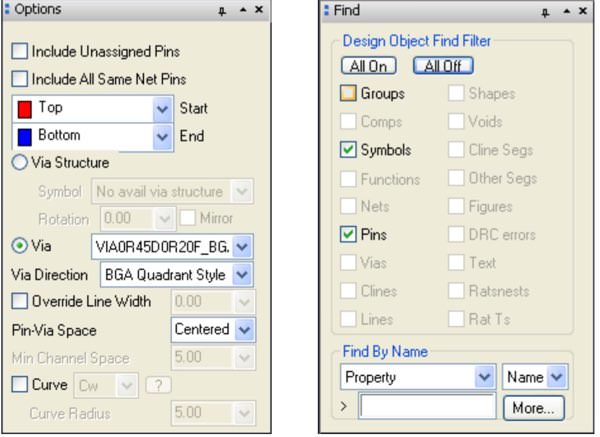

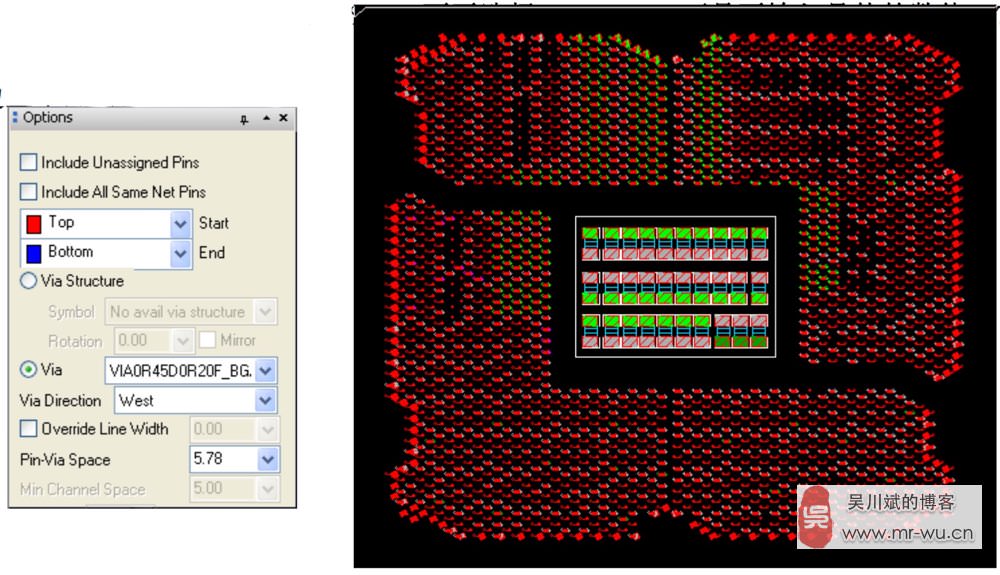

1.过孔扇出功能介绍

执行Rout->Create Fanout,在Options界面,可以选择过孔的类型,扇出的方向,过孔距离焊 盘的位置,扇出线段的宽度,无网络管脚是否扇出等,选择内容非常丰富。

在Find界面,可以选择按照按照Groups、Symbols、Pins扇出,实际应用中按照Symbols扇出和按照Pins扇出经常可以互补,

完美地解决扇出问题。完成上述设置后,左键点击需要扇出的对象即可完成过孔扇出。

#1

- 过孔扇出案例

? 扇形扇出

这是最常见的BGA扇出方式,过孔处于周边管脚的居中位置,线宽采用默认,我们常见的 BGA芯片都可以采用这种方式扇出。

? 特殊管脚排列形式的BGA

Intel出品的Jasper、Romley、Grantley等服务器处理器都是采用特殊的管脚排列形式, Brickland也不例外,这种BGA不能采用扇形扇出的方式进行过孔扇出,需要根据其封装特点, 灵活运用ALLEGRO提供的扇出方式。

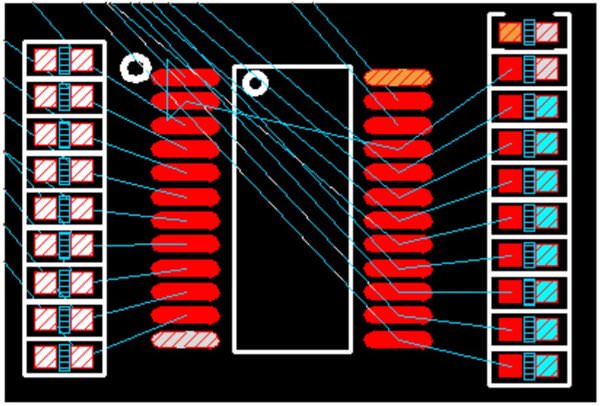

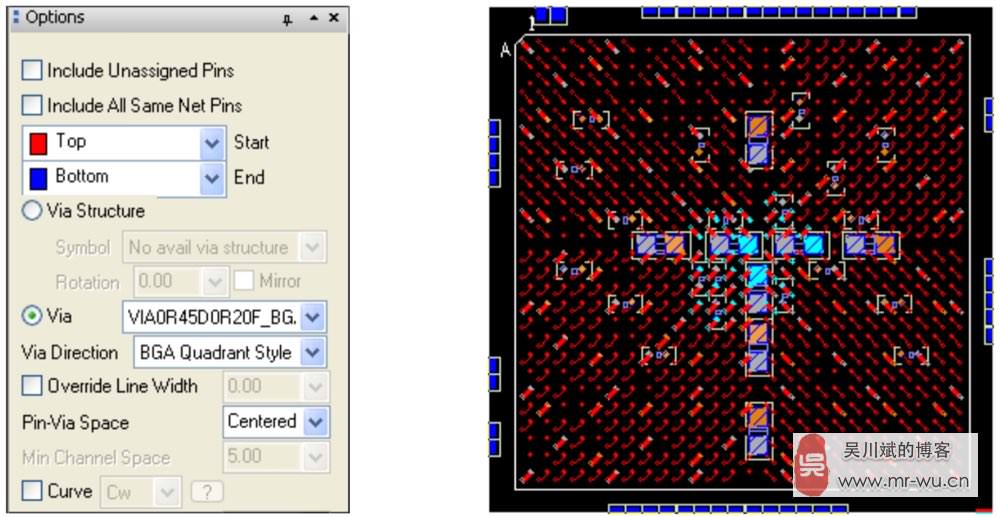

Brickland过孔扇出

根据Brickland过孔排列方式,Via Direction分别选择West和East进行芯片左半部分和右半部分管脚的扇出。同时,Pin-Via Space不再选择Centered,而是要输入具体的数值5.78。 这样的设置可以确保过孔处于周边三个焊盘的居中位置。

添加封装补偿

? 封装补偿文件

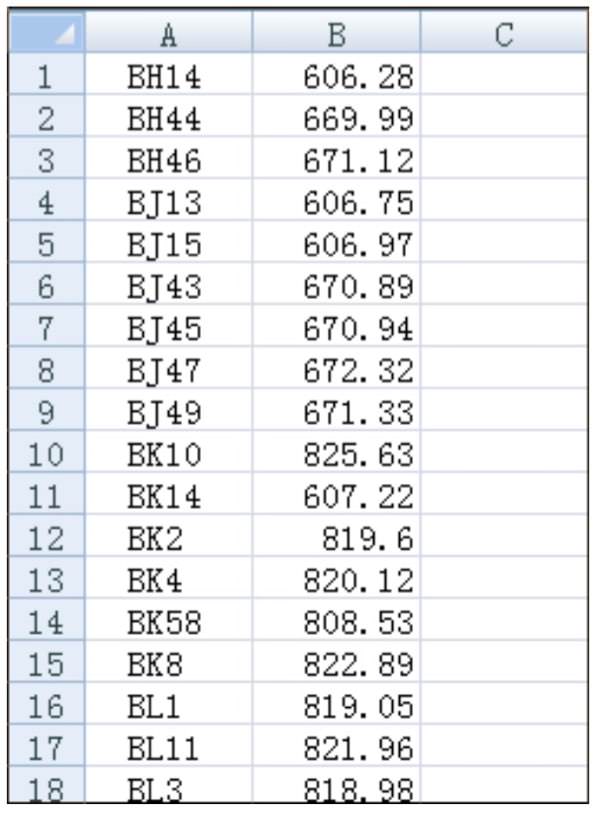

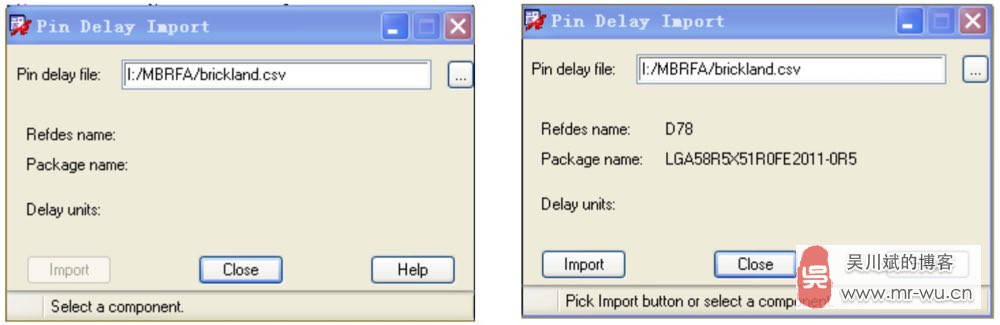

芯片厂家提供的封装补偿文件通常是.xlsx格式的,将源文件编辑成左边一列为管脚名、右边 一列为对应的封装长度的格式,然后文件另存为.csv格式。我们这块服务器主板上的CPU和背 板插座需要进行封装补偿,针对每一种器件制作一个封装补偿文件。

添加封装补偿

执行File->Import->Pin delay import,在跳出的对话框中选择需要的文件,根据对话框最下面的提示,选定需要添加封装补偿的器件,器件被选中后就会高亮显示,然后按照提示把封装补偿数据添加到器件上,对于四片Brickland芯片,需要重复操作四次可以全部添加完成。

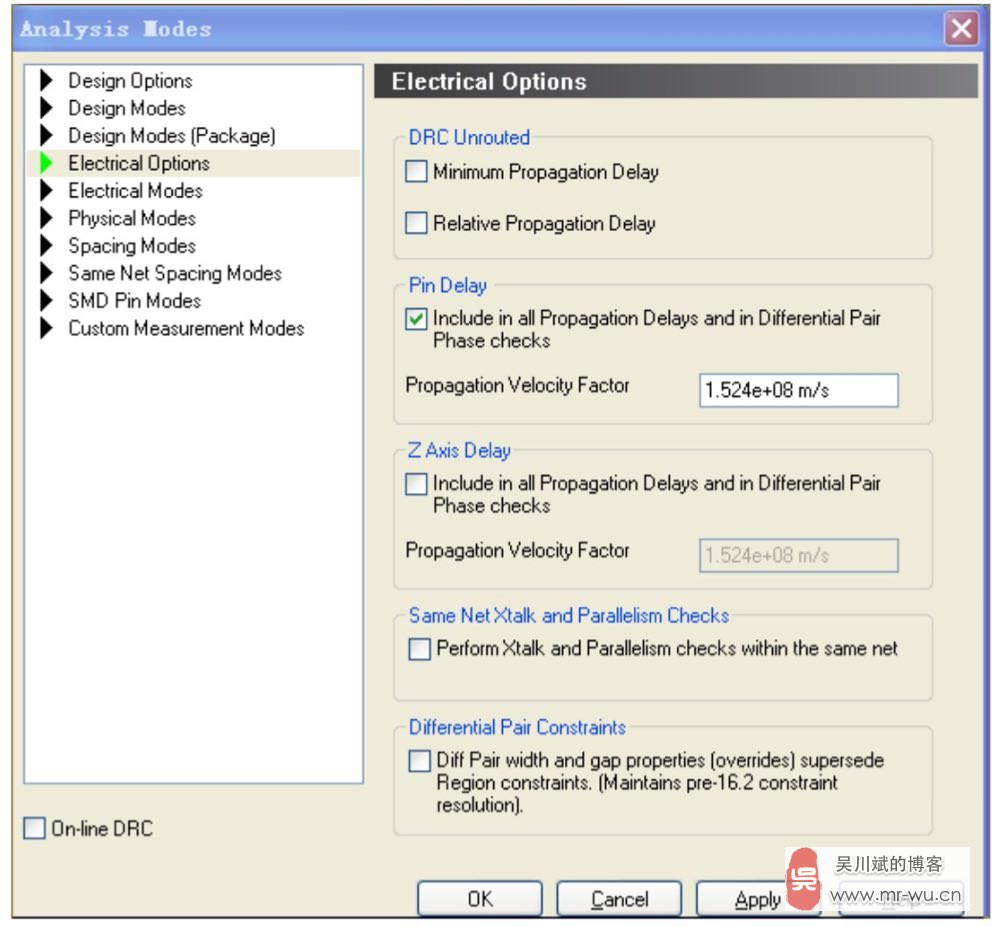

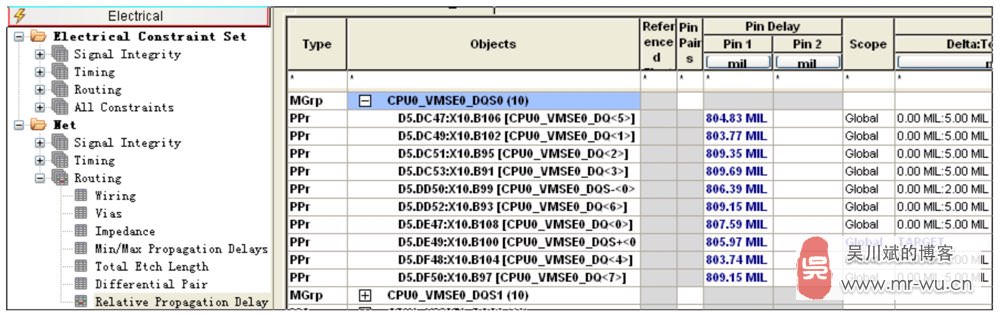

约束管理器设置

打开约束管理器,执行Analyze->Analysis Modes,打开Electrical Options页面,勾选Pin Delay下面的方框,添加的封装补偿数据才会应用到等长调整中。

封装数据显示

在约束管理器里面打开等长约束,可以直观的看到封装补偿数据。

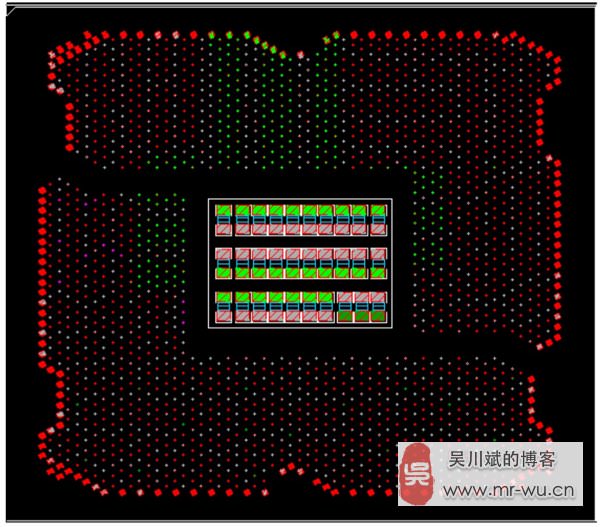

布线拷贝

与布局阶段的相同模块拷贝一样,布线阶段的相同模块拷贝极大地提高到了设计效率,是我们非常喜欢的一项实用功能。ZTE RAST服务器单板上有四片相同的Brickland芯片,相对应的就有四组(每组两个插座)相同的内存插座,四路专供Brickland实用的VCORE电源、VSA电源、VTT电源,四路专供内存插座使用的电源,还有大量采用相同模块的外围电源。 这么多相同电路模块,可以充分发挥Allegro提供的强大拷贝功能,对这块极为复杂的服务器主板设计效率的提升起到举足轻重的作用。

? 相同模块布线拷贝

完成一个电路模块的全部或者部分布线后,就把它做成一个模板保存起来。与布局阶段创建 模板相比,只增加了一个步骤,就是在执行Done命令之前选择走线、过孔、铜皮等,这样做 出来的模板就包含了相关布线元素了。

其他相同的模块就可以拷贝这个做好的模板了, 具体方法与布局阶段完全一样,拷贝完成后在原有的Group里面增加新拷进来的布线元素,成为一个新的整体,极为方便地在板上移动。 按照相同模块拷贝的方式一次性拷贝布局布线,与先拷贝布局,然后再执行Edit->Copy拷贝布线相比有一个明显的优点:所有布线元素自动附上对应的网络名称,不需要任何认为干预,一步到位。我们这块服务器主板上的绝大部分电源模块都 可以按照相同模块拷贝的电源模块,每一种模块 都只需要完成一个模块的布线,其余的全部通过拷贝完成,提高设计效率的作用相当可观。

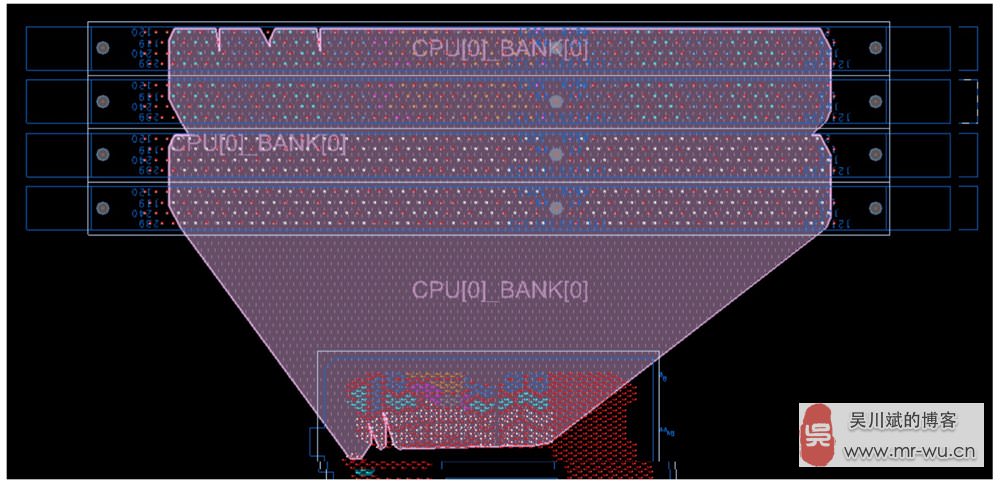

Brickland模块拷贝

如前所述,我们板上一共有四片Brickland芯片,这些正是这块服务器主板的核心部分。 Brickland的主要高速网络是SMI、PCIE3.0、QPI(9.6G),其中SMI网络在内存子卡上转换成 DDR3网络。我们把其中一片Brickland上面的高速网络线按照一定顺序全部拉出BGA封装外面,然后以此为模板,按照模块拷贝的方式拷贝到其他三片Brickland芯片,这样就节省了其他三片Brickland芯片出线的时间了。这些拷贝的走线顺序全部不需要改动,PCIE和QPI的走线层根据交叉情况可以进行适当调整,SMI的走线层完全不需要调整。

内存插座SMI线模块拷贝

如前所述,本板有四组内存插座,主要连接SMI总线,然后在子卡上转换成DDR3总线连接内 存条。每一组内存插座上面的SMI总线与对应的Brickland 的连接关系是完全一致的。所以,只要完成一组内存插座 的SMI网络拉出插座外面,其他三组的SMI网络出线方式就 可以按照模块电路拷贝的方式拷贝过来,节省了大量的时间。

完成电源模块、CPU、内存插座的相同模块拷贝之后,这块服务器 主板的关键网络布线已经初步完成。对于QPI和SMI网络,由于两端 器件都已经按照合理的顺序拉出线,只要把两端的线连接起来就可以连通。

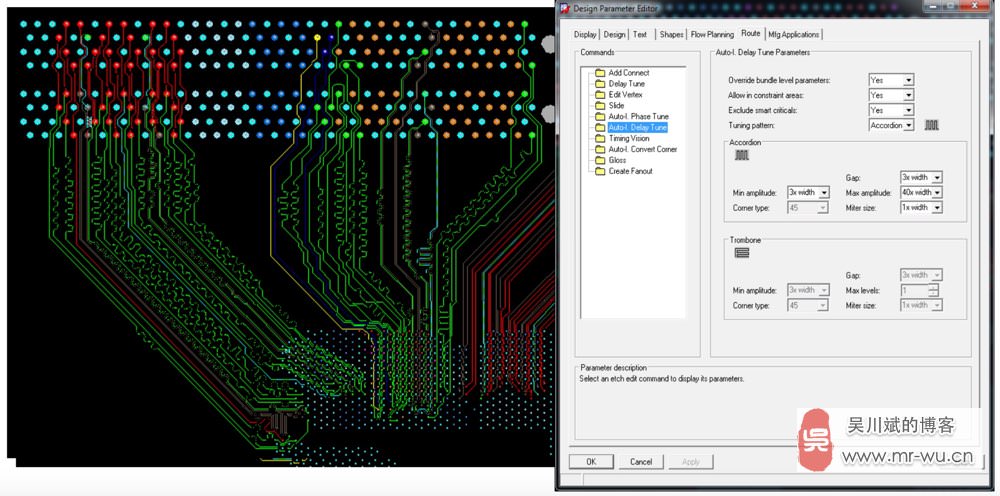

等长绕线

Allegro提供了非常简单高效的等长绕线工具,执行Route->Slide,Options界面就可以进行相关设置了,设置完成后用鼠标拖动信号线,画图界面的左下方就会出现一个实时更新的状态条,上面用数字显示该信号线与设计长度约束的差距,用颜色显示长度是否达到设定的长度范围,只要显示绿色就表示长度已经符合设定的要求,如果想精益求精就让上面的数字趋近于0。可见,等长绕线的过程中并不需要打开约束管理器,只要在画图界面简单操作就可以完成等长绕线了。

。。。

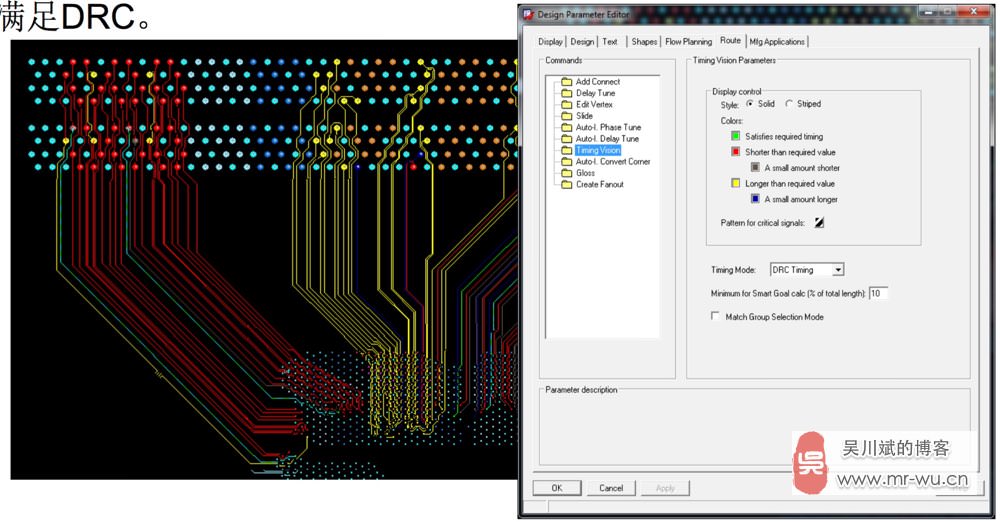

Time Version 功能研究

Time Version是一种及时的直观的方式来显示Match Group的 Delay的情况,能帮助PCB工程师直接通过颜色来判断Delay是否 满足DRC。

AiDT功能研究

AiDT是Allegro中提供的自动绕等长的功能,该功能帮助PCB工程师从繁琐的手动调等长的工作中解放出来。

背钻设计

ZTE RAST服务器主板上大量PCIE3.0走线,无法保证所有PCIE线的残桩都符合要求,对于残桩不符合要求的地方就需要进行背钻。 Allegro提供了非常完善的背钻设计工具,帮助我们高效完成了背钻设计。

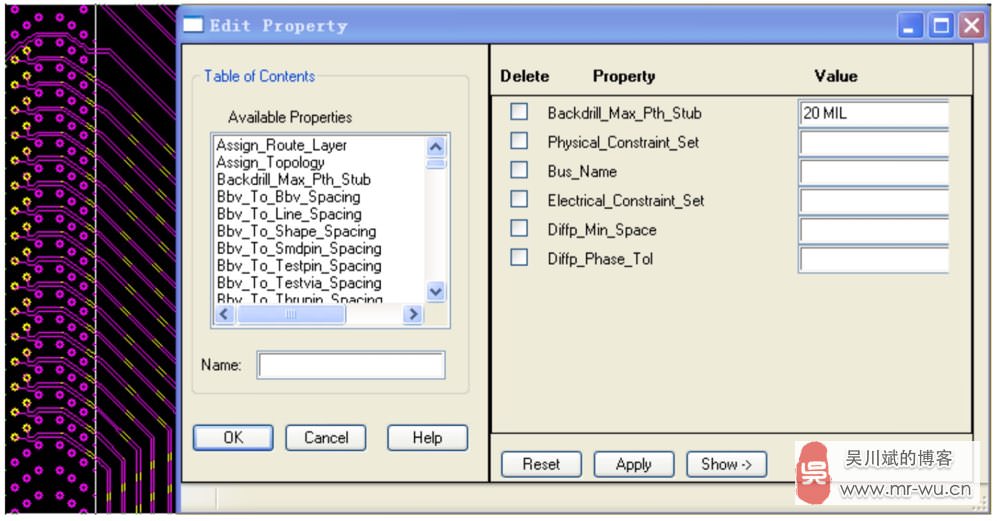

? 定义背钻网络

选择需要进行背钻的网络,给Backdrill_Max_Pth_Stub属性赋予一个数值20mil。这个设置包含两层含义:

定义选中的网络进行背钻设计

背钻后剩余的残桩不大于20mil

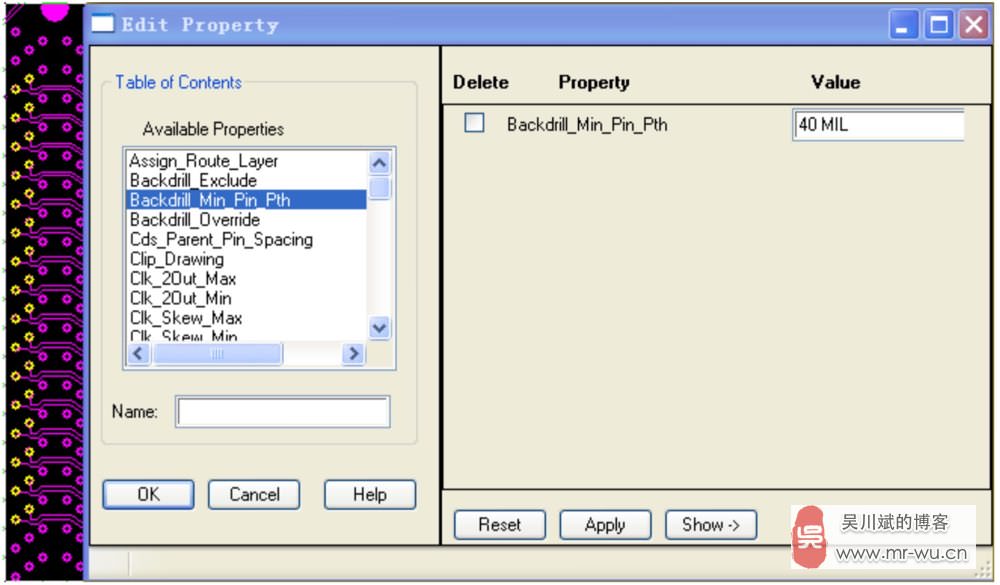

限制背钻深度

对于压接连接器的管脚,必须保留一定长度的孔壁以确保可靠连接,这时候我们就可以给这 些管脚赋Backdrill_Min_Pin_Pth属性,具体数值要根据连接器厂家提供的参数为准。

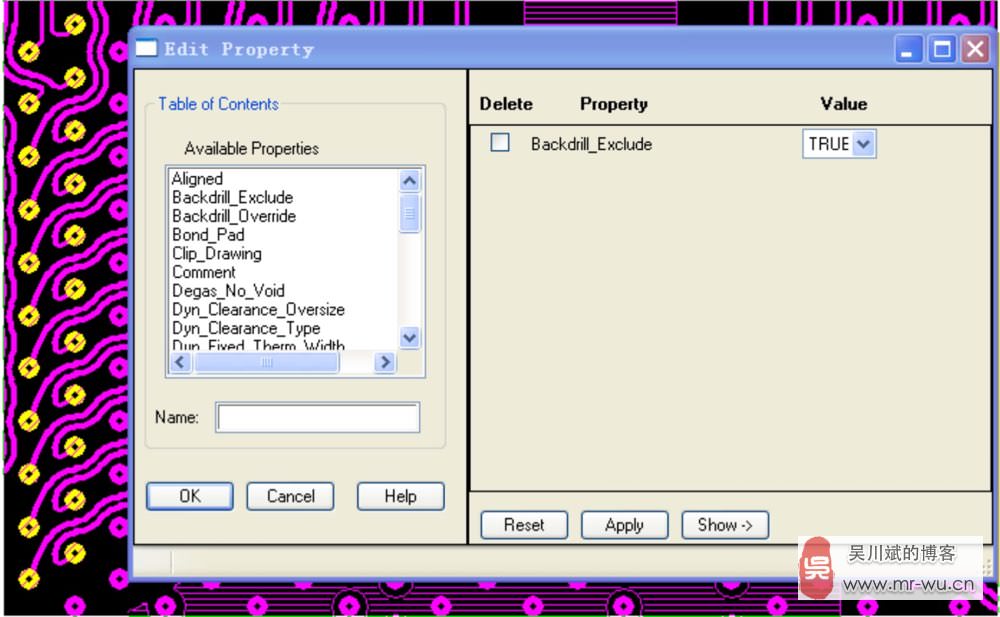

排除背钻过孔

选定背钻的网络,在CPU下面的过孔不满足进行背钻的条件,给这些过孔赋予 Backdrill_Exclude属性,就把这些过孔排除在外,不进行背钻设计。

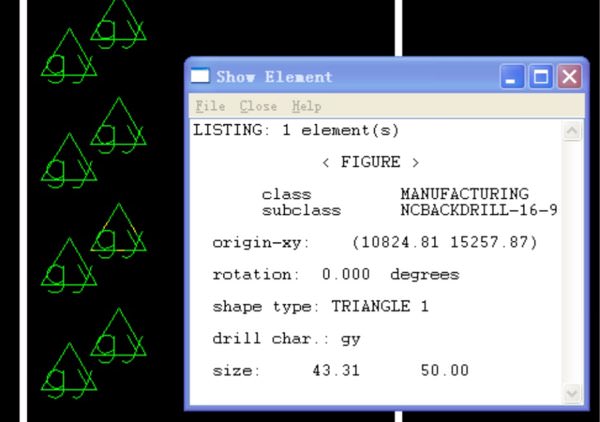

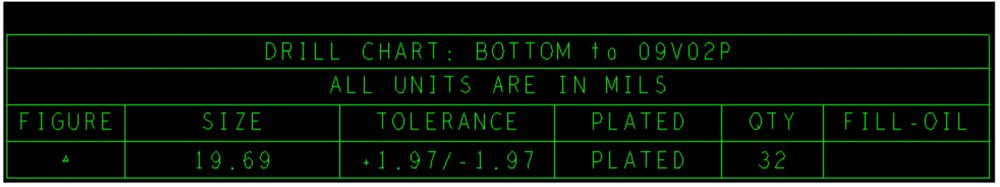

背钻设置和分析

Manuffacture->NC->Backdrill Setup and Analysis,进行背钻设置和分析。我们这里的背钻从 Bottom层开始到09V02P截止,其中09V02P层是钻透层。点击按钮Analyze,对背钻进行分析, 存在冲突的地方会产生错误标识,同时弹出文本框详细描述错误原因,根据提示修改,直到 没有任何错误。这个分析的功能可以确保背钻的深度既不会太深,也不会太浅,更不会把过孔本身连接的焊盘钻掉,在保证安全的前提下达到最佳的背钻效果。

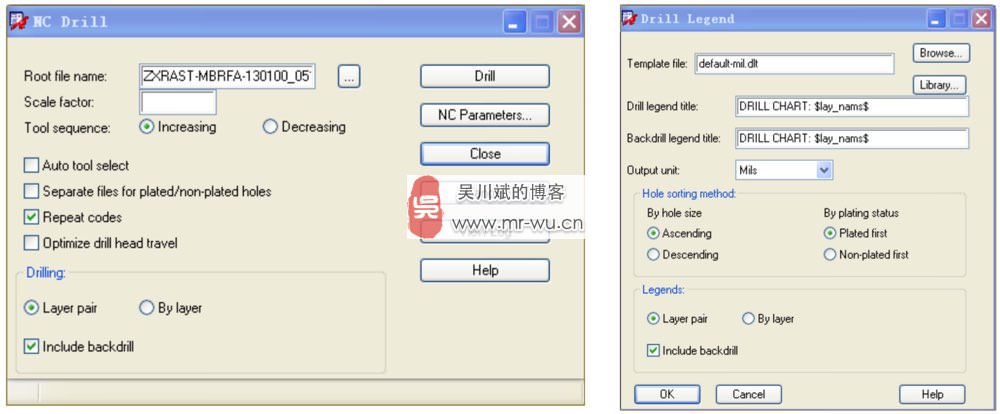

产生背钻标识

在NC Drill界面勾上Include backdrill,执行Drill命令;在Drill Legend界面勾上Include backdrill ,执行OK命令,背钻标识就会随着其他钻孔标识一起产生,并不需要单独的操作。

背钻标识

查看过孔上面的背钻标识,就能了解到这个过孔的具体背钻信息。 对于一种背钻类型,增加一个钻孔表格,作为对它的统计。

背钻输出

在光绘设置中添加背钻孔NCBACKDRILL-16-9 ,在输出的光绘文件中会增加一个钻带文件 bd-16-9.drl。与其他相关文件一起打包归档,使用起来非常规范。

二次开发工具的使用

Allegro是一个开放的平台,使用Skill语言我们既可以修改软件界面,使之更符合自己的设计习惯,也可以根据自己设计的特点开发很多快速工具,让我们的设计更加简便高效! 我们根据日常工作需要,在Allegro的平台上开发了很多实用的快速工具作为Allegro的补充。 在ZTE RAST服务器主板的设计过程中,在不同的设计阶段先后用到了多个二次开发工具,让单板的设计效率进一步提高。这里简单介绍几个。

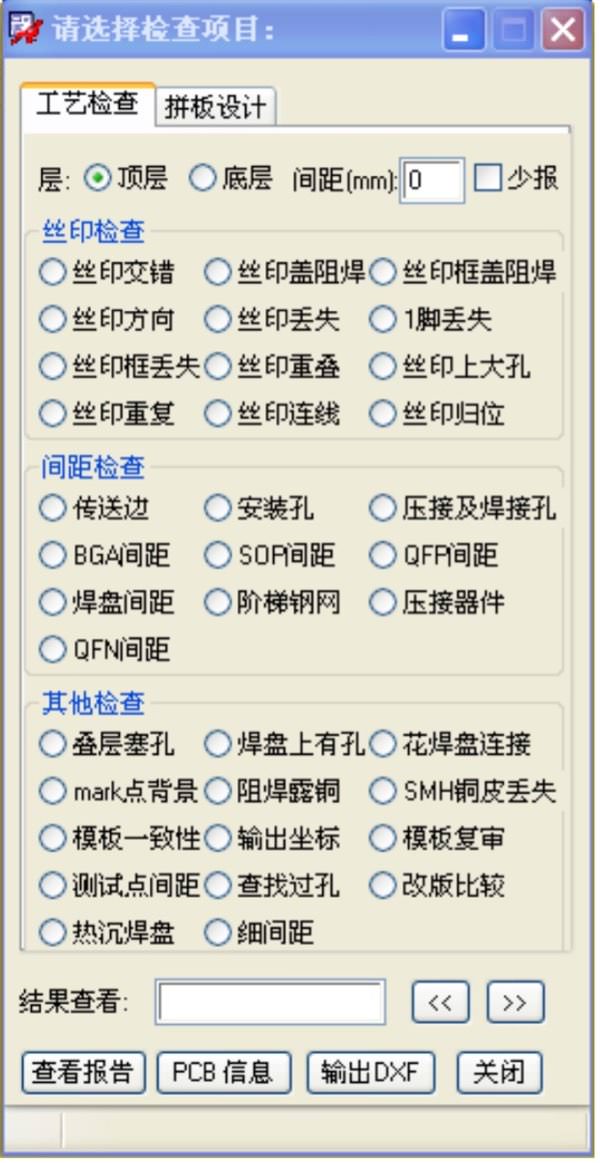

? 工艺检查工具

通过工艺检查工具可以全面、细致地检查单板在工艺方面的问题,不但节省了大量的人工检查的时间,还可以避免因人为疏忽造成质量事故,对于我们提高单板设计效率和改善单板设计质量起到了极大的作用。

光绘自动输出工具

光绘输出是PCB设计的最后一个步骤,一旦发生错误将难以挽回。我们采用在 Allegro平台上 开发的光绘自动输出工具,以最简洁的方式输出光绘,实现优质高效。

批量调整线宽工具

采用这个快速工具可以按照信号层将某一种宽度的线统一修改为另一种宽度,简洁高效

浙公网安备 33010602011771号

浙公网安备 33010602011771号