全双通通话消回音还在用FM1188?现在推荐新的应用方案FM23-CE-382B。

多年的使用习惯,做免提通话产品,需要回音消除功能,一般都选用美国富迪的FM1188作为首选,价格不是很便宜,但性价比也还可以。

但FM1188毕竟是很多年前的一款老产品,在2004年左右推出的,长期使用中发现缺点还是有一些的,比较典型的是消回音过程中,容易产生杂音。

虽然经过一些调校以及结构上的改进,有些问题能得到一些改善,对于产品的设计使用,还是可以使用大部分免提通话产品。

毕竟10多年的芯片,原厂对这个型号也在慢慢边缘化,官网早已撤掉了型号介绍,产量供应也在逐渐缩减,特别是到了2020年的大环境影响,国际技术打压,疫情蔓延,晶园短缺,各种因素,这款芯片同样出现了供应困难。

因此选用FM23这个型号的方案也是迫不得已。

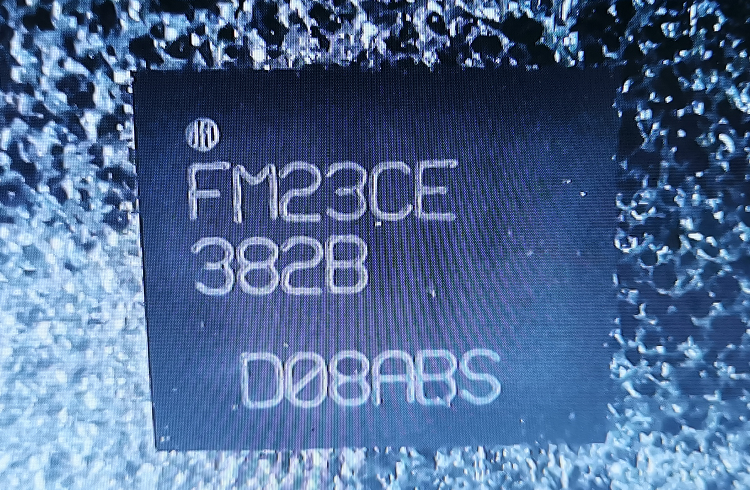

型号全称是:FM23-CE-382B,封装是CSP20。

芯片体积很小2.6mmX2.2mm,适合各种产品的设计选用。

![]()

![]()

![]()

但功能还是可以的,大致特性介绍如下

Highly integrated single-chip solution :

Voice processor with hardware accelerators.

Three 16-bit ADCs (Analog to Digital Converter) for two microphone inputs (MIC0 and MIC1) and

one line level input (LINE_IN).

Each analog input channel is sampled at 8 kHz, 84dB SNR.

Each microphone input has a built-in PGA as on-chip pre-amp.

1 DAC (Digital to Analog Converter) for line level output (LINE_OUT).

Built-in RAM and ROM code. No external RAM necessary.

Support Analog Communication mode (HW bypass mode).

Software programmable gain controller is built-in in each analog input and output port.

3.3V voltage tolerance for all digital inputs.

Low-power consumption:

180 nm advanced process.

2-microphone mode: ~25mW.

1-microphone mode: ~25mW.

Power down mode: Current Consumption 5μA typical

1.8V for all analog power domain.

1.8V for digital and core power domain.

High performance:

Powerful AEC (acoustic echo cancellation) up to 60dB.

Superior full-duplex

Support 2 microphones and 1 microphone modes.

Differential analog input to reduce RF interference.

Acoustic echo tail length coverage: up to 100ms.

Flexible clock sources: support external 1.8~3.3V clock source.

External 1.8~3.3V clock source :

3MHz to 32MHz with a multiple of 1MHz.

4.096 MHz to 40.96 MHz with a multiple of 4.096 MHz

Built-in PLL (Phase-Locked Loop) for the clock generation.

SHI interface supported with an external I²C compatible host controller up to 400kbps as the fast mode, and

controlled by sending commands and parameters on the fly.

Voice processor with hardware accelerators.

Three 16-bit ADCs (Analog to Digital Converter) for two microphone inputs (MIC0 and MIC1) and

one line level input (LINE_IN).

Each analog input channel is sampled at 8 kHz, 84dB SNR.

Each microphone input has a built-in PGA as on-chip pre-amp.

1 DAC (Digital to Analog Converter) for line level output (LINE_OUT).

Built-in RAM and ROM code. No external RAM necessary.

Support Analog Communication mode (HW bypass mode).

Software programmable gain controller is built-in in each analog input and output port.

3.3V voltage tolerance for all digital inputs.

Low-power consumption:

180 nm advanced process.

2-microphone mode: ~25mW.

1-microphone mode: ~25mW.

Power down mode: Current Consumption 5μA typical

1.8V for all analog power domain.

1.8V for digital and core power domain.

High performance:

Powerful AEC (acoustic echo cancellation) up to 60dB.

Superior full-duplex

Support 2 microphones and 1 microphone modes.

Differential analog input to reduce RF interference.

Acoustic echo tail length coverage: up to 100ms.

Flexible clock sources: support external 1.8~3.3V clock source.

External 1.8~3.3V clock source :

3MHz to 32MHz with a multiple of 1MHz.

4.096 MHz to 40.96 MHz with a multiple of 4.096 MHz

Built-in PLL (Phase-Locked Loop) for the clock generation.

SHI interface supported with an external I²C compatible host controller up to 400kbps as the fast mode, and

controlled by sending commands and parameters on the fly.

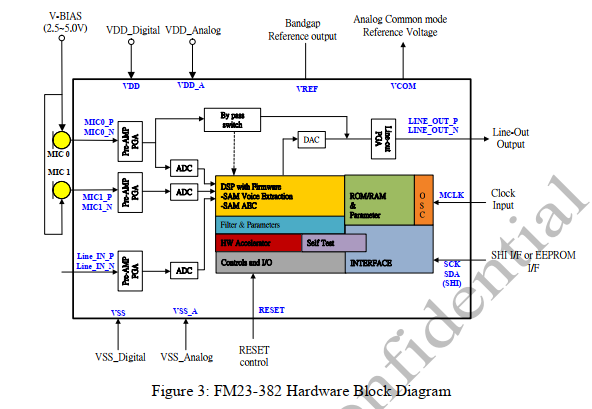

芯片工作框图如下

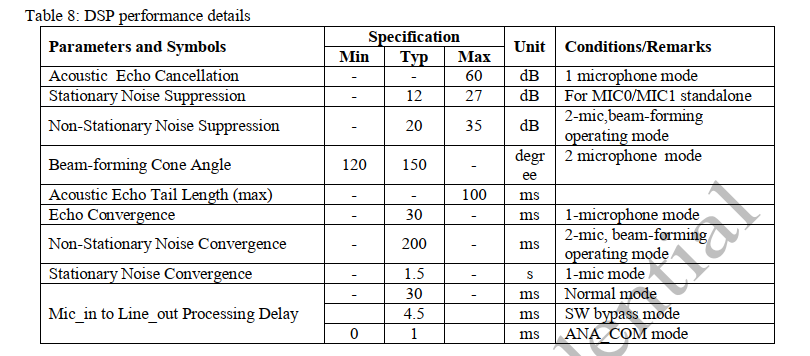

DSP处理 性能介绍如下

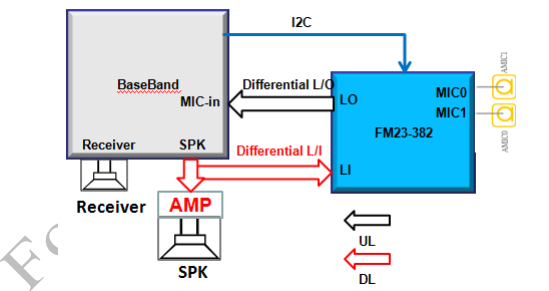

可以看出,芯片性能还是可以,在选用做样机测试,综合评测后,替换1188方案还是可行的。

如果有需要了解的工程技术朋友,可以加好友联系交流。

只讨论全双工通话消回音及语音拾取降噪技术问题,交流请加Q:2696573916,或VX13642365547

浙公网安备 33010602011771号

浙公网安备 33010602011771号