硬件工程师经典面试题(17):为什么高速数字系统如此偏爱差分传输?

Hello,大家好,之前看过全彩新书《高速数字设计》(基础篇)的一位粉丝说:看这本书会上瘾!

我当然明白他的意思,并且表示“感谢认可”,这种反馈对偶来说意义重大,因为写的东西对读者有用,也就终于达成了偶写作的目的。不过,其实我还想说:《高速数字设计》(进阶篇)较之《基础篇》更是有过之而无不及(我还没发力,你就倒了,哈哈,不要打我~~)

PS:《进阶篇》初步规划是从各种高速逻辑电平(如LVDS、ECL、GTL、CML、HSTL等)与常用高速接口(USB、HDMI、MIMP、SATA、DDR、PCIE等)角度阐述高速数字系统,与实践工程衔接会更加密切。当然,《进阶篇》的大框架肯定会以“章节”方式组织,因为像《基础篇》这样完美的编排架构实属可遇而不可求(这恐怕是“有章无节”编排架构的巅峰了,即便是已经得到广大读者认可的《三极管应用分析精粹》也要稍逊一筹~~)。当然,是否(或何时)正式撰写取决于《基础篇》受读者欢迎的程度。

言归正传,咱们进入下一个面试题:

为什么高速数字系统特别偏爱差分传输?

如今,高速数字系统的应用已经越来越广泛了,普通老百姓最常见的恐怕就是USB,其他还有HDMI、SATA、MIPI、GbE、PCIe等等,它们的数据传输速率都越来越快,并且都无一例外采用差分传输。那么,差分传输到底有什么魔力呢?我们简单来看一下!

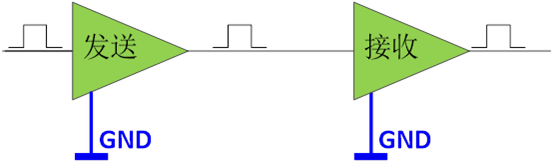

以往我们将信号放在一条导线上传输,而另一条导线则作为参考(例如,公共地0V),也称为单端传输(single-ended transmission)或非平衡传输,相应的传输结构如下图所示。

也就是说,单端传输的对象是“导线上的电压与参考电压之间的差值”,这也是比较常见且简单的通信与控制方式(以前我们讨论的基本逻辑门输入与输出信号都是如此)。

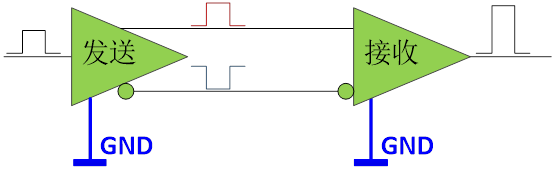

但是,单端传输结构有一个明显的缺陷:抗干扰能力比较差。当外部空间(或其他因素导致的)噪声耦合到信号线上时,传输线电平就会受到影响,一旦数字信号受的影响过大,接收方将很难准确判断,如下图所示。

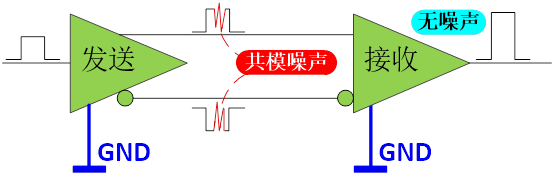

为了增强数据传输的稳定性,高速数字系统中更常采用双端传输(double-ended transmission),也常称为差分传输或平衡传输,其信号(在传输前)首先会被分解为两个互补信号(差分信号),然后分别在两条导线上传输,而第三条导线(例如,公共地0V)则作为参考,相应的传输结构如下图所示。

双端传输的接收方有一个很大的特点:共模信号的抑制能力比较强。也就是说,如果两条信号线上的电平同升(或同降),接收方依然有能力准确还原其中的信息。

具体来说,双端传输结构中的两条信号线之间通常是紧耦合的(尽管不是必须的),这也就意味着,噪声会同时反应在两条信号线上(产生了共模信号),而接收方只需要使用减法操作就能够将噪声抵消,而差模信号经减法操作后幅值就翻倍了(有用的信号通常就在差模信号中),相应的传输噪声抑制基本原理如下图所示。

顺便提一下,将差分对落实到PCB上时通常会遵循“平行、等长”的原则(“等长”本质上是为了“等时”),但是请特别注意:差分对上任何不匹配因素都会将差模信号转化为共模信号。因为两个信号总是可以看作是差模与共模信号的叠加,这也就意味着,只要差模信号由于任何原因(例如,传输线长度不匹配、宽度不相等、过孔数量不相等、过孔位置不对称、负载不相同等等)而使得接收方看到的不再是严格意义上的差模信号(例如,存在时序偏移或波形不对称),就可以理解为产生了共模信号,也就从某种程度上削弱了差分传输的优势。

当然,接收方具备较强的共模信号抑制能力只是双端传输的优势之一,而另外一个优势则是“能够主动将差模信号转换为共模信号”,受限于篇幅不再赘述。

以上文字与图片节选自全彩新书《高速数字设计》第21章《风骚独领的差分传输:反客为主》,其中从共模与差模信号的角度详尽探讨了差分传输的优势,并且结合实践阐述了高速PCB中差分对布线的注意事项。

原文链接:https://mp.weixin.qq.com/s/gGcEjf2VkC_Jmxx4WoVyTQ

相关链接:

浙公网安备 33010602011771号

浙公网安备 33010602011771号