硬件工程师经典面试题(15):为什么50Ω电阻与50Ω传输线并联不是25Ω?

Hello,大家好,咱们直奔主题进入下一个经典面试题:

为什么50Ω电阻与50Ω传输线并联不是25Ω?

这个问题应该算是信号完整性与高速PCB设计相关的经典问题,它来源于“应对高速信号反射的”传输线阻抗匹配方案,不少工程师可能曾经(或仍然)有些不解:50Ω与50Ω并联不正是25Ω吗?我刚学习电子技术就知道并联电阻计算公式,咋一到高速数字系统中就不管用了?

并联电阻计算公式当然是无敌的,只不过你确定并联的电阻值是正确的吗?咱们简单来看看究竟发生了什么?

我们知道,当高速信号在传输线上传播时,如果遇到阻抗突变之处就会产生信号反射,也就有可能破坏信号完整性(Signal Integrity, SI)。那么很明显,当信号通过传输线到达高输入阻抗负载时(这是很普遍的,因为数字逻辑的输入阻抗通常比较高),由于负载阻抗远大于传输线特性阻抗Z0,也就会导致信号反射现象,而端接匹配就是为了消除信号反射采取的常用措施。

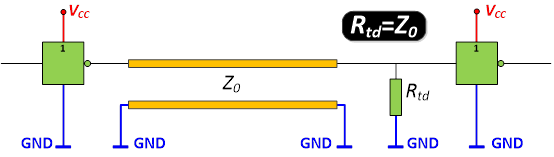

具体的端接匹配方案有很多,受限于篇幅不便赘述,此处仅介绍常用的终端匹配方案,它是在传输线终端(也就是负载端)对公共地并联一个下拉电阻Rtd,只要Rtd值等于传输线特性阻抗Z0即可完成匹配(这样当信号从传输线“跳”出到达负载时,其看到阻抗仍然是一致的,也就不会产生信号反射问题),相应的端接示意如下图所示:

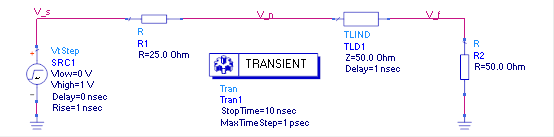

我们可以使用ADS软件来仿真一下,相应的仿真电路如下图所示。其中,SRC1是一个阶跃信号源(幅值为1V,上升时间为1ns),用来模拟一个高速信号的上升沿。TLD1是一个可以指定特性阻抗与传播延时大小的传输线(此处保持默认的50Ω与1ns),其左侧串联了一个25Ω的电阻(R1,可以将其理解为信号源内阻,其阻值与传输线阻抗不相同/不匹配),其右侧对地连接了一个50Ω电阻(R2,也就是端接电阻)。

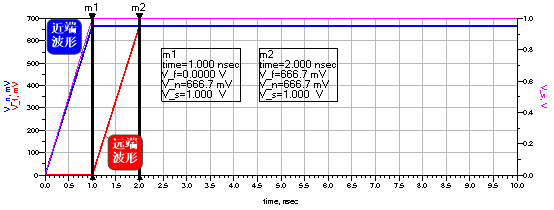

仿真得到的负载两端(传输线远端)的红色波形如下图所示,除1~2ns时刻是上升时间外,其他电平都是稳定的(没有反射波形),其稳定幅值约为666.6mV,它是当信号刚刚注入到传输线的那一刻,25Ω电阻(R1)与50Ω传输线对1V阶跃信号进行分压的结果。

那么很多人可能会想:50Ω端接电阻(R2)与50Ω传输线并联后的总阻值不应该是25Ω吗?那么当信号注入到传输线时,不应该25Ω电阻(R1)与25Ω总阻抗对1V阶跃信号进行分压(也就是0.5V)吗?

答案是:总阻抗可能是25Ω,但更有可能是50Ω!

首先我们需要明确一点:高速数字信号在传输线上传播时看到的阻抗仅取决于“信号电平转换的那个边沿(由高至低,或反之)”。如果形象点说,信号在传输线上的传播方式就好像我们蒙着眼睛走路一样(一叶障目),其感受到的瞬时阻抗就相当于“我们在脚着地那一瞬间才感受到的道路平坦度”。

也就是说,当信号传播到某个节点时,其感受到的瞬时阻抗仅取决于“信号电平转换期间这一小段传输线的实际状态”,而该节点之前的路径是透明的(已经走过的路就不必理会了),该节点之后的路径也是不可见的(还没有走过的路就暂时不必理会),“活在当下”正是信号在传输线上的传播方式。从易于理解的角度,信号感受到的瞬时阻抗仅取决于在电平转换期间对应的总电感L与总电容C,如下图所示。

如果传输线的长度足够短,那50Ω端接电阻与50Ω传输线并联还真是25Ω。但是对于绝大多数传输线较长的场合,“传输线远端的端接电阻”对于刚刚注入到传输线近端的信号来说是不可见的(换句话说,刚刚注入传输线近端的信号并不知道传输线远端是否存在端接电阻),自然不能根据“端接电阻与传输线阻抗并联值”计算注入到传输线上的信号电压幅度,因为信号在刚注入到传输线时只看到50Ω的传输线阻抗。

简单地说,传输线足够短时可以简单理解为一个50欧姆电阻(集总参数元件),但当传输线较长时却表现为分布参数元件,不能简单使用电阻并联公式计算总阻抗。

以上文字与图片均源于已出版全彩新书《高速数字设计》(基础篇),其中涉及更多细节,也详细探讨了以下两个相似问题:

其一,虽然信号从传输线远端出来经过了“与传输线特性阻抗值相等的”端接电阻,但是再往前传播不还是高阻抗负载吗?难道不会导致信号反射?

其二,同样都是50Ω,凭什么电阻器就能消除反射,而传输线却不能呢?传输线阻抗不也是并联在负载两端的吗?

----

原文链接 https://mp.weixin.qq.com/s/MHPlTVGWD307TG4jF-1Ccw

相关链接:

浙公网安备 33010602011771号

浙公网安备 33010602011771号