失调电压(三)运放失调的仿真

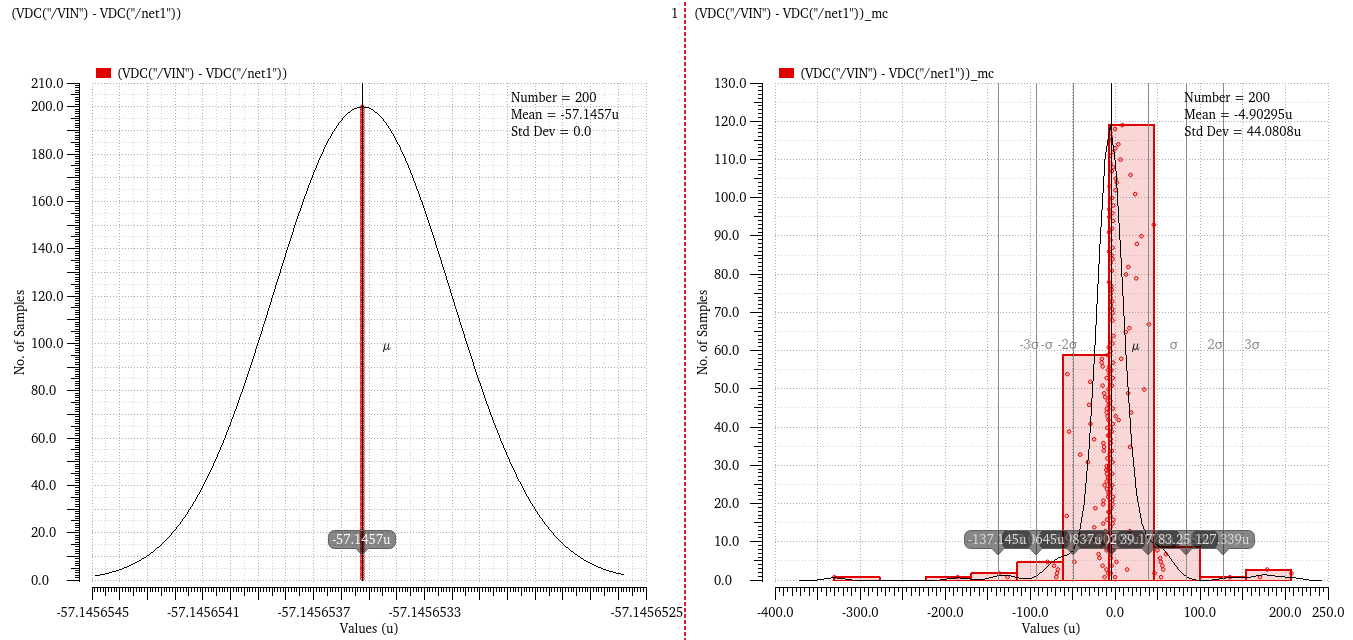

经常在某红薯/某群看到有同学问为什么他的VOS仿真结果像下面这个样子,均值uV级,3sigma也是uV级。大家听后分别表示惊为天人,是不是用了chopper,虽然说我当时用chopper也没chopper到3sigma50uV的情况。后来发现只是有人没用带蒙卡模型的管子去跑了VOS的蒙卡仿真hhhhh。

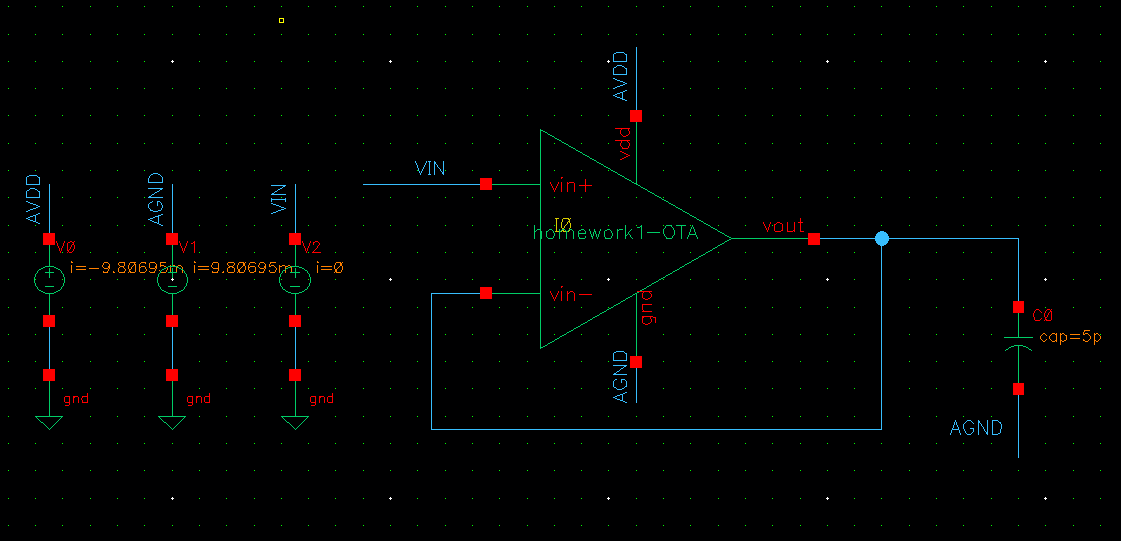

运放失调电压的仿真我目前用的是Allen书里写的这种方式,一个最简单的tb可以搭成这样(确实是啥都不考虑最简单的):

由前面(一)(二)的讨论可以知道,运放的失调电压=器件失调=失配+版图不匹配+电路不匹配。首先,电路不匹配可以体现为不对称的电路结构、不完全对称的电流镜、以及各种buffer由于增益等非理想带来的系统失调;第二,器件失调引起失调电压,就像(二)中所说的,一个差动对里面,负载的失配和输入对管的宽长比失配会被VOD放大到输出,阈值电压失配直接折合到输出,这种道理;另外,版图画得匹配性差在此也能引起失调电压。

因此,要关注失调问题,首先电路本来的系统失调要被关注到,其次要带上器件的mc模型去跑mc才能仿出失调电压,最后画完版图还要在跑后仿的时候关注到这里的失调电压是否被一个糟糕的版图工程师扩大化了。上图50uV的失调原因现在一目了然,娃没带管子的mc模型直接跑的mc,所以其实跑出来的只是个系统失调。

###############################################################################

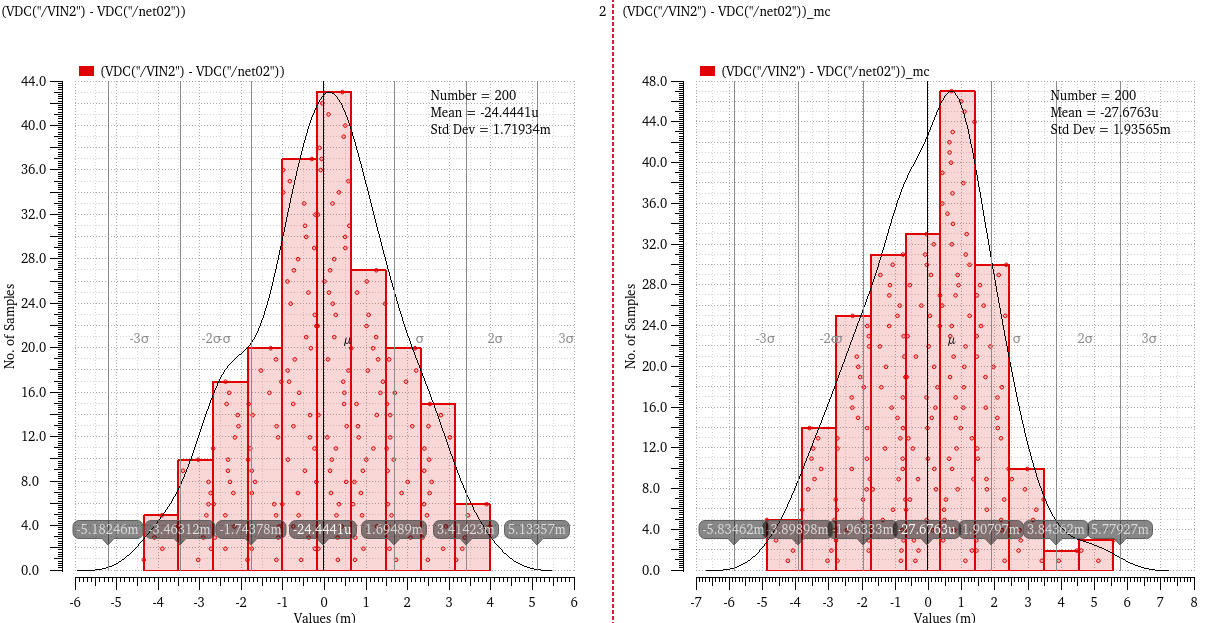

这里给到一个真实的运放失调仿真结果实例(随便拿了个很久前的运放,很垃圾但不影响学习):

(1)此时,输入对管的WL=80u2u=160uu,VOD=65mV。仿真到失调电压的3sigma大约为4.6mV

(2)当我们改输入对管的WL=160u4u=640uu,VOD=65mV。仿真到失调电压的3sigma大约为4.4mV。这里为什么增大了输入对管的面积为4倍,sigma才变化了0.1mV,个人找补原因是,本来就是sqrt的,其次趋势是对的。

(3)当我们改输入对管的WL=40u1u=40uu,VOD=65mV。仿真到失调电压的3sigma大约为5.9mV。这里为减小了输入对管的面积4倍

(4)当我们改输入对管的WL=40u2u=80uu,VOD=80mV。仿真到失调电压的3sigma大约为5.6mV。VOD的影响确实是最明显的。

就这样吧,这玩意跟工艺关系太大了,我做过的最好的也只是2mV多,连1mV的边都碰不到,感觉CMOS工艺要下去到uV内,必须用上clk了,改天再给出chop后的结果。

浙公网安备 33010602011771号

浙公网安备 33010602011771号