电流镜、电流镜的失配、电流镜失配常用的消除技术(三)

今天来学习CM的失配以及消除,对我们的设计作出进一步的指导:

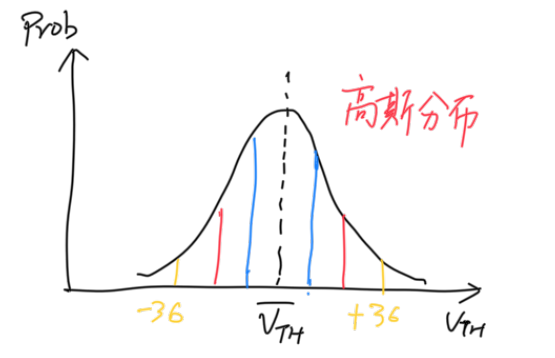

失配通常会对模拟电路有很大影响,在设计阶段需要充分考虑。比如表现为运放的输入失调电压,电流镜的镜像误差。也可能导致量产时候良率损失的重要因素。阈值VTH算是器件最重要的参数了,工艺流程中,通常都有阈值调整的Mask,从而保证阈值符合预期。尽管如此,实际的阈值仍然存在着接近高斯分布的偏差,偏差量的标准差和器件面积的关系可以用AVT的参数表示。(以前有小朋友问过AVT是不是VTH的增益hhh,听说在晶圆厂干工艺的同学们要一直盯着这个指标,突然偏移过大了就算人在被窝也得赶紧蹦起来去检查机器):

!

!

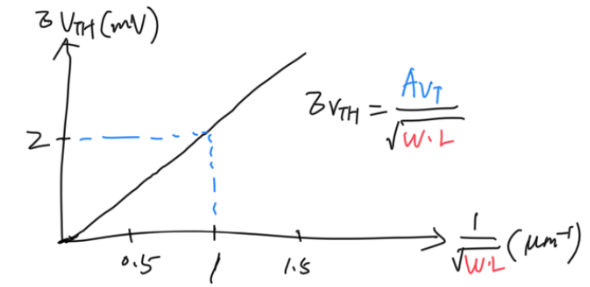

从下图可以看到,随着WL乘积的增加,1/sqrtWL的减小,deltaVTH会减小,会向里走,走的速率就是AVT;随着WL乘积的减小,1/sqrtWL的增加,deltaVTH会增加,会向外走,走的斜率就是AVT,AVT越大,deltaVTH就涨得起飞,这就是AVT的意义。(举例:假如AVT=2mVum,如果MOS器件的WL=1um^2,则通过计算简单估算阈值失配3σ(VTH)=6mV)。除了阈值VTH,其他工艺参数也存在随机分布的情况。比如工艺提供的测试结果通常会包含VTH_gm、Idsat、Δβ/β等的偏差计算公式,帮助设计人员选择器件尺寸。当然除了MOSFET外,电阻,二极管,三极管,电容都存在偏差,各种器件的偏差,对构成的复杂电路系统的影响,通常需要借助EDA工具协助分析和评估。这就是mc的意义,也是为什么失调我们用mc来跑的原因。之前有小孩问为什么他跑PVT的时候,不能一起跑mc和corner,追根溯源就是这里了,虽然但是EDA里面其实也写清楚了,mc=process+mismatch,这些都可以同一归结到这里AVT等吧我觉得。

实际上,在先进工艺节点中(40nm以下),和版图相关的效应,如LOD、WPE、PSE、OSE及DFM、STI等都对器件有着比较明显的影响,可能导致失配。这里又来复习本科学过的二级效应,看原理不是目的,指导设计和版图才是目的:

1、WPE(Well Proximity Effect)阱临近效应:是指在阱doping的过程中,阱边缘由于散射doping浓度比其他地方要高一些,这样临近阱边缘的器件特性就与远离阱边缘的器件特性不一致,主要体现在阈值电压、迁移率和体效应上(例如NWLL的掩模边缘原本该被挡住的地方还是散射掺杂进WELL的边缘来了)。WPE效应影响很多,但最最需要关注的就是VTH了,在一些VTH敏感的场合例如基于VTH的全CMOS基准就要给版图工程师明确的指示,这里WPE一定要注意。WPE的解决方案:(1)在扩散区边缘放DUMMY;(2)器件离WELL的边缘远一些;(3)工艺上再加一些特殊的离子注入手法。方法(2)是咱们常用的,将器件远离阱,可以减小WPE,即将well面积画大一些,将器件的上下左右四个方向到well的距离尽量大,一般都会有一个最小距离要求,大部分是2um以上,不满足2um也不会报DRC错误,所以在DRC和LVS验证的时候是查不到WPE效应的。如果满足了2um,一般都可以将WPE降到很小,如果满足了2um还不能和前仿真相等,那就是用的工艺还有一些其他的规则要求,但这时候WPE肯定是在可以接受的范围了。

(2)STI(Shallow Trench Isolation)浅槽隔离的压力效应:在很多时候也叫LOD效应,这俩基本上属于因果关系。隔离器件现在很多用STI,需要用到CVD,化学气相沉积挖出沟槽这个动作会对两侧的器件产生机械压力,因此STI会产生应力,这个应力会使得STI两侧的器件特性受到影响。这里就涉及到了LOD和OSE效应了。

LOD效应:由于STI到多晶硅栅poly的距离也就是器件有源区长度的不同,应力对器件的影响也不同,因此叫做扩散区长度效应,如下图,有源区OD的长度越大,STI对器件的应力影响越小。因此,如果想要2个MOS匹配,那么他们到STI的距离应该是一样的或者距离大到可以忽略不计LOD效应。LOD效应和WPE效应一样,直接影响MOS管的阈值电压等参数,因此如果电路对阈值电压比较敏感,那么在layout中一定要把LOD效应考虑在内。LOD效应怎么考虑,最简化说就是保证离STI最近的最左边和最右边的poly,它们距离STI的距离一致,当然前提是左边M1,右边M2这种情况,或者距离远到LOD效应太小了也行。

OSE效应:OD Space Effect,是由于STI本身的宽度不同引起的对两侧器件的应力不同。这个效应在数字IC研究居多,模拟IC主要研究LOD效应,那就偷懒吧。

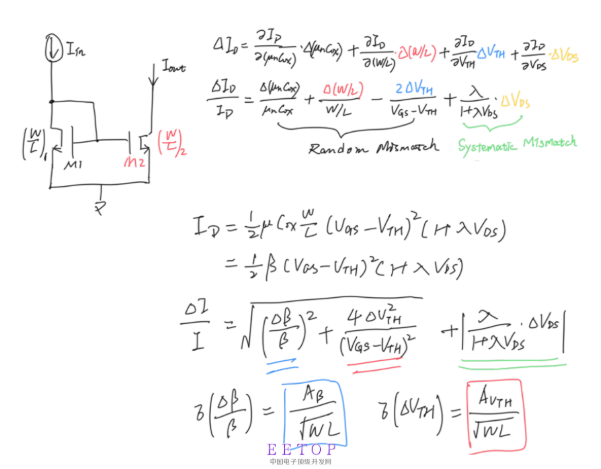

最主要的,对于简单的电流镜,考虑如何减小失配的影响是我们的重点。如图,其中β和VTH都可以通过增大面积减小失配的标准差,并且通过增加过驱动电压VGS-VTH可以减小阈值偏差对总电流偏差的贡献:

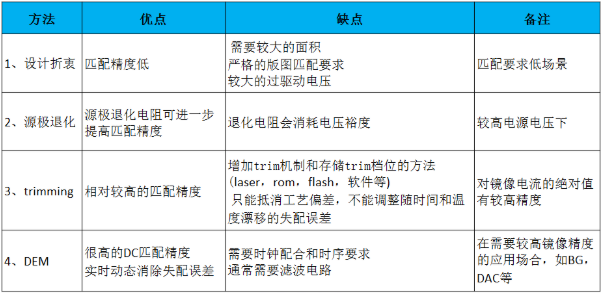

电流镜的失调=随机失调+系统失调。我们设计的时候可以调节系统失调,各个DC点要调整好,实在不行引入负反馈做类似于自偏置的结构也能把系统失调干没。随机失调我们也管不了太多,但是要尽量想办法减小,例如面积的考量,多去跑mc。当然有一些实实在在的办法,别人总结得很好:

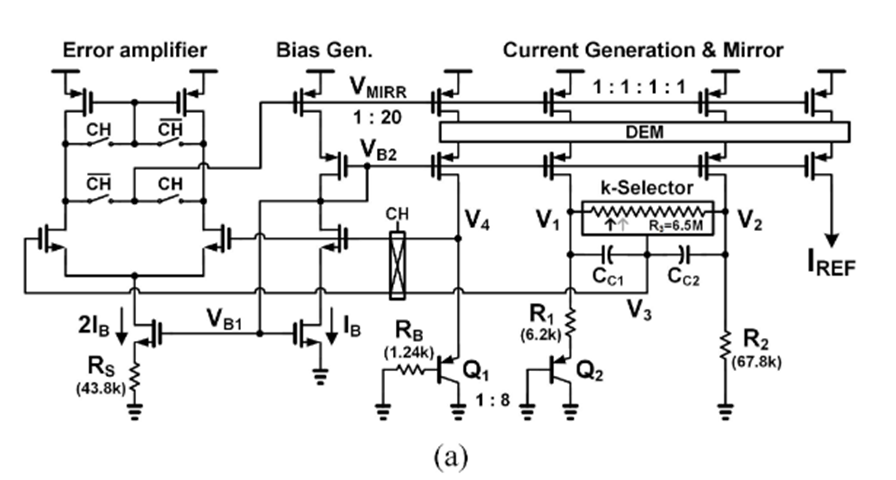

方法1~3很常用,这里对方法4很感兴趣,在2024年基准的J上就用DEM:(1:1的DEM不就是chop么),DEM同样可以用在1:N、M:N的镜像关系中时,这时需要时钟电路配合,产生特定的控制时序,通过轮源切换的方式,动态消除镜像器件的失配量。这里就不多说了,基本原理很简单,当然查询DEM确实发现有很多更厉害的玩法,主要是时序问题。

浙公网安备 33010602011771号

浙公网安备 33010602011771号