电流镜、电流镜的失配、电流镜失配常用的消除技术(二)

上文回忆了常见的电流镜电路,捋了一下普通电流镜-威尔逊电流镜-普通cascode电流镜-各种低压cascode电流镜的进阶以及设计思路。在进行今天的学习之前,为上文再丰富一些内容:

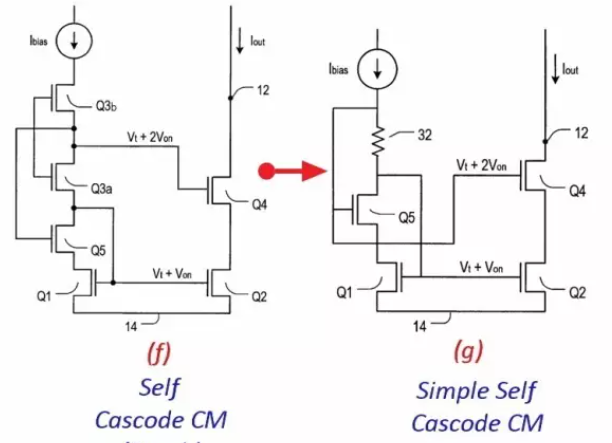

上文最后说到常用的用电阻直接生成VB=VGS+VOD的低压cas思路,其实它的原型是贝尔实验室的Sooch于1985年申请的专利号为4550284的美国专利提到的结构:

可以看到这与之前介绍过的孙楠老师展示过的电路非常类似,需要注意的是,图7(f)中Q3a工作临界饱和状态,其简单的等效原理可以表示为图7(g),变成最经典的电阻自偏置低压cascode,但是多吃掉了一些输入摆幅。

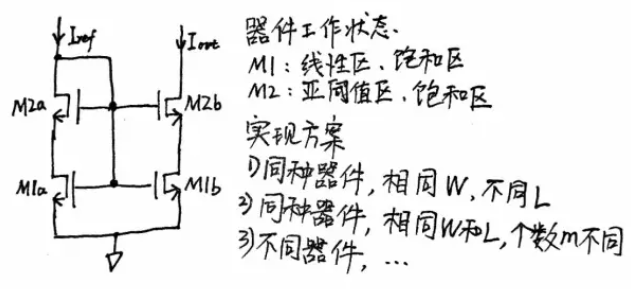

下图(h)是Aashi公司的Ichiro于1999年申请的美国专利中提到的结构,专利号为5966005,在原始的专利中,Ichiro提到利用短沟道效应,通过使用不同的沟道长度,配合不同的阈值电压,实现Q2工作在饱和区,从而实现较高的输出阻抗(反向短沟道效应,会使阈值随沟道长度减小而增大,貌似这样该结构就无法保证Q2工作在饱和区)图(i)为带源极电阻负反馈的电流镜,可以作为(h)的等效电路。

这里是怎么体现Ichiro利用到短沟道效应的呢?可以看到共栅管的L取L2,共源管的L取L1,W都为W,如果设计L1>L2,即让上面共栅管充当那个短沟道器件,于是有VTH3<VTH1,而VG=VTH1+VOD1,则VD1=VG-VTH3-VOD3=VTH1+VOD1-VTH3-VOD3=VTH1-VTH3,当L取得合适的值的时候VD1>VOD1,使得下面的共源管也能饱和。这个结构其实很常见,self-cascode的结构,或者基于VTH的亚阈值CMOS带隙基准,这里都是这个框架,只不过Ichiro设计了L不同使得VD1能提起来。由于饱和区的MOS的ro很高,这里虽然电路等效为源负反馈,但是共栅管能放大的小信号电阻获得了巨大的提升,使得输出阻抗成为gmroR=gmroro的量级。

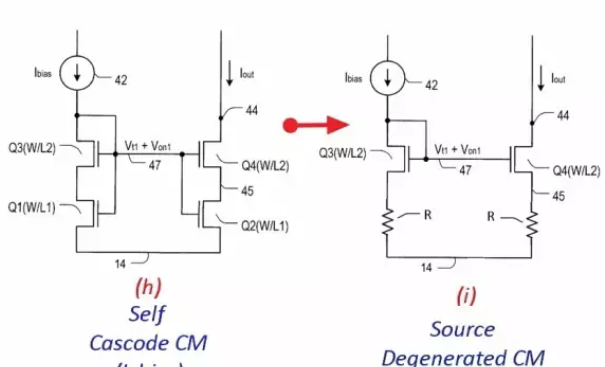

这里刚好补充学习一下器件物理的知识:

1、短沟道效应SCE,Short-channel effects:当MOSFET的沟道长度 L 缩小到与源/漏结的耗尽区宽度可比拟甚至更小时,原本在长沟道器件中成立的理想静电学假设被打破,导致一系列非理想效应,统称为短沟道效应。设计者需要知道的SCE对电路参数的影响:(1)Vth 随着沟道长度 L 的减小而显著降低;(2)DIBL效应出现:Vth 随漏源电压 Vds 的增大而降低。高 Vds 下漏极电场“帮助”栅极降低了源端注入载流子的势垒。使得gmro减小,漏电增加。(3)亚阈值摆幅退化,亚阈值摆幅 S (指使 Ids 变化一个数量级所需的 Vgs 变化量,理想最小值 ~60mV/dec @ 300K) 随着 L 减小而增大(变差)。

2、反向短沟道效应:在非常短的沟道长度下(通常比 SCE 主导的区域更短),有时观察到 Vth 随着 L 的进一步减小而反常地升高的现象,称为反向短沟道效应。具体到电学特性就是:(1)阈值电压上升;(2)迁移率下降,gm减小。

为了直观一点,可以看一张前辈扫的图:器件的阈值和栅长密切相关,表现为反向短沟道效应。下图是低阈值、标准阈值和高阈值1.2V器件的阈值变化情况。随着栅长的减小,阈值都有不同程度的增加。这也是先进工艺中,电源电压在下降,但模拟电路中选择的器件栅长并不能按比例shrink缩小的原因。

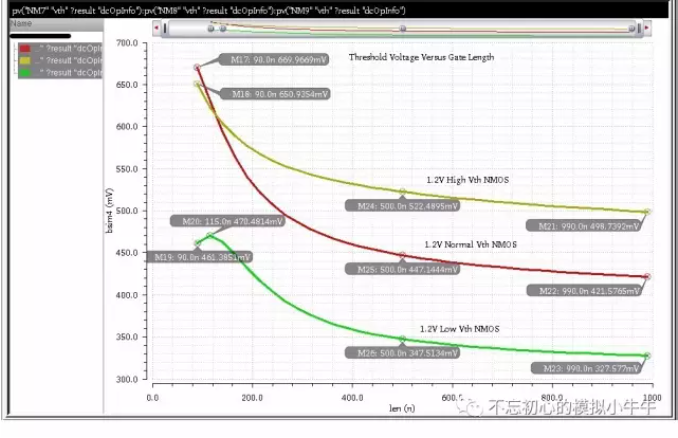

上面的电流就是self-cascode的结构,一般在低压电路中经常会用,我也用过。下面再来学习一下这个电流镜如何设计:

下图列出了Self Cascode CM的实现思路及方式。这里提出了几种可能,其中方案(1)利用同一类型器件不同L去实现,也是Ichiro专利提到的思路。方案(2)也是目前文献中提到的性能较好实现方式。方案(3)是利用部分工艺提供的不同阈值的器件组合来实现。

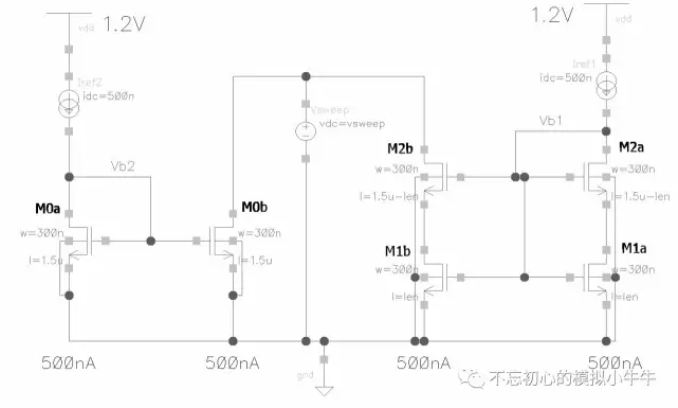

方案(1):Ichiro在其专利中提到的方法,其解释是利用M2的沟道比M1的沟道短,从而M2管阈值小于M1管,利用阈值差,使M1工作在临界饱和,从而得到较大的输出阻抗。当然,你工艺不能太先进,不然会有反向SCE效应了,一般来说差不多100nm吧。这里对比了同样面积条件下单管和拆分的管子的I-V特性。测试环境如图6所示后续也会用到这个测试电路作为对比。这里选择了W=0.3u,总的栅长L=1.5u,镜像500nA的电流。测试图:

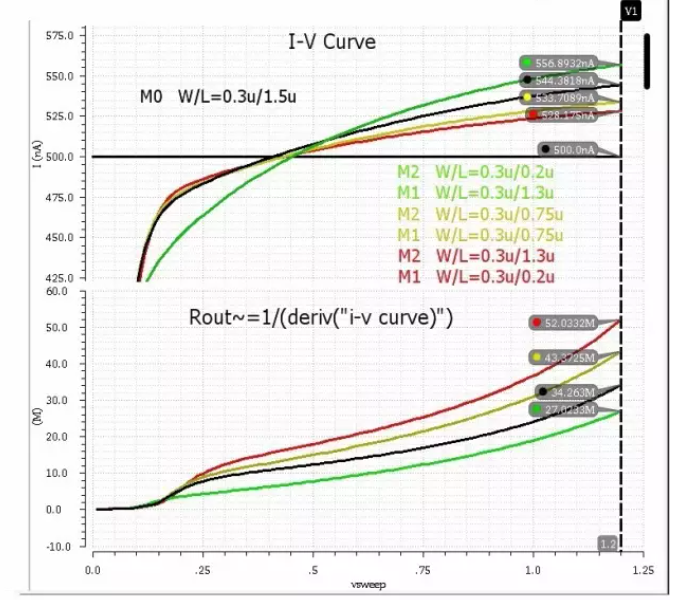

测试结果(这里应该是已经属于RSCE的情况了):

黑色为单管M0b的漏极电流;红色、黄色和绿色为不同尺寸拆分情况下M2b的漏极电流。红色情况下输出阻抗提升比较明显,这也是最简单的一种self cascode结构,通过拆分,能够提高输出阻抗。注意,这种情况下,M1管沟道较短,其阈值较M2管大很多。当总的栅长较大时,情况会稍有不同,阈值差别不大,需要用方案2)来实现。

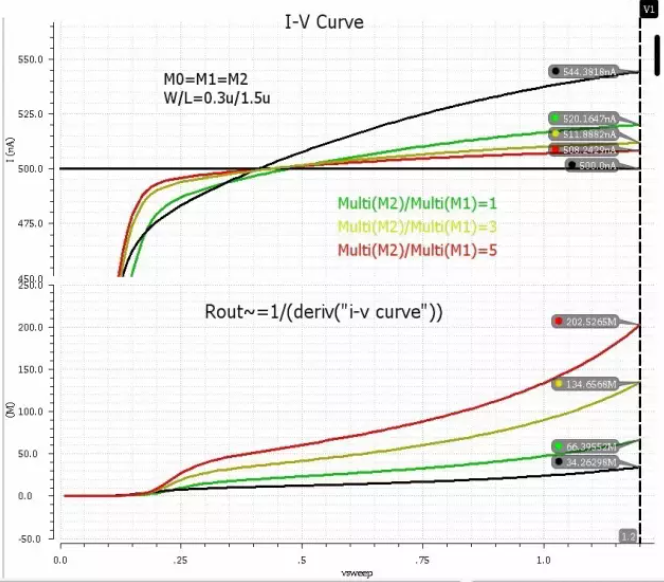

方案(2):同种器件,相同的W和L,取m不同:这次M0、M1和M2的W/L=0.3/1.5u,改变M2和M1的个数比(这也是我常用的办法,本质就是VOD作差而不是VTH作差):

测试结果:虽然对比有些不公平,毕竟面积大很多,但可以看到这种方式还是能够大幅度的提高其输出阻抗,并表现出了较小的饱和电压从而增大了输出摆幅。其中M1工作在线性区或临界饱和,M2一般会工作在亚阈值区。

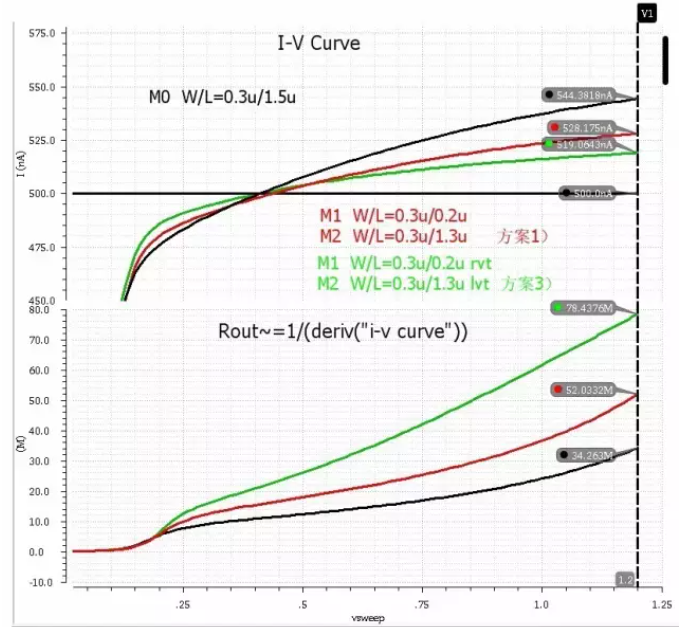

方案(3):用svt和nvt的MOS管:适用于提供的多种阈值的逻辑器件(90nm以下)的工艺。从图4看到,hvt器件阈值会比rvt多出几十毫伏电压。利用阈值差,可以促使M1管工作在临界饱和区,从而得到较大的输出阻抗。

总结就是,不缺面积就用方案(2),缺了就用(1),有多种管子那直接用多种管子,不过你要考虑版图匹配性和PVT。

浙公网安备 33010602011771号

浙公网安备 33010602011771号