电流镜、电流镜的失配、电流镜失配常用的消除技术(一)

电流镜是带隙基准电路设计中非常重要的一个环节,今天想记录记录对于电流镜的思考。

一、有哪些电流镜

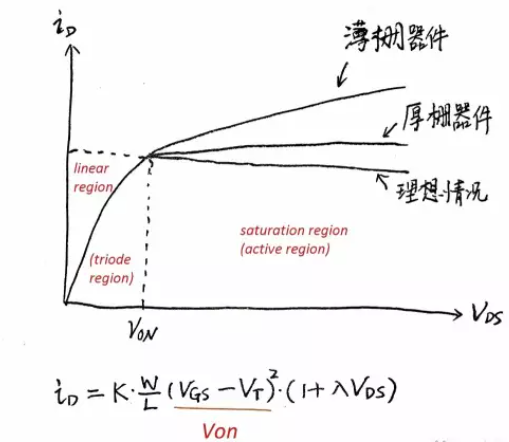

1、电流源具体会根据电流的流向,分为电流源(Current Source)和电流沉(Current Sink),电流源通常都是以电流镜的形式实现,可以看做是双端口电流放大器。单个MOS管的输出电流随着工艺节点的缩小表现出饱和区的非理想性:

2、来看看常用的电流镜结构:

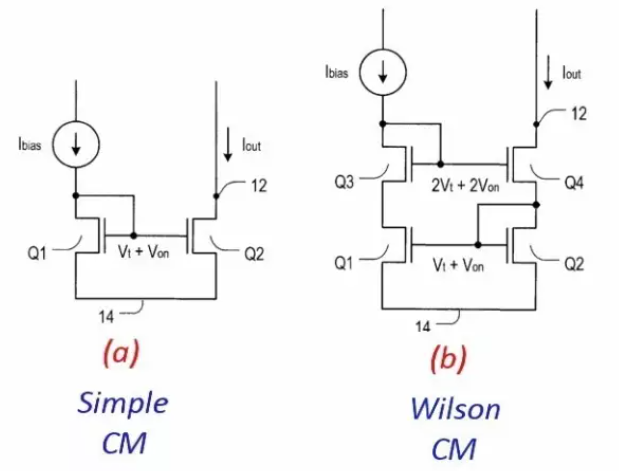

a表示最普通的电流镜,只能用长L的管子去压制CLM效应,Channel length modulation。另外,写出Iout/Iref表达式,发现当两个NMOS的L取不一致时,CLM系数不一致,于是镜像误差会被加剧。

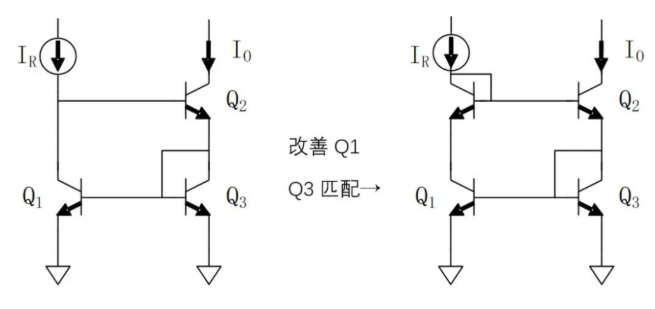

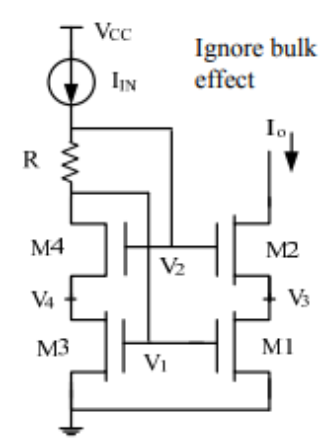

b表示威尔逊电流源,基础思路就是引入负反馈去抑制Iout输出端的电流变化。实际上威尔逊一开始提出的是下图(左)的结构:

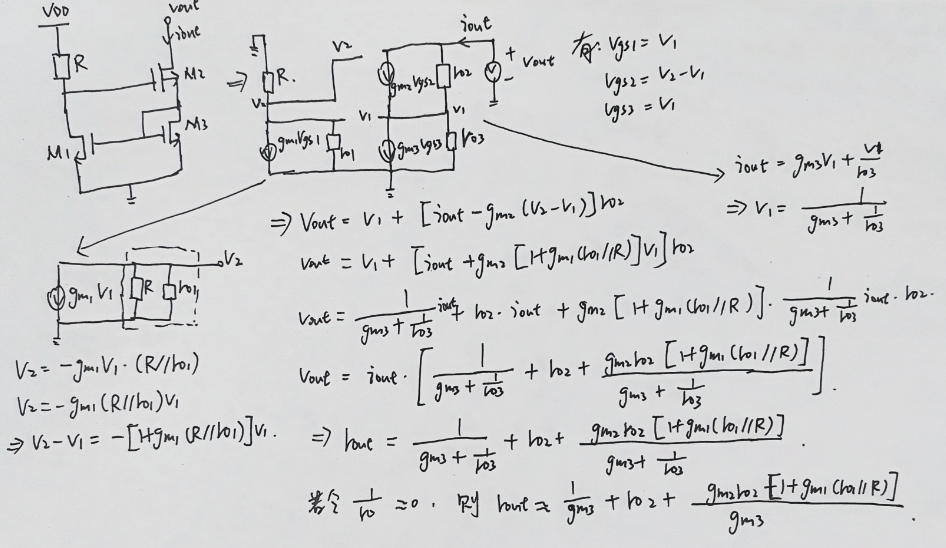

这里我将BJT的变成NMOS。编号和拓扑不变,对于左,在原来M3的漏极引入M2作为负反馈的传递者与输出I0波动的屏蔽者,看上图(a),本来,当输出端IOUT的电压上升时,Q2由于CLM效应输出输出电流增大。现在,看下图(左),假设电流I0增加,则M3电流上升,则VG3上升,而M1和Reference的内阻组成一个common source stage,M2的栅极电压下降,结合VG3即VS2的上升,则M2电流即I0下降,这是一个负反馈过程,输出电流I0得以稳定。实际上这里也是改成了输出级cas的形式,不过二极管形式的接法接到了输出端的NMOS上而非输入NMOS上,其输出阻抗是gm2ro2*1/gm3吗?不是,我画了一下小信号,得到输出电阻的量级大概是gm2ro2(ro3//R)。如果参考电流源内阻较大,则电流镜输出电阻大约为cascode的电阻,当然这是比较常见的情况,但是当参考电流源内阻较小时,此结构的输出电阻将会降低。

这样威尔逊电流镜就可以做到抗输出节点电压变化,此时我们考虑其copy的性能,注意到,VDS1=VGS2+VGS3=VGS2+VDS3,多出了VGS2,因此有:图(右)是后人对威尔逊电流镜的一种改进,目的是使得输入支路也为cascode结构,这样可以明显发现VDS1=VDS3,电流镜的copy能力是好的。看上图(b),改进版的工作原理为:若Vout上升,Iout上升,则VG3上升,VD1下降,则VIN下降,即VS2下降,于是对于M2,VS2上升,VG2下降,M2电流减小,于是输出电流的增加得到抑制,负反馈调节起作用。这里我们也能求一下其输出电阻。我纯纯懒蛋子,改天再求吧,笔漏墨了,离谱。

不论怎么说,威尔逊极其改进型,都消耗了更多的电压裕度,输出电压最小值为2VOD+VTH。

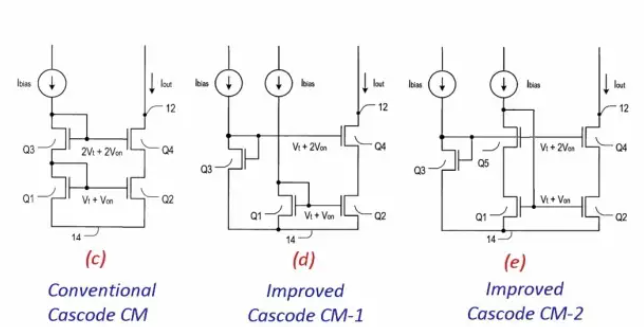

另外有cascode电流镜:

(c)与改进型威尔逊电流镜十分相似,区别只是下面共源的NMOS的二极管接法的位置。事实是一开始工程师发明的cascode电流镜并没有M3管,如图(d),但是共栅管M4的偏置需要解决,因此才引入了如图(c)所示的简单cascode电流镜结果。这里不管负反馈的问题,因为从外部Vout节点到左边支路属于漏极到栅极的影响。这里就用电流源的角度考量:实际电流源相比理想电流源要多并联一个电源内阻在二端口上,因此分出去的电流会被内阻分流,内阻越大分流越小,由于此处内阻为cascode倍增的内阻,所以对外抑制能力得到提升。然后又来第二个问题,copy精度的问题,即VDS1和VDS2问题。假设四个管子尺寸相同,看左边,由于I3=I1,有VGS3=VGS1,看右边,忽略CLM时有VGS4=VGS2,又因VGS1=VGS2,所以得到VGS3=VGS4,得到VX=VY(一般都这么命名)即VDS1=VDS2,因此copy也是准的。当然,这里其实只要M2/M1=M4/M3即可。

当然,(c)相对于(d)不仅仅只是增加了M3去偏置M4共栅管而已,原因在于如果M4的VB由外部给的话,当外部VB变化时,VY即VDS2跟着变化,输出电流变成了外部电压的弱函数,那自然是不要的。当然你可以设定好VB合理的值,但也没解决根本问题。而(c)就没有这个问题。(c)的坏处就在于输出摆幅限制在了VOD4+VGS2,原因在于VX=VY。(d)的摆幅就明显大了一个VTH,因此把这种摆幅在2VOD的cascode电流镜叫低压cascode电流镜。这里有个经典问题是:当VOUT下降时,M4和M2谁先进入线性区?

(e)是最常用的一种低压cascode电流镜,它可以成功解决以上(c)和(d)的输出摆幅和copy精度的问题。说白了,(c)不能低压根本原因就在于VY=VX=VGS1,被VGS1钳住了,而下面这俩NMOS的饱和条件里其实并不一定要漏极电压这么高对吧,这里其实是浪费的,所以我们就需要将这里的电压释放出来——M1的栅电压借到上面VIN的位置去。从M1和M5的饱和条件很容易得出,VB的取值范围为:VGS4+VGS1-VTH1<=VB<=VGS1+VTH4,化简为:VGS4-VTH1<=VTH4,再变成VGS4-VTH4<=VTH1即VOD4<=VTH1,只要满足这个条件,中间就有VTH1-VOD4=400mV这么宽的一个VB的范围呢,只要在这个范围内M1和M5都饱和。那么,我们设计去让VB为某个值的时候,M1的栅极电压可以释放到最小——即一个VOD。很明显,当设计VB=VGS5+VOD1时,检查其满足上式的饱和条件,此时有VGS1=VGS2=VOD1,输出摆幅吃到极致了。换句话说,偏置的VB的最小值也就是VGS5+VOD1了,仿真时要小心检查。这里再次提出问题:这个地方线性了就咋了?都有什么影响?

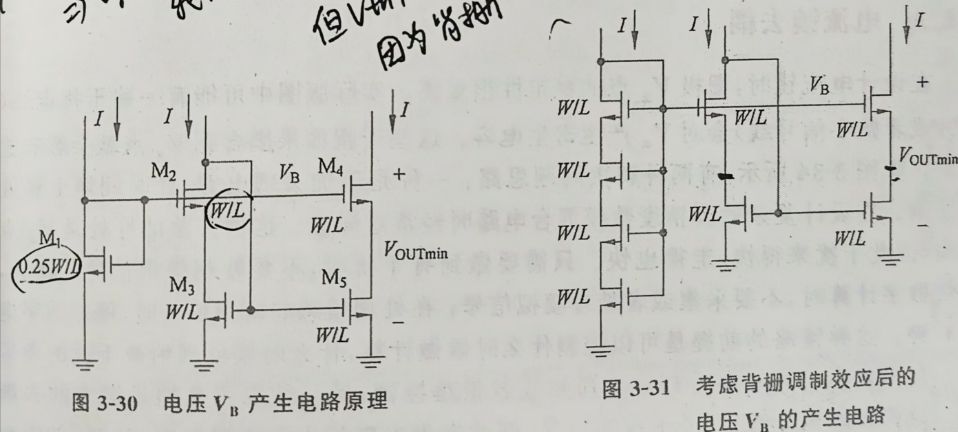

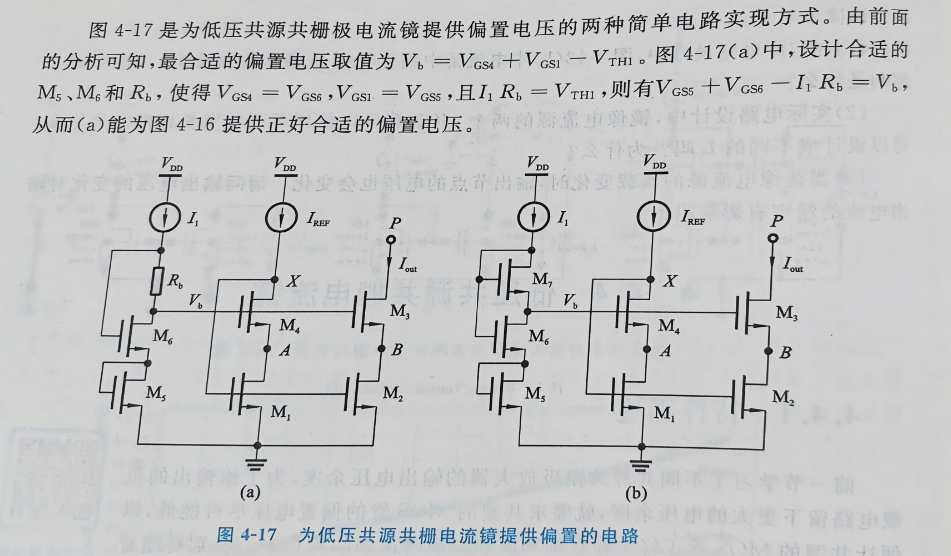

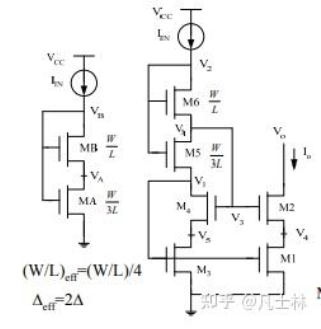

这里的问题是(e)里面的VB的偏置电路怎么设计?比较常见的就是下图的方案:

在左图中,用Iref同时偏置M1和M2支路,M1取M2的1/4宽长比,于是在忽略CLM之后,M1的VOD为M2的两倍,记为VOD1=2VOD2,对于M1管有:VGS1=VOD1+VTH1=2VOD2+VTH1=VOD2+VGS2-VTH2+VTH1,根据上文我们知道最低的VB=VGS2+VOD3,假设VOD2=VOD3,于是M1给VB偏置成功与否取决于VTH1与VTH2的关系,如果它们相等,自然有VB得到最低偏置,下面NMOS的栅极电压裕度被完全释放,输出摆幅达到最低,but not。这里体效应一定起作用使得VTH2>VTH1,于是M1给到的偏置会比VB能接受的最小值低,M3的漏极电压会小于VOD进入线性区。

改进方案如右图,1/4变成4个1的串联。感觉用处不大,毕竟体效应没有被完全改善,还是有风险而且版图难匹配啊。孙楠介绍了比较好用的方案:

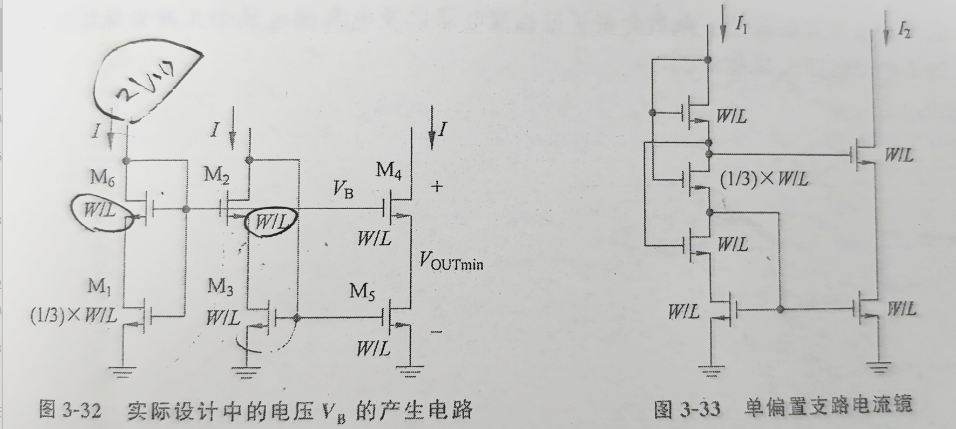

将4个1的串=1/4改为1和1/3的串=1/4,让M6和M2匹配起来。但是可以推算此时最下面NMOS,M3的VDS依然要么刚好等于VOD3,要么小于VOD3,还是有进入线性区的风险。于是实际设计的时候要注意这里把下面的1/3设计成1/5、1/6这样子,这样实际上一等效可以算算,VDS3会给到1.2个VOD3。本质上跟上文的分析一样,你不可能把这个低压结构的低压用到极致,总得用摆幅换取一些PVT的robust吧。右图是孙楠展示的一种用输入电压摆幅去trade功耗的一种做法。可以再展示一下其他的几种方案。

当然,张鸿老师教的直接在M2漏极加电阻的方案算是比较基础的了,但是其实思路是最直接的,下面NMOS的栅极被释放到M2漏极成为VGS电压,那么直接在M2漏极电压上再叠加一个VOD不就获得了VB=VGS+VOD了嘛。当然,这里在设计的时候该注意的也要注意好,裕度的问题,尤其是在用到电阻的时候,也是最好大于一个VOD,但别太大,V2太大了导致V4很高,V1不动则M4的VDS裕度被压缩,进入线性区。但其实我觉得这种方案就挺好,输入电压摆幅牺牲了一个VOD,也不是特别大,减小了一路功耗,多用了电阻面积,具体项目中见仁见智吧。

浙公网安备 33010602011771号

浙公网安备 33010602011771号