跨时钟域处理方法大全

单bit信号跨时钟域:

从慢到快(满足1.5倍周期原则)

两级电平同步;

注意事项:

1.如果慢时钟是clk_slow,快时钟是clk_fast,那么从clk_slow打出的单bit信号宽度至少是clk_fast周期的1.5倍,否则认为是从快到慢;

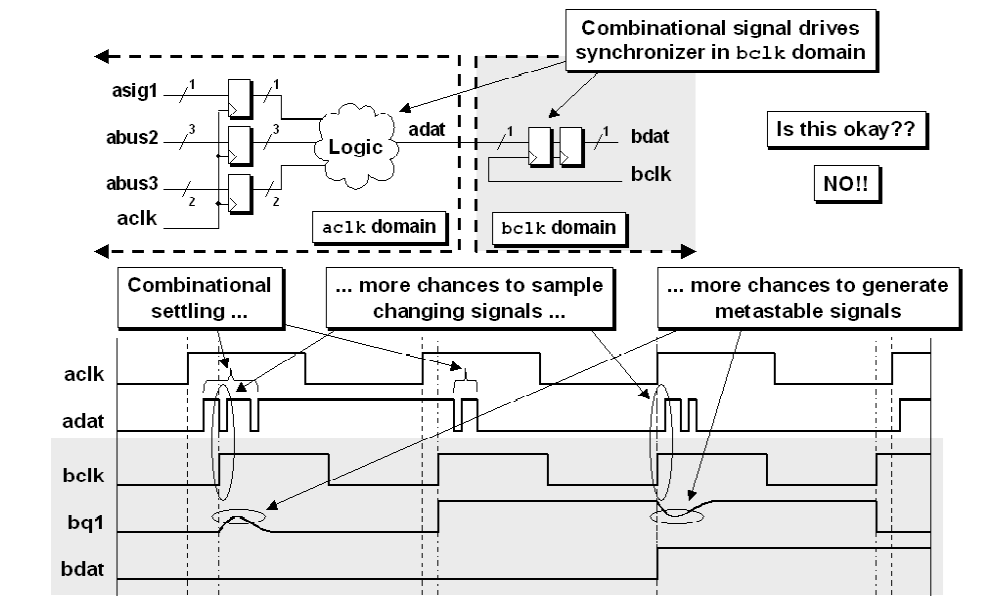

2.从clk_slow同步到clk_fast,从clk_slow打出的信号必须经过clk_slow打过,否则组合逻辑输出会有毛刺,被clk_fast采到,会增大clk_fast时钟域第一级触发器出现亚稳态的概率,从而增大同步器出现亚稳态的概率;如下图所示:

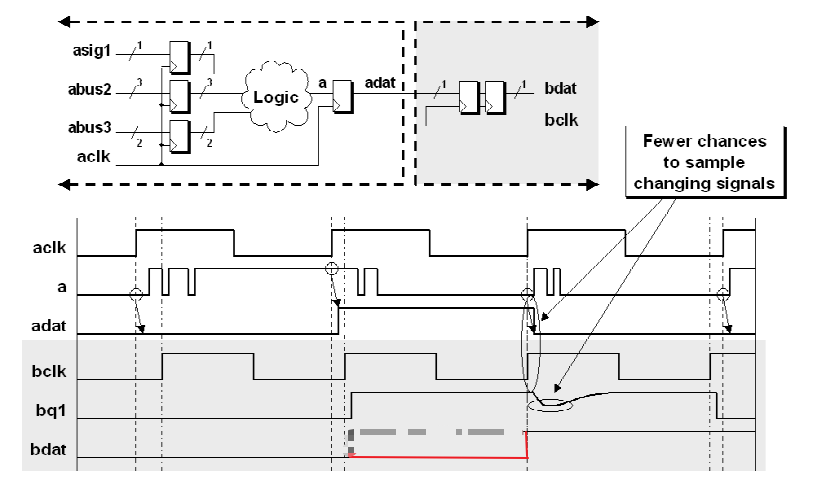

经过clk_slow打过的单bit信号adat的跨时钟域如下图所示:

虽然,2种情况结果一致,但是需要注意的是经过clk_slow打拍之后的同步,亚稳态概率降低。

从快到慢:

单bit从clk_fast跨时钟域到clk_slow

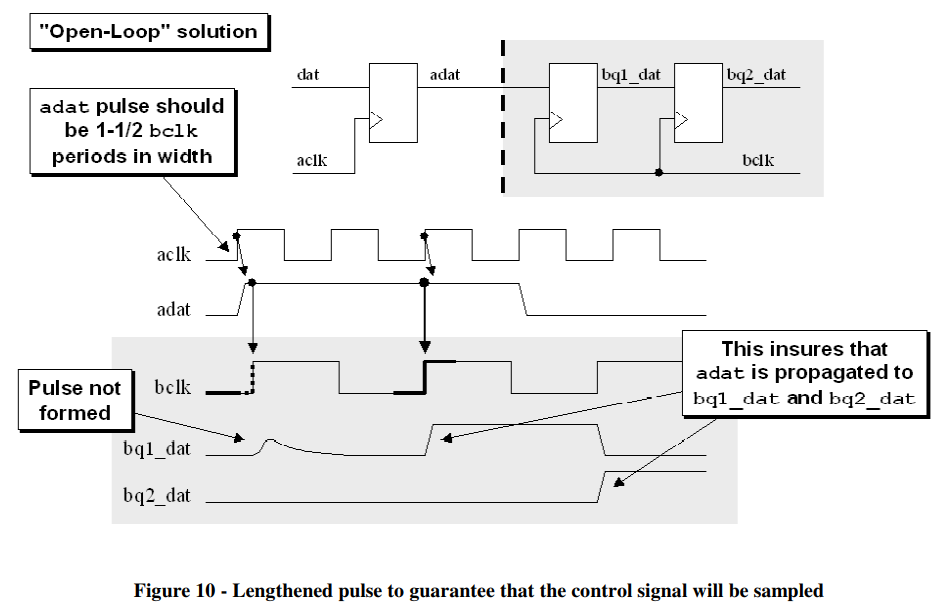

方法1:开环控制

展宽clk_fast时钟域的信号宽度到大于等于1.5倍clk_slow时钟域周期,这样可以保证信号被clk_fast采集到,但是这样的话,对clk_fast和clk_slow的频率有一个约束关系,当设计改动clk_fast和clk_slow频率变化时,可能需要重新修改代码,这种设计不具有健壮性,如下图所示:

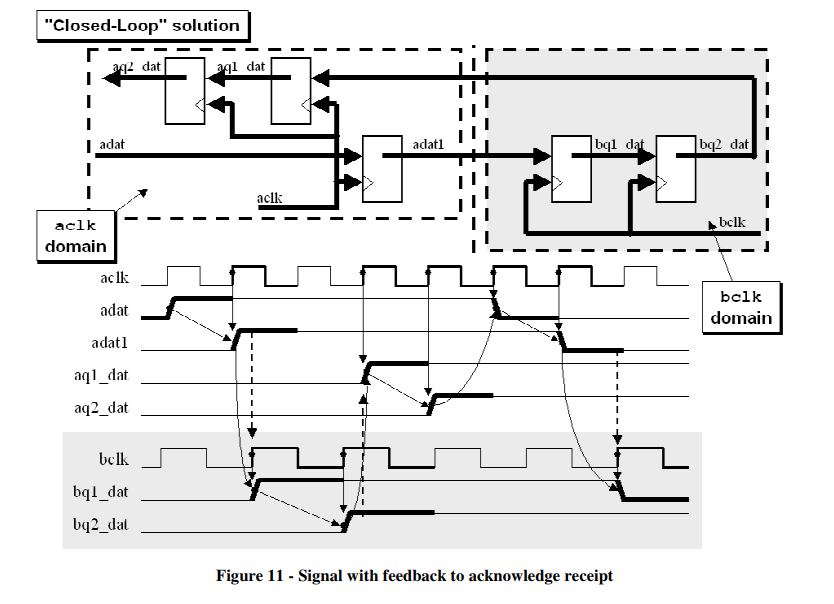

方法2:闭环控制

使用反馈信号自动延长快时钟域的信号;

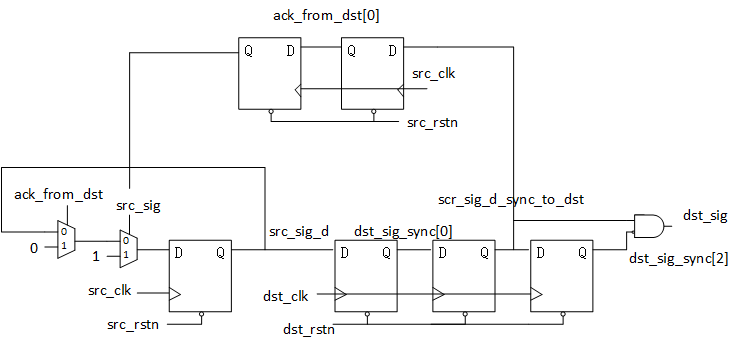

其中一种做法是使用脉冲同步器(genpart_pulse_sync):

这种脉冲同步器可以接受单周期脉冲,也可以接受多周期脉冲,设计理念是如果Input没有拉低,那么就不会让ack_from_dst拉低src_sig_d;

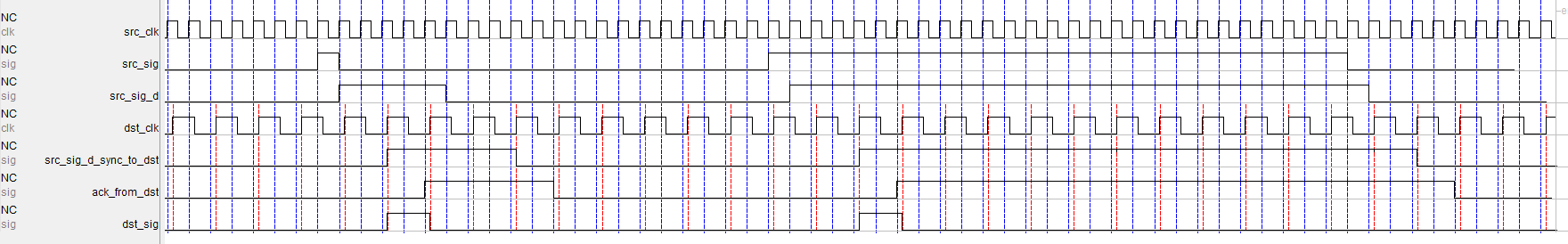

时序如下图所示:

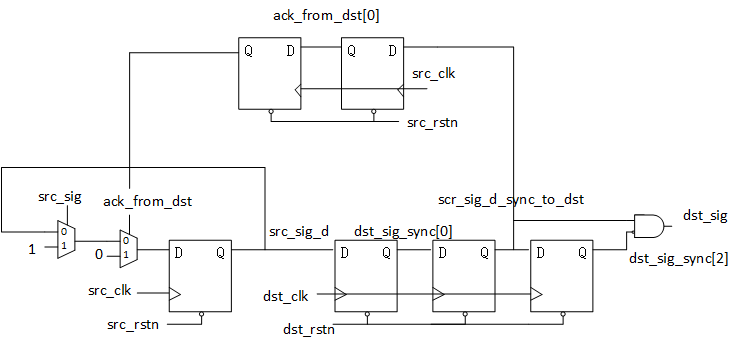

还有一种脉冲同步器,只能接受单周期脉冲:

那么这时,如果src_sig不是单周期脉冲,可以将src_sig取沿做成单周期脉冲,然后再给到此脉冲同步器;

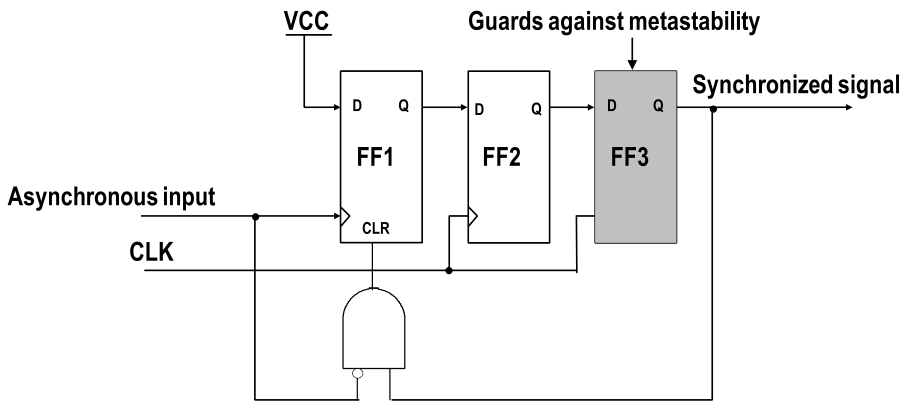

clk_fast时钟域的一个脉冲信号,宽度只有快时钟域的一个周期,将该信号同步到clk_slow,如果不在快时钟域把脉冲信号展宽,实现方法可以用下面这种剑走偏锋的方法:

时序如下图所示:

多bit信号跨时钟域

多bit信号的跨时钟域方案都需要符合从快到慢和从慢到快的使用场景;

有5种多bit信号的处理方式:

方式1.根据多bit信号之间的关系,看能否合并成单根信号,或者多bit信号之间有明确的时序关系,变成一个单bit信号,其他bit信号由此单bit信号产生;

方式2.格雷码计数器;

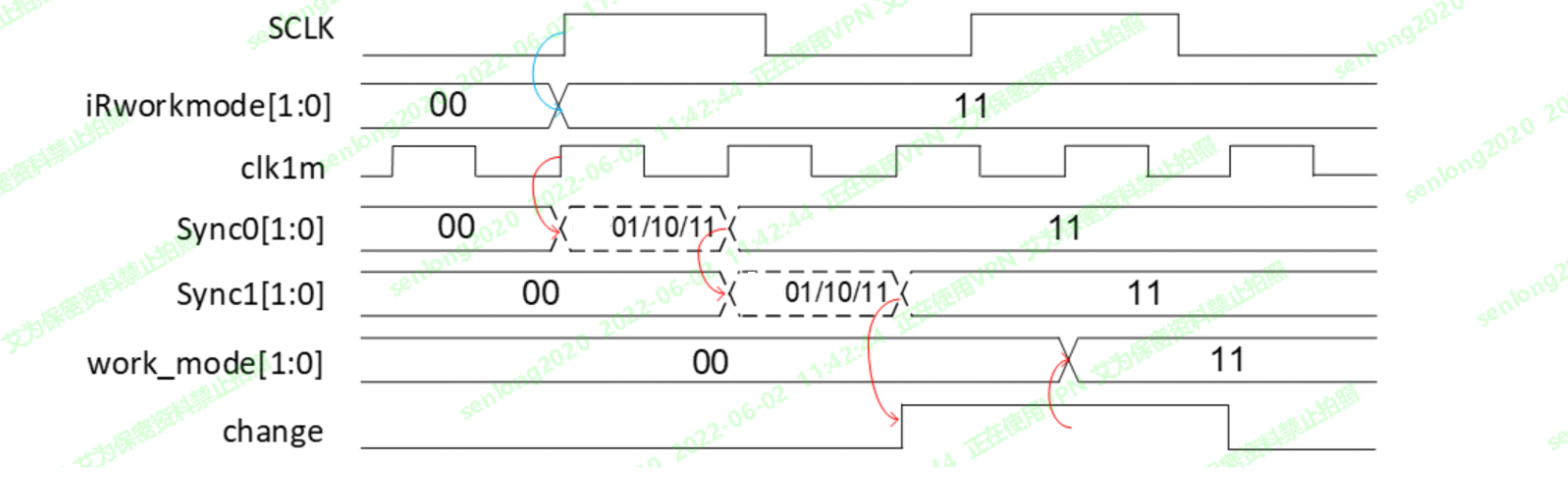

方式3.Multi-Cycle-Path Formulation方法,本质是用控制信号从clk_fast同步到clk_slow,然后被被同步到clk_slow的控制信号再去控制clk_fast的数据打到clk_slow,在此期间,clk_fast的数据保持不变,之后的握手机制是为了消除开环结绳法的限制;

方式4.异步FIFO;

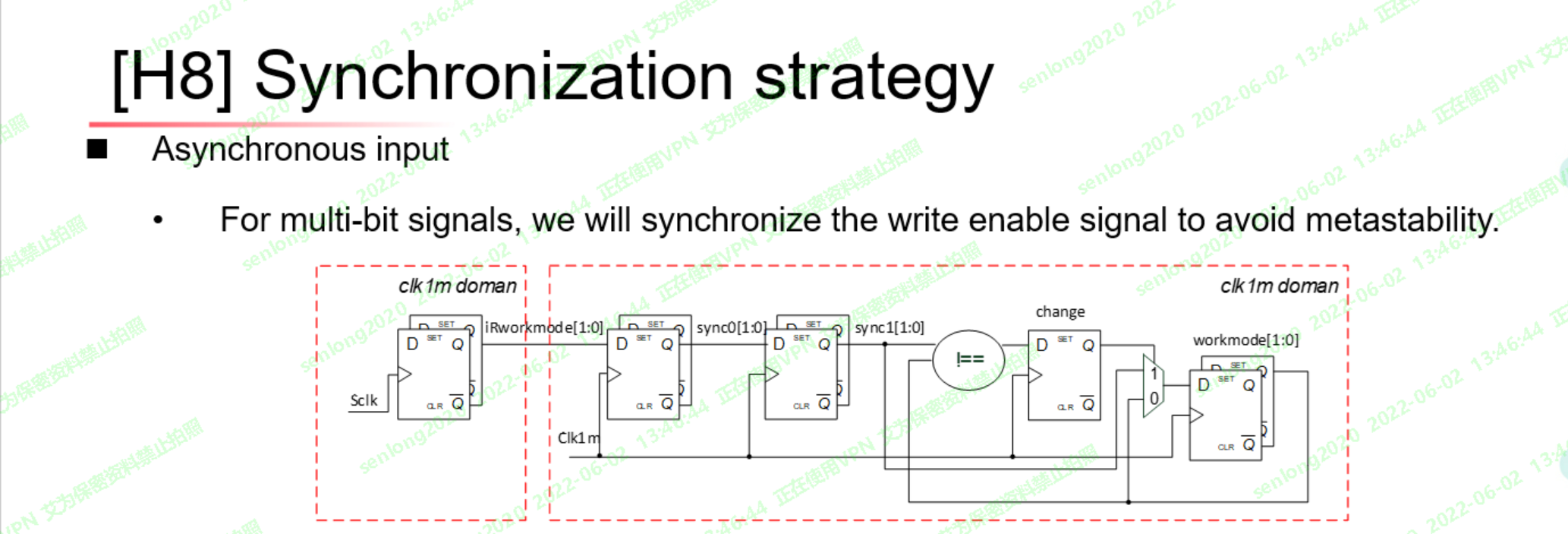

方式5:多bit信号同步器

方式1:

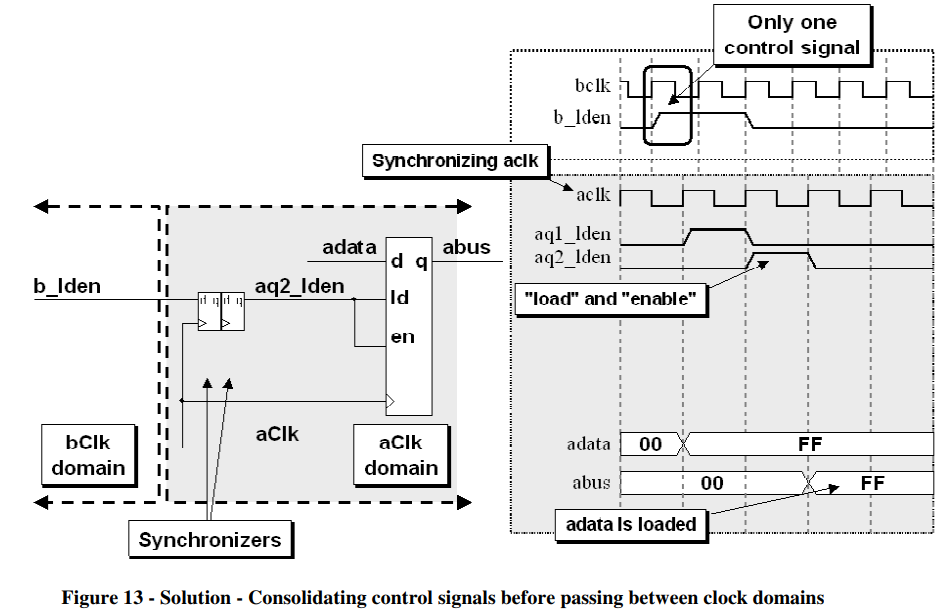

load和en作为两个控制信号需要跨时钟同步。两个信号需要同时拉高才能正确操作,但是实际同步时可能两者存在一定skew,导致再同步域两级reg同步后两个信号错开,导致控制失败:

解决方法:将b_load和b_en合并成一根信号b_lden:

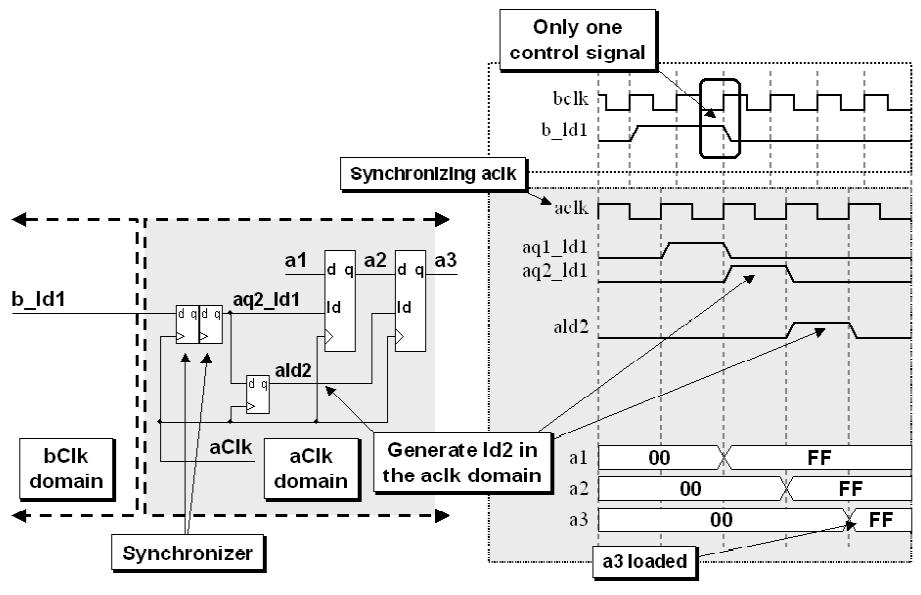

控制信号多比特之间有一定时钟相位差,这种情况下,如果两个信号隔开固定的相位,在传输过程中可能会有一定偏移,则同步时也会导致同步后的信号错开,造成同步失败:如下图种aq2_ld1和aq2_ld2相位增大;

解决方法:只传输其中一个信号,另一个信号在同步域内产生,如将aq2_ld1在aClk时钟域打一拍得到ald2,aq2_ld1和ald2相位关系不变;

方式2.格雷码计数器;

因为相邻的2个格雷码之间只有1bit不同,那么被另一个时钟域时钟采样的那一刻,只会有1bit发生变化,因此多bit格雷码跨时钟域传输,可被视为单bit信号传输,用单bit信号传输的方法进行跨时钟域传输;

单bit信号跨时钟域传输方法:例如2级同步,那么格雷码多bit信号就和单bit信号跨时钟域一样,需要满足慢时钟域打出信号宽度是快时钟域的1.5倍,此时每一个格雷码都不会丢失,如果是快到慢,慢时钟采到的格雷码之间是跳跃的,会丢失一些格雷码,并且采到的格雷码的值是当前值或上一个值,看使用情况,例如异步FIFO中使用的就是这种方式;

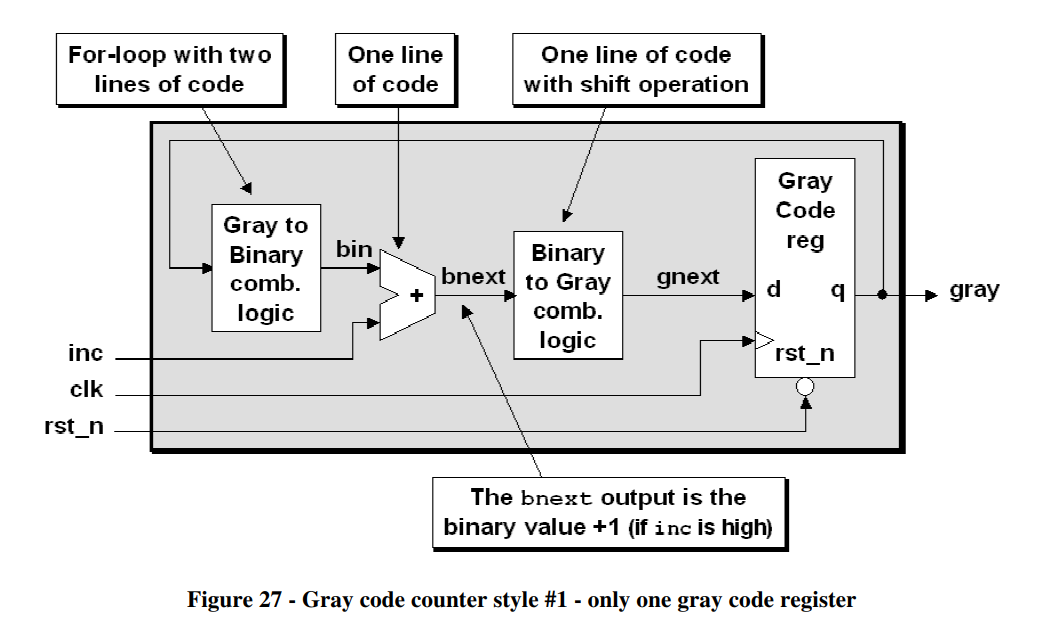

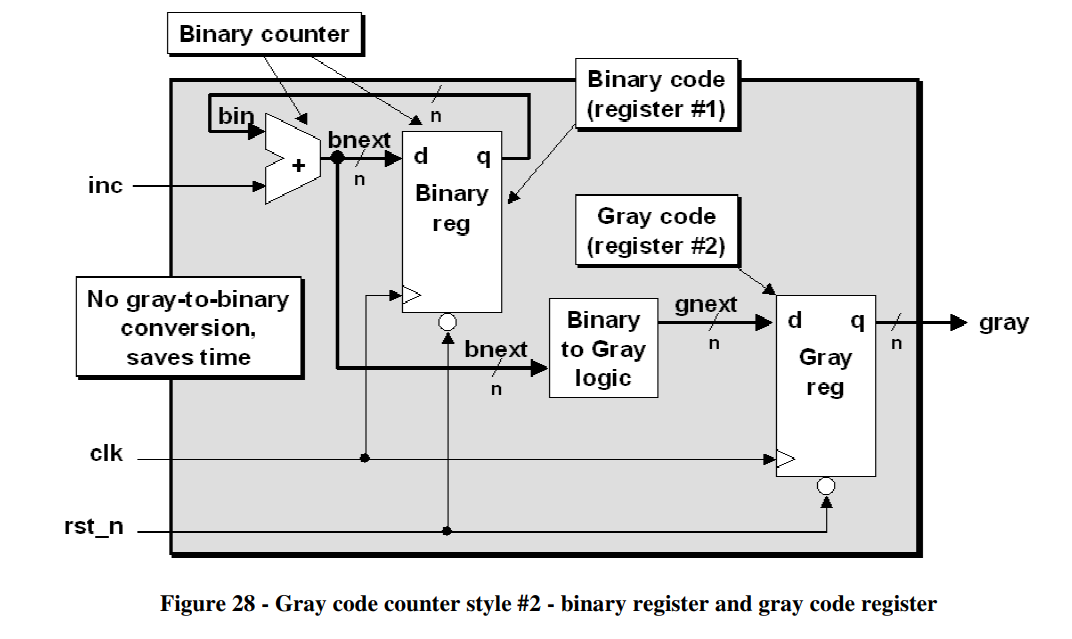

格雷码计数器适合同步二进制计数器,有2种产生格雷码计数器的方式:

方式1:

方式2:

方式3.Multi-Cycle-Path Formulation方法,本质是用控制信号从clk_fast同步到clk_slow,然后被被同步到clk_slow的控制信号再去控制clk_fast的数据打到clk_slow,在此期间,clk_fast的数据保持不变,之后的握手机制是为了消除开环结绳法的对脉冲之间间隔的限制;

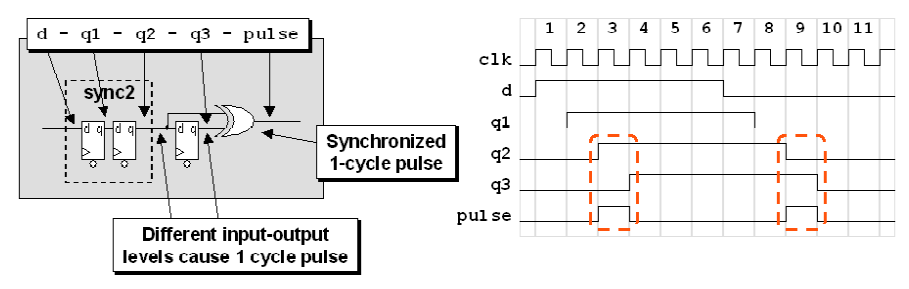

首先介绍脉冲产生电路:

然后可以将此电路简化为:

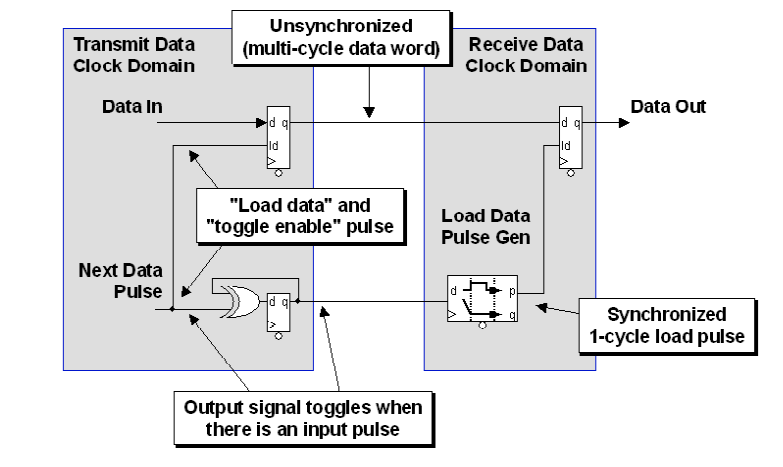

开环结绳法:

用脉冲同步器先同步单脉冲信号Next Data Pulse,然后用同步后的沿load Data In到Data Out;

限制:1.Next Data Pulse为单脉冲 2. 2个Next Data Pulse之间间隔至少为3个接收时钟域时钟周期;

这种电路快到慢,慢到快都可以;

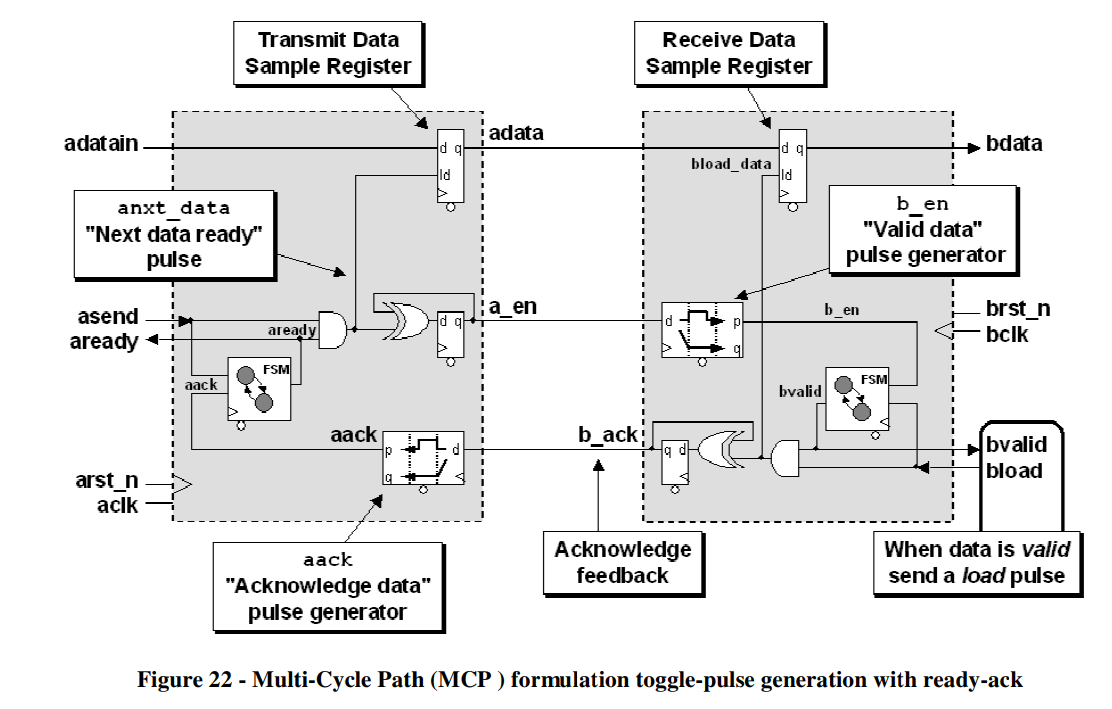

为了摆脱限制,可以使用握手机制,即为闭环结绳法: (asend为单脉冲)

这种电路快到慢,慢到快都可以;

这种电路多了一个aready信号通知发送端可以发送数据,但是要求接收端始终做好接收数据的准备,因为b_en一来,数据adata就会打到到bdata,接收端就要能够接收bdata;

note:这里“接收端”是指b_data传递给的电路;

为了接收端不用始终做好接收数据的准备,可以在接收端也做一个握手机制,bvalid代表Receive Data Sample Register的D端数据是valid,此valid信号通知接收端可以接收数据,然后接收端发出bload,来告诉接收时钟域可以把adata load到bdata。

note:这里“接收端”是指b_data传递给的电路;

如下图所示:

(asend为单脉冲)

方式4. 异步FIFO

参考Cummings的FIFO雄文:《Simulation and Synthesis Techniques for Asynchronous FIFO Design》

方式5:

数据同步错误的情况:

数据同步正确的情况:

浙公网安备 33010602011771号

浙公网安备 33010602011771号