建立时间和保持时间(setup time 和 hold time)

建立时间和保持时间贯穿了整个时序分析过程。只要涉及到同步时序电路,那么必然有上升沿、下降沿采样,那么无法避免setup-time 和 hold-time这两个概念。本文内容相对独立于该系列其他文章,是同步时序电路的基础。

针对xilinx手册中一些概念的更新和术语的规范化,以及存在的一些问题,参考文档为UG906,已进行了一系列修改。--2019/5/5

系列目录

建立时间和保持时间(setup time 和 hold time)

OFFSET约束(OFFSET IN 和OFFSET OUT)

Clock Skew , Clock uncertainly 和 Period

1. 什么是setup-time 和 hold-time

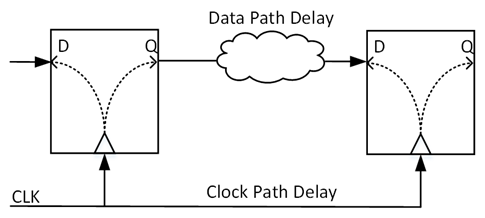

同步时序电路设计中,只在时钟的上升沿或下降沿进行采样。为了正确得到采样结果,需要确保采样时刻数据有效,因此工具会对综合结果进行静态时序分析,以判断时钟和数据之间的相对关系是否满足要求。以寄存器-寄存器之间的路径为例子

图1

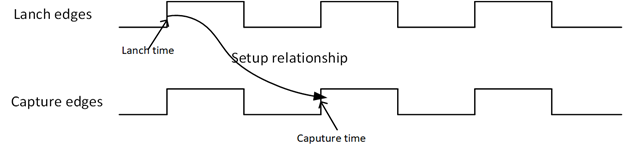

图2

- 发射时间(launch edge):源时钟发射数据的时刻

- 采样时间(capture edge):目的时钟采样数据的时刻(显然采样时刻要晚于发射时刻)

而Setup time和Hold time,按照维基百科的解释为

Setup time is the minimum amount of time the data signal should be held steady before the clock event so that the data is reliably sampled by the clock. This applies to synchronous input signals to the flip-flop.

Hold time is the minimum amount of time the data signal should be held steady after the clock event so that the data are reliably sampled. This applies to synchronous input signals to the flip-flop.

无论是Setup time 或者Hold time,都是指时间上的相对关系;在具体分析过程中,时钟有发射时钟和采样时钟,而各个路径上的数据也有不同的延时,因此仅提及Setup time/Hold time往往有指代不清的问题。因此,Xilinx在UG902中明确了

- setup relationship:时序分析工具给出的launch edge和capture edge之间setup关系

- setup requirement:launch edge和capture edge之间最严格的setup约束(分析得到所有的setup relationship中的最小值)

- hold relationship:时序分析工具给出的launch edge和capture edge之间hold关系

- hold requirement:launch edge和capture edge之间最严格的hold约束(分析得到所有的hold relationship中的最大值)

如图2所示,在同一理想时钟下,假设时钟周期为5ns;lanch time记为0ns,则capture time为5ns,此时setup relationship为5ns,hold relationship为0ns。

2. 建立在Setup和Hold上时序分析

建立在上一节基础上,可以对数据的具体采样时刻进行分析,以判断是否在数据有效时刻完成了采样。如果说采样时刻比数据到达时刻晚,则满足了setup的要求。

如图1所示,由于源时钟可能有路径延时,因此Q端的输出会比launch time晚source clock path delay,同时由于在数据路径上有延时,因此到达下一寄存器Q端还需花费datapath delay时间,因此

Data Arrival Time(Setup) = launch edge time + source clock path delay + datapath delay

类似可计算实际的采样时刻

Data Required Time(Setup) = Caputure edge time + destinationclock path delay – clock uncertainty – Synchronous Element Setup time

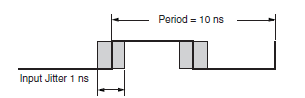

其中Synchronous Element Setup time是寄存器的特性,Clock Uncertainty类似下图所示,由于时钟的不确定性,需要考虑最坏情况。

Xilinx计算Slack来判断是否满足是需要求。Slack的中文意思是“松弛的”,可以简单的理解为设计余量。即如果slack是正数,那么设计满足要求,否则不满足要求。对于setup time的slack,有

Slack = Data Required Time(Setup) - Data Arrival Time(Setup)

如图2所示的理想情况下,Required Time(setup)为5ns,只要datapth delay不大于5ns,那么Slack就能满足要求。

当然,在一个设计中会存在多条路径,所有的Slack均需要满足要求。

类似的,也可以给出Hold的分析结果;与setup不同,要求数据完成采样之后下一个数据才能到达。

Data Arrival Time(hold) = launch edge time + source clock path delay + datapath delay

Data Required Time(Setup) = Caputure edge time + destinationclock path delay + clock uncertainty + Synchronous Element Hold time

Slack = Data Arrival Time(Hold) - Data Requried Time(Hold)

如图2所示的理想情况下,Required Time(Hold)为0ns,只要datapth delay大于0,那么Slack就能满足要求。

浙公网安备 33010602011771号

浙公网安备 33010602011771号