时钟切换的消除毛刺问题

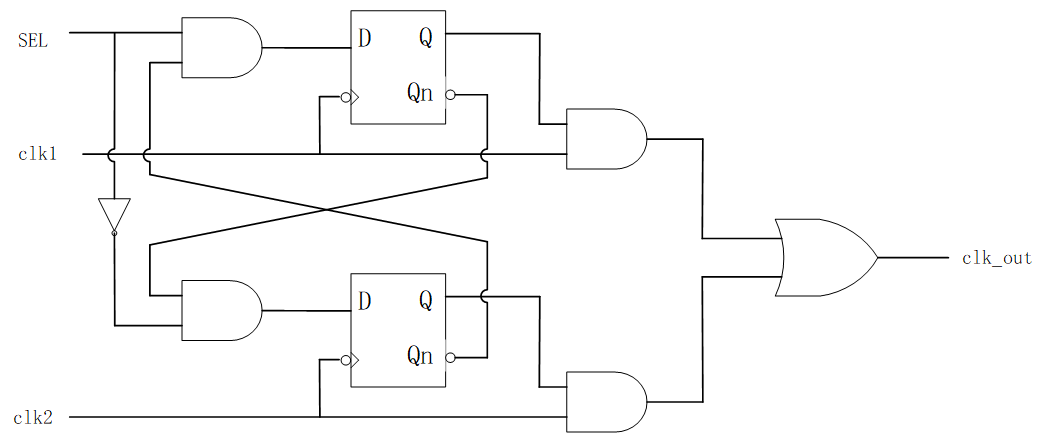

题目中说了是两个同步的倍频时钟clk0 clk1,已知clk0是clk1的二倍频,属于相关时钟,避免切换时毛刺出现,只需要在组合逻辑的基础上添加下降沿触发的DFF。原理图如下:

那么为什么要使用下降沿触发的DFF呢?

原因是这样,所谓去除毛刺,就是要避免毛刺的产生,那么得先明白毛刺是如何产生的,其实只要两个时钟相反时切换都换产生毛刺,如果没有DFF,比如,在clk1为低电平时,sel马上切换到clk0,恰巧clk0为高电平,但高电平只剩一点了,所以便产生了一个高电平毛刺,当然同理也有低电平毛刺。

但在此时钟切换电路中,sel信号的传输存在着DFF的延迟,也就是说在时钟切换时,两个DFF的输出存在都是0的情况,此时clk_out输出为低电平,这段时间可能很短,如果在两个时钟都是高电平的时候切换,可能会产生低电平毛刺,所以考虑要在两个都为低电平的时候切换最为稳妥。

那么使用下降沿触发的DFF,尽管sel已经有切换指令了,但需要等到下降沿后才通过DFF传到后面,因为是下降沿,所以高电平已经结束了,切换过去可确保无毛刺。

通过在每个时钟源的选择路径中插入一个负边沿触发的D触发器,可以确保时钟在高电平时,输出保持不变。 通过这种反馈的方式使得在时钟切换时需要等待当前时钟取消选择,从而避免毛刺的产生。

`timescale 1ns/1ns

module huawei6(

input wire clk0 ,

input wire clk1 ,

input wire rst ,

input wire sel ,

output reg clk_out

);

//*************code***********//

reg sel1, sel0;

always @ (negedge clk1, negedge rst) begin

if(!rst)

sel1 <= 0;

else

sel1 <= sel & ~sel0;

end

always @ (negedge clk0, negedge rst) begin

if(!rst)

sel0 <= 0;

else

sel0 <= ~sel & ~sel1;

end

always @ (*) begin

clk_out <= (sel1 & clk1) | (sel0 & clk0);

end

//*************code***********//

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号