振荡器闪烁相噪学习

Y. Hu, T. Siriburanon and R. B. Staszewski, "Oscillator Flicker Phase Noise: A Tutorial," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 68, no. 2, pp. 538-544, Feb. 2021, doi: 10.1109/TCSII.2020.3043165.

1. 背景

-

急需低闪烁相噪设计的应用场景:

FinFET和FDSOI工艺的闪烁噪声恶化;

5G/6G无线通信、高速接口、量子计算需要极低PN。 -

Hajimiri的ISF理论:

对称波形可以抑制闪烁噪声的上变频;

例如在环振中,增加级数(且保持频率不变)可以获得陡峭的边沿,减小边沿的不对称,可以减小闪烁相噪。 -

之前的关于LC振荡器闪烁噪声上变频的工作大多聚焦于电流偏置VCO

其中有变容管与非线性电容的 AM-FM 机制和 Groszkowski 效应等。

近年来,随着工艺尺寸的减小(MOSFET非线性寄生电容变小)和开关电容的引入(可以有很多个band,调谐范围不受变容管限制,因此变容管面积可以很小),AM-FM 机制变得不是很重要了。而且,振荡器中也常常不含尾电流管(voltage-biased osc.)。因此,本文聚焦于交叉耦合管的 1/f 噪声上变频的机制与改善方法。

2. 分析

2.1 循环平稳 1/f 电流噪声

振荡器中的MOS管电流闪烁噪声,为循环平稳噪声:

其中 I1/f,rms(t) 以振荡器周期 T0 为周期,\(\Delta \omega\) 为较低频率(1\f 噪声的特性)。观察这个电流闪烁噪声(假设大小为正)在不同时刻对振荡波形的影响:

注意图3(a)和(c)之间,只过了 T0/2,VDS(工作点)的相等以及1/f 的低频特性导致两个时间点的循环平稳 1/f 电流噪声大小几乎相等。如果 VDS 振荡波形对称,则 1/f 噪声导致的相位延迟和超前相等,净相位变化为0,闪烁相噪很小。如果波形不对称,则闪烁相噪较大。

如果下降沿缓,则净相移小于0(滞后);如果上升沿缓,则净相移大于0(超前)。

2.2 波形不对称的源头

- 观察共模路径

NMOS振荡器中,共模路径会包括tank电感。

CMOS振荡器中,共模不会走tank电感,而且由于local电源和地很近,Ldecap几乎为0.

![Pasted image 20250731144153]()

- 实际仿真结果

未进行1/f噪声优化的NMOS-only和CMOS振荡器的仿真结果显示,NMOS-only的二次谐波比三次谐波大,而CMOS的三次谐波比二次谐波大。

[!NOTE] 猜想

不同的振荡器,恶化1/f噪声的谐波成分不同。有的是二次谐波会恶化1/f噪声,有的是三次谐波会恶化1/f噪声。

- 进一步分析:谐波如何影响波形的不对称

- 二次谐波:(二次谐波电流与基频电压相位相同)

流经感性、阻性、容性阻抗时的电压

![Pasted image 20250731154944]()

流经电感(\(\omega_{cm,tank} >> 2 \omega_{0}\))使下降沿变缓,流经电阻(\(\omega_{cm,tank} = 2 \omega_{0}\))对称,流经电容(\(\omega_{cm,tank} << 2 \omega_{0}\))使上升沿变缓。

![Pasted image 20250731155035]()

- 三次谐波:(三次谐波电流与基频电压相位相反)

流经阻性、容性阻抗时的电压

![Pasted image 20250731155541]()

流经容性(3次谐波频率远大于谐振腔谐振频率,呈容性)使上升沿变缓,流经阻性(双tank如class-F可以做到)对称。

![Pasted image 20250731155848]()

- 二次谐波:(二次谐波电流与基频电压相位相同)

2.3 如何减小闪烁相噪

- 二次谐波谐振(or not?)

将二次谐波电流IH2的阻抗看做调节VDS陡峭程度的“旋钮”。例如,在CMOS振荡器中,IH3会进入DM tank(呈容性)中,使VDS上升沿变缓,如果加一个CM tank让IH2的阻抗呈阻性/感性的高阻,则VDS上升沿会变陡,使VDS更对称。 - 减小导通角

如class-C。 - 引入VGS相对VDS的相移

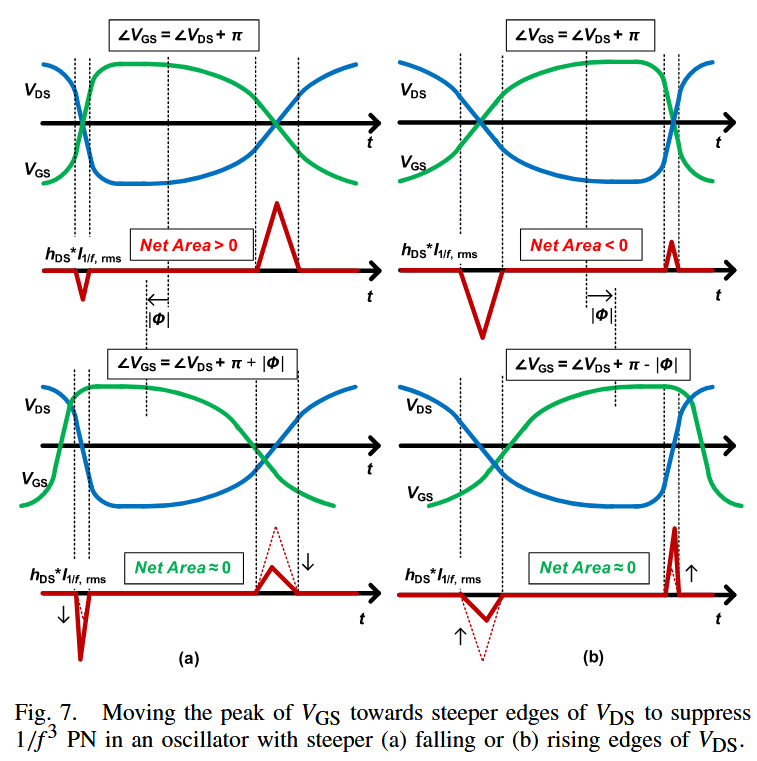

将VGS的峰值向VDS的较为陡峭的边沿移动。例如VDS上升沿陡峭,如图(a),则1/f电流噪声引入的负相移<正相移。如果想办法将VGS左移,则在VDS上升沿注入的1/f噪声电流会变大,可以其引入的负相移=正相移,减小1/f噪声引入的PN。

引入相移的方法:在CMOS振荡器中的变压器中,使用电容比例来做相移。

![Pasted image 20250804150024]()

浙公网安备 33010602011771号

浙公网安备 33010602011771号