verilog语法

状态

verilog中对于状态的描述一共有四个

- 1:高电平

- 0:低电平

- x:未知,可以是高电平也可以是低电平

- z:高阻态,悬空状态

进制

verilog的进制和其他语言有很大的不同

- 二进制:4'b0101表示四位二进制的0101

- 十进制:4'd2表示四位十进制的2

- 十六进制:4'ha表示四位十六进制的a

总之前面的4是指位宽后面的是指进制等

标识符

类似变量名,用于定义变量、模块名、端口名、信号名等

标识符的第一个符号不能是数字

数据类型

verilog中主要有三大数据类型

- 寄存器数据类型

- 线网数据类型

- 参数数据类型

这三大数据类型中真正起作用的是寄存器和线网数据类型,参数其实就是中间过度的东西

寄存器数据类型(reg)

只能在always和initial中被赋值,默认初始值是不定值x。

如果过程描述时序逻辑,即always带有时钟信号则寄存器变量为对应的触发器

如果过程描述组合逻辑,即always不带有时钟信号则寄存器变量为对应的硬件连线

其实就是一个器件。

在定义的时候需要在末尾加上分号,reg 【31:0】name;其中中括号表示位宽,高位在前地位在后,若未给出默认位宽为1.

线网数据类型(wire)

表示结构体之间的物理连线,并且线网不能存储值,它的值由驱动它的原件所决定的。

驱动线网的变量的元件有,门、连续赋值语句、assign等。

如果没有驱动元件连接到线网上则该变量为高阻态z。

线网数据类型wire、tri(很少用)

wire name;

wire [31:0] name;

参数类型(常量 parameter)

有define的效果

parameter name = 4'b0101;

如果定义多个参数除了最后一个参数其他用逗号隔开就行

运算符

与c基本一致

其中拼接运算符:

c={a,b[3:0]};

c[3:0]={a,b[3:0]};

程序框架

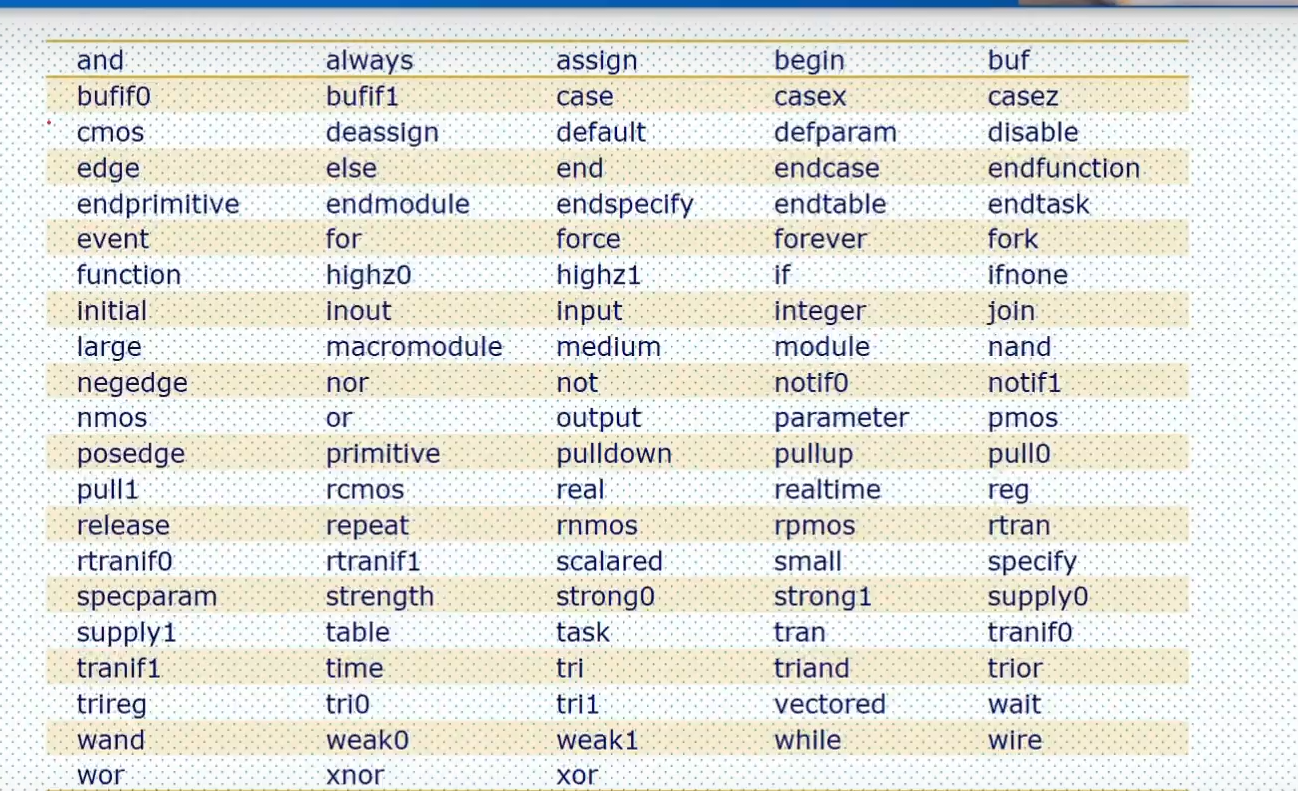

关键字

模块的结构

verilog的基本设计单元是模块

由两部分组成,一个部分描述接口,另一部分描述逻辑功能。

每个verilog包括四个主要的部分:端口定义、io说明、内部信号说明、功能定义

assign给线网赋值的方法

fpga最后都可以综合成器件,当然也由不可综合的语句主要用于仿真软件

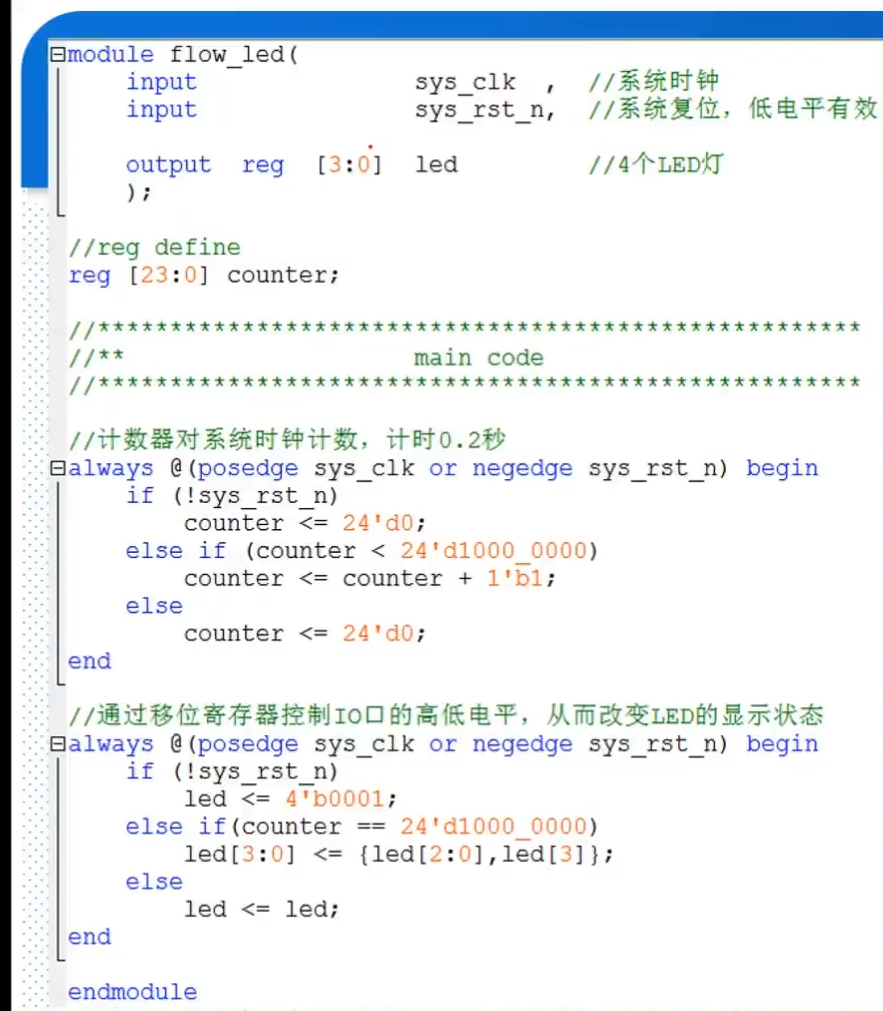

完整的程序结构:

需要注意的是每一个逻辑语句都是并行的,而在always语句中是顺序的,多个always语句是并行的

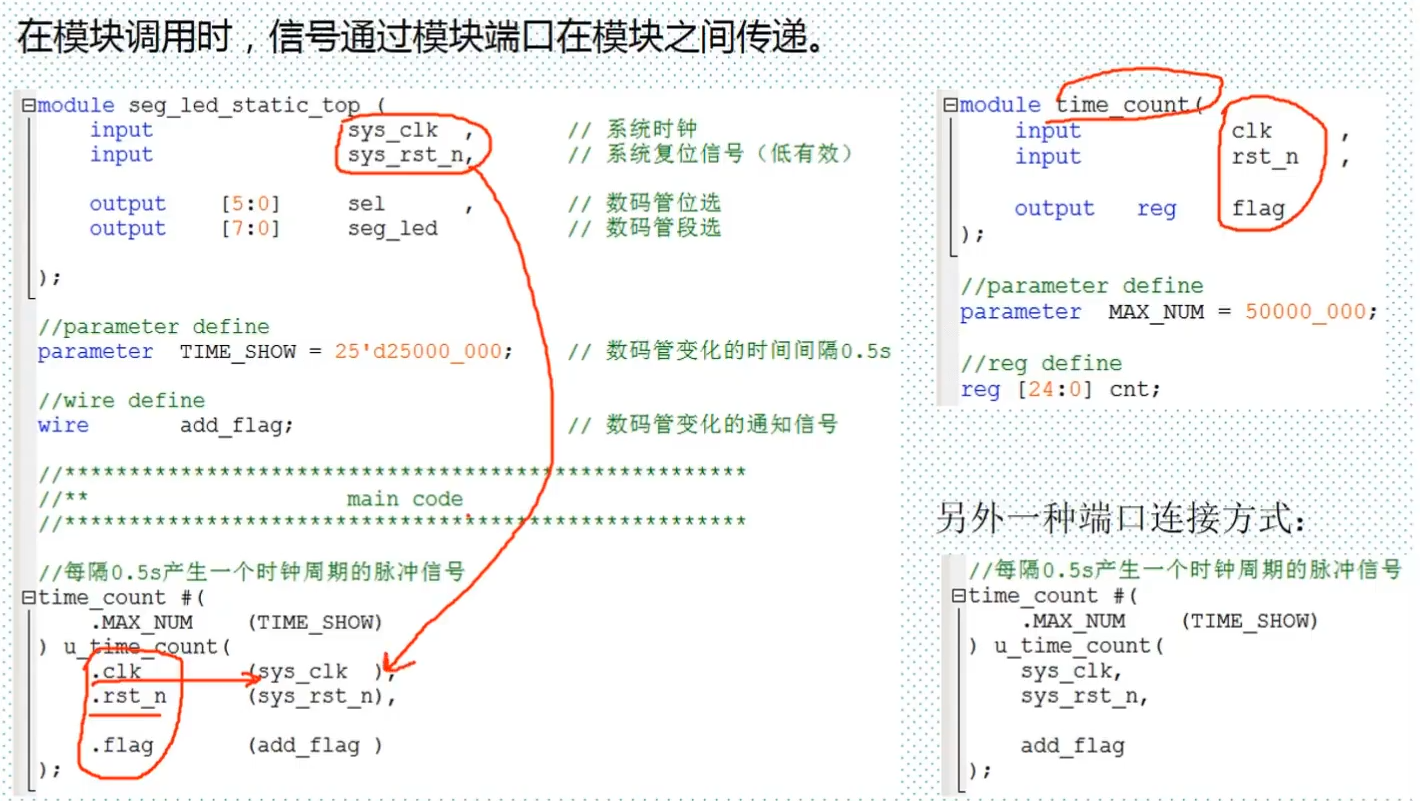

模块的调用

调用很简单,一目了然

结构语句

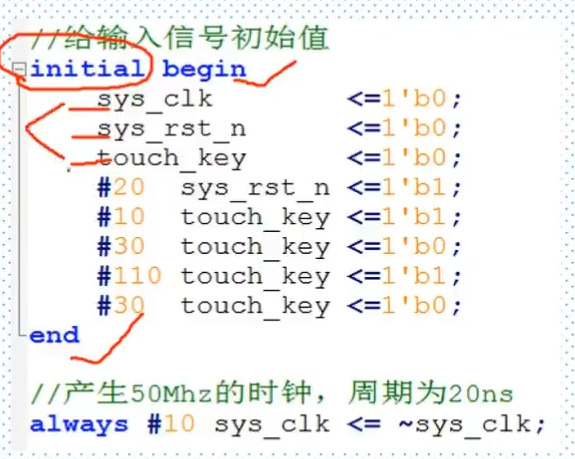

initial和always

initial:只执行一次

常用于测试文件,在仿真时候产生激励信号或者赋予初值。

立刻执行和延时执行

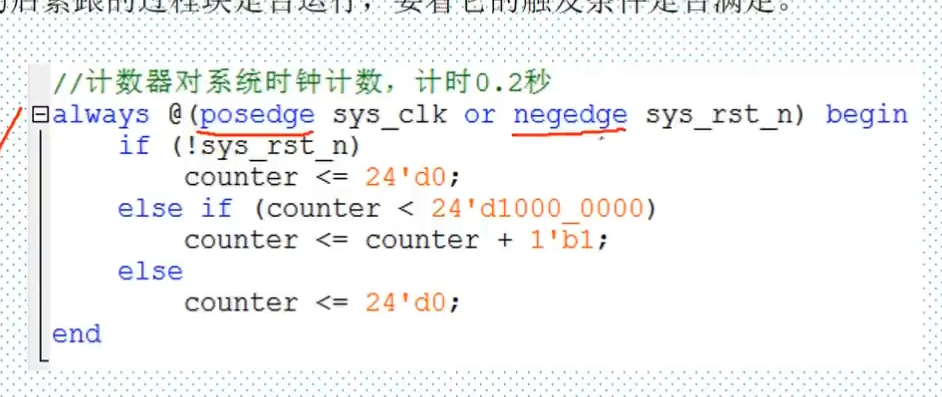

always:重复执行

但是只有和一定的时间控制结合才能有作用

可以是沿触发也可以是电平触发,可以是单个信号也可以是多个信号

沿触发posedge上升沿negedge下降沿,其中or来描述组合逻辑。如果括号中设置为*表示所用到的输入变量有变化就执行

赋值

阻塞赋值 =

非阻塞赋值 <=

阻塞赋值

计算右边并更新左边

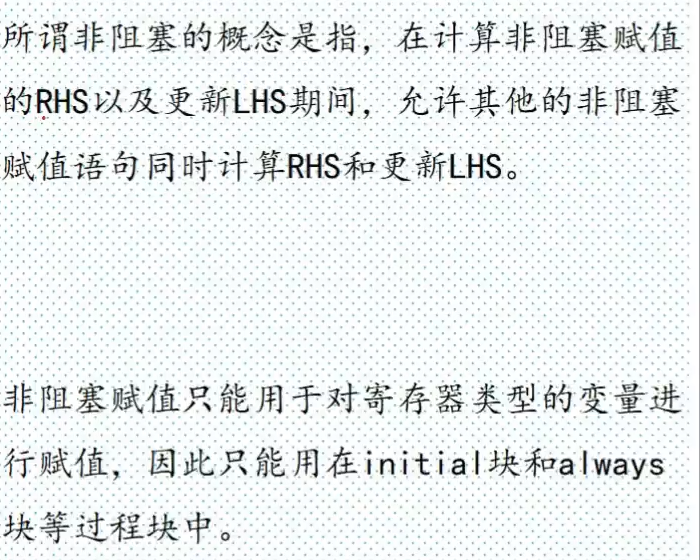

非阻塞赋值

赋值开始的时候计算右边

赋值结束的时候更新左边

是在触发的时候不赋值,下一个周期才赋值,所以只能用在时序逻辑电路里面。

条件语句

if else

注意事项:

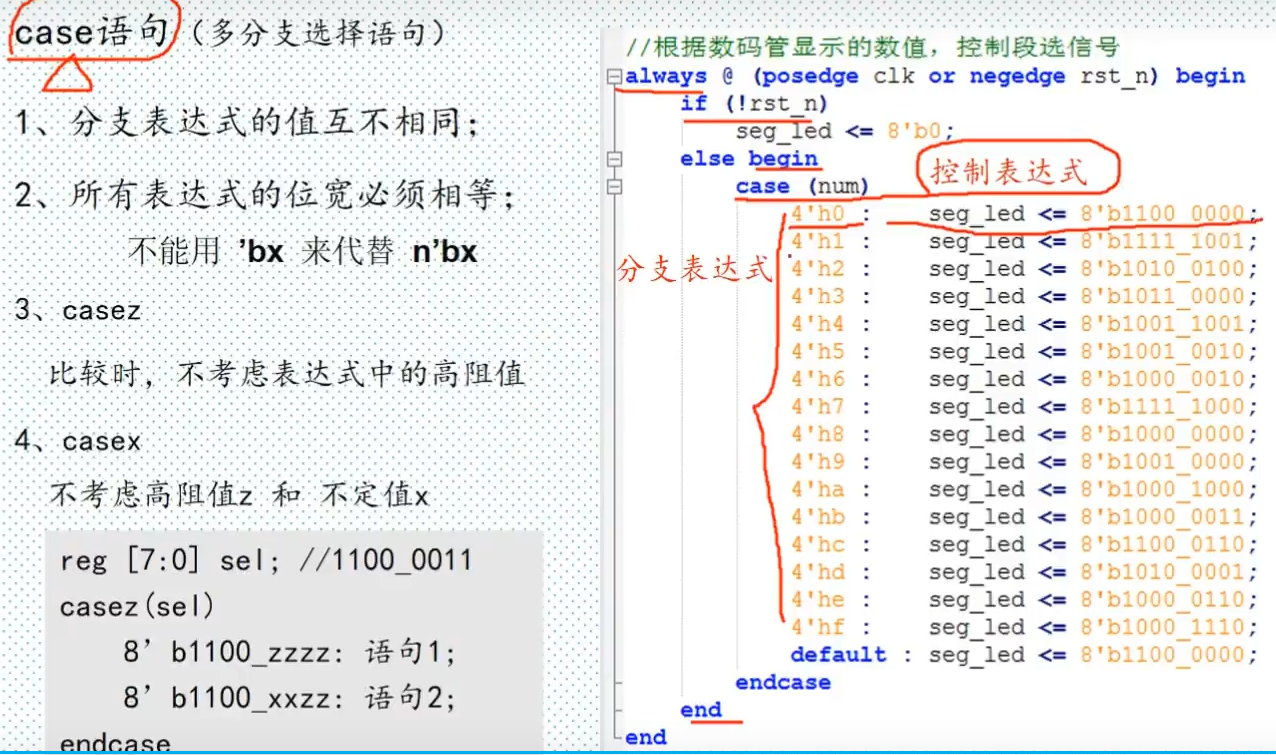

case

不考虑就是遇到任何zzzz或者xxxx都不考虑,前面的符合就行

浙公网安备 33010602011771号

浙公网安备 33010602011771号