STM32之glossary

glossary

- Word: data/instruction of 32-bit length.

- Half word: data/instruction of 16-bit length.

- Byte: data of 8-bit length.

- Double word: data of 64-bit length.

- IAP (in-application programming): IAP is the ability to reprogram the Flash memory of a microcontroller while the user program is running.

- ICP (in-circuit programming): ICP is the ability to program the Flash memory of a microcontroller using the JTAG protocol, the SWD protocol or the bootloader while the device is mounted on the user application board.

- I-Code: this bus connects the Instruction bus of the CPU core to the Flash instruction interface. Prefetch is performed on this bus.

- D-Code: this bus connects the D-Code bus (literal load and debug access) of the CPU to the Flash data interface.

- Option bytes: product configuration bits stored in the Flash memory.

- OBL: option byte loader.

- AHB: advanced high-performance bus.

- CPU: refers to the Cortex®-M4 with FPU core.

System architecture

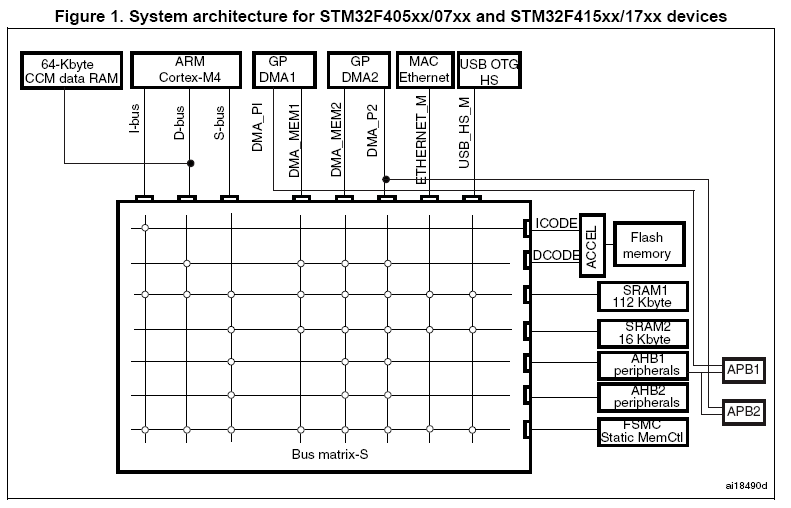

STM32F405xx/07xx and STM32F415xx/17xx, the main system consists of 32-bit multilayer AHB bus matrix that interconnects:

The main system consists of 32-bit multilayer AHB bus matrix that interconnects:

• Eight masters:

– Cortex® -M4 with FPU core I-bus, D-bus and S-bus

– DMA1 memory bus

– DMA2 memory bus

– DMA2 peripheral bus

– Ethernet DMA bus

– USB OTG HS DMA bus

• Seven slaves:

– Internal Flash memory ICode bus

– Internal Flash memory DCode bus

– Main internal SRAM1 (112 KB)

– Auxiliary internal SRAM2 (16 KB)

– AHB1 peripherals including AHB to APB bridges and APB peripherals

– AHB2 peripherals

– FSMC

The bus matrix provides access from a master to a slave, enabling concurrent access and efficient operation even when several high-speed peripherals work simultaneously. The 64-Kbyte CCM (core coupled memory) data RAM is not part of the bus matrix and can be accessed only through the CPU. This architecture is shown in Figure 1.

浙公网安备 33010602011771号

浙公网安备 33010602011771号