【自学嵌入式:计算机组成原理】36. 优化内存的走线

36. 优化内存的走线

寄存器、内存设计与时间空间权衡策略

一、寄存器的信号线构成与扩展

寄存器是CPU内部的高速临时存储单元,其信号线数量由数据位宽和控制信号共同决定。

1. 16位寄存器的信号线计算

一个完整的16位寄存器需传输以下信号:

- 数据输入(Din):16条线(对应16位二进制数据,每位独立传输);

- 写使能(WE):1条线(控制是否将Din的数据写入寄存器);

- 时钟(Clock):1条线(同步数据存储时机,如边缘触发锁存);

- 输出使能(OE):1条线(控制寄存器是否向外输出数据);

- 数据输出(Dout):16条线(输出寄存器保存的16位数据)。

总信号线数量为:

\[16\ (\text{Din}) + 1\ (\text{WE}) + 1\ (\text{Clock}) + 1\ (\text{OE}) + 16\ (\text{Dout}) = 35

\]

2. 64位寄存器的信号线扩展

对于64位寄存器,数据位宽翻倍,因此:

- Din和Dout各需64条线(对应64位数据);

- WE、Clock、OE仍各需1条线(控制信号与位宽无关)。

总信号线数量为:

\[64\ (\text{Din}) + 1\ (\text{WE}) + 1\ (\text{Clock}) + 1\ (\text{OE}) + 64\ (\text{Dout}) = 131

\]

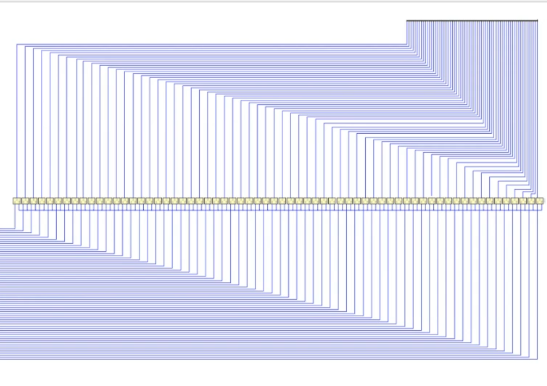

3. 内存地址的核心价值:简化硬件连线

若直接用“寄存器式并行连线”设计大容量内存(如1GB),信号线数量将无法工程实现(需百万级连线)。内存通过地址编码解决此问题:

- 用地址线替代“每位数据的并行线”,通过“行(row)+ 列(column)”定位单个内存单元;

- 示例:10位地址线可编码 ( 2^{10} = 1024 ) 个单元,仅需10条线,而非1024条并行线。

二、内存单元的设计逻辑:从并行到串行

内存由单元阵列组成,每个单元需精准定位与控制,核心是“用地址编码替代并行连线”。

1. 内存单元的基础信号

单个内存单元需以下控制与数据信号:

- 行选择(row):定位单元所在的行;

- 列选择(column):定位单元所在的列;

- 读控制(ld,load):触发数据从单元读出;

- 写控制(str,store):触发数据写入单元;

- 数据输入(Din):待写入的1位数据;

- 数据输出(Dout):读出的1位数据。

2. 地址编码的工作流程

内存通过地址译码器将二进制地址转换为“行+列”选择信号,流程如下:

- 地址总线输入n位地址(如16位地址可编码 ( 2^{16} = 65536 ) 个单元);

- 译码器拆分地址为“行地址”和“列地址”,激活对应行、列的选择信号;

- 仅被选中的单元响应ld/str信号,执行读/写操作。

→ 用n条地址线即可控制 ( 2^n ) 个单元,大幅减少物理连线数量。

三、时间与空间的四大权衡策略

计算机系统中,时间(运行速度)与空间(硬件资源)需动态权衡,典型策略有四类:

1. 时间换空间(串行输出)

- 核心逻辑:牺牲速度,减少硬件资源占用。

- 示例:串口通信(UART),将8位并行数据逐位串行输出,仅需1条数据线,但传输8位数据需8个时钟周期(速度慢于并口)。

2. 空间换时间(并行输出)

- 核心逻辑:牺牲硬件资源,提升运行速度。

- 示例:并口通信(如早期打印机接口),用8条数据线同时传输1字节,1个时钟周期即可完成,但需更多物理连线。

3. 时间换时间(流程优化)

- 核心逻辑:不直接消耗硬件资源,通过时间调度提升效率。

- 示例:CPU流水线技术,将指令执行拆分为“取指、译码、执行”等阶段,让前一条指令的后续阶段与后一条指令的前期阶段并行执行,用时间重叠提升整体吞吐量。

4. 空间换空间(DMA与硬件加速)

- 核心逻辑:通过专用硬件(如DMA控制器)优化数据路径,间接简化系统整体复杂度。

- 示例:DMA(直接内存访问)允许外设直接与内存交换数据,无需CPU全程参与,减少CPU资源占用(硬件:增加DMA控制器;收益:CPU可执行其他任务,系统整体“空间复杂度”降低)。

总结

- 寄存器设计:位宽越大,并行数据线需求越多,需通过内存地址编码优化硬件连线;

- 内存核心思想:用地址线替代并行数据线,通过“行+列选择”大幅减少物理连线;

- 时间-空间权衡:四类策略覆盖不同场景,需结合需求选择(如串口省线但慢,DMA用硬件换系统效率)。

理解寄存器、内存的设计逻辑与时间空间权衡,可掌握计算机“存储系统优化”的核心思想——用编码、调度等手段平衡硬件资源与运行效率。

浙公网安备 33010602011771号

浙公网安备 33010602011771号