varilog 设计初步介绍

varilog设计基础知识

varilog功能与特点

描述逻辑门,如and,or,nor都在内置中,可以直接调用

描述基本开关模型,如cmos;

可采用多种方式建模,如顺序行为描述方式---使用过程化结构化结构建模,数据流行为描述--使用连续赋值语句建模,结构化方式--使用门和模块实例描述。

varilog有两种数据类型,wire--线网型,表示器件间的物理连线;reg--寄存器型,表示抽象数据存储元件(在always过程块中赋值的数据必须声明为reg型)

全加器:全加器是能够计算低位进位的二进制加法电路。与半加器相比,全加器不只考虑本位计算结果是否有进位,也考虑上一位对本位的进位(这是和半加器的本质区别,虽然半加器输出也有进位但是它没有进位加法器),可以把多个一位全加器级联后做成多位全加器。全加器输入有前一次运算的进位,加数,被加数,输出有此次运算的进位,及运算结果

四位全加器的代码如下

module add4(ina,inb,cin,sum,out);//有分号 input [3:0]ina,inb;

input cin;

output out; output [3:0]; assign {out,sum}={ina+inb+cin}; endmodule//无分号

在这里,我们不需要完全来理解这个代码,只是想借助代码来介绍varilog设计的相关知识。

1.varilog程序是由module开始,endmodule结束的。

2.每个模块开始都要进行端口的定义,定义输入输出端口。如上面程序的2,3,4,5行就是对端口的定义。而第一行是端口列表。

3.varilog程序可以一行写几个语句,也可以分多行写。

4.除了endoule,end,endcase等语句结束无分号以外,其余都要有。

理解要点:

1。理解程序中哪些是顺序执行,哪些是并行执行

Q:在模块中,所有过程块,连续赋值语句(assign)实例引用等是并行执行的。

2.在统一模块中三者出现的先后顺序没有关系,他们表示的仅仅是一种通过变量名连接的关系。

3.只有连续赋值语句assign和实例引用语句可以独立于过程块存在于模块功能的定义部分。

4.在一个模块中可以存在多个模块,这些模块之间是并行运行的。

5。当一个大模块包含一个或多个子模块,varilog采用模块调用或模块实例化来实现这些子模块于高层模块的连接。

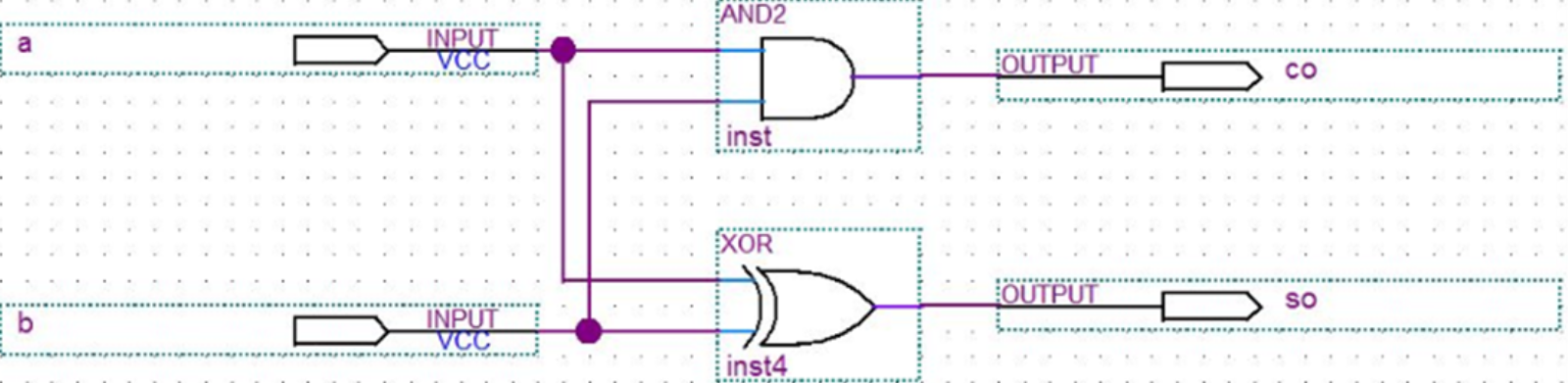

如调用两个半加器实现全加器

(a)

半加器原理图(b)

(b)

标识符:可以由字母,数字以及$,"_"(只有这两个特殊符号可以,其他的含有”/"也不对)的组合,开头不能是数字,只能是下划线或者字母,标识符区分大小写。

关键字:如module,endcase,parameter,intial,不区分大小写。

在下一篇中将详细介绍varilog语法。

浙公网安备 33010602011771号

浙公网安备 33010602011771号