Nordic nRF54L 系列的关键引脚规划指南

接下来我们将探讨 nRF54L 系列(nRF54L15、nRF54L10、nRF54L05)引脚规划的关键方面。我们将从探讨与引脚规划相关的电源域及其相关的 GPIO 端口开始。我们将突出每个域提供的引脚数量及其关键特性,例如速度限制和支持特性,如引脚感应、GPIOTE 以及从睡眠状态唤醒系统的能力

nRF54L 系列的电源域

引脚规划涉及需要引脚的外设,如 ADC、PWM、SPI、UART 等。为了有效地将外设映射到正确的引脚,我们需要知道它属于哪个域

定义:电源域是芯片中可以独立开启或关闭电源以优化能耗的部分,nRF54L 系列架构分为四个电源域:

- MCU domain (MCU):

该域包含 Arm Cortex-M33 处理器、作为快速轻量级外围处理器(FLPR)的 RISC-V 协处理器以及包括 ETM 跟踪的调试系统。它还包含高速外围设备(例如 UARTE 和 HS-SPI)。MCU 域运行在 128 MHz 时钟上。该域中具有数字 ID 的外设将以数字 0 开头(例如 UARTE00),该域有一个专用 GPIO 端口,即端口 2(P2)

- Radio domain (RADIO):

该域包含短程射频及其支持射频协议栈的外设。它运行在 32 MHz,由于该域内所有外设都旨在支持射频,因此该域没有专用 GPIO 端口。该域与引脚规划无关(除非使用方向寻找或多天线信道探测——见规则 4.f)。

- Peripheral domain (PERI):

该域包含芯片上大多数外设,并运行在 16 MHz。该域中具有数字 ID 的外设将以数字 2 开头(例如 UARTE20)。该域有一个专用 GPIO 端口,即端口 1(P1)

- Low-power domain (LP):

此域专用于设计用于超低功耗模式的周边设备。即使周边域关闭,它也可以用来唤醒系统的其余部分。它运行在 16 MHz 频率,此域中具有数字 ID 的周边设备将以数字 3 开头(例如,UARTE30)。该域有一个专用的 GPIO 端口,即端口 0(P0)

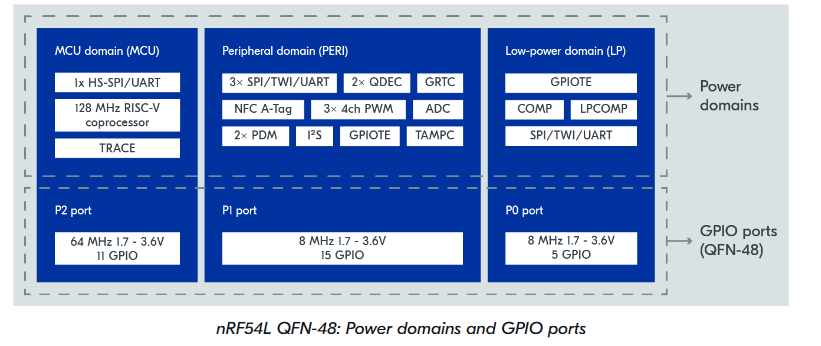

下面的框图显示了可用的电源域及其组件和周边设备---------------------------------------------------------

实现具有多个电源域的 SoC 的一个重要原因是确保低功耗运行。通过允许各个域独立供电,当芯片的某些部分不需要主动工作时可以将其关闭,这有助于实现更低的功耗。这能够延长电池寿命并减小电池尺寸。低功耗域尤其包含专为超低功耗模式设计的接口,即使接口域被关闭时也能唤醒系统的其他部分

可用端口和功能

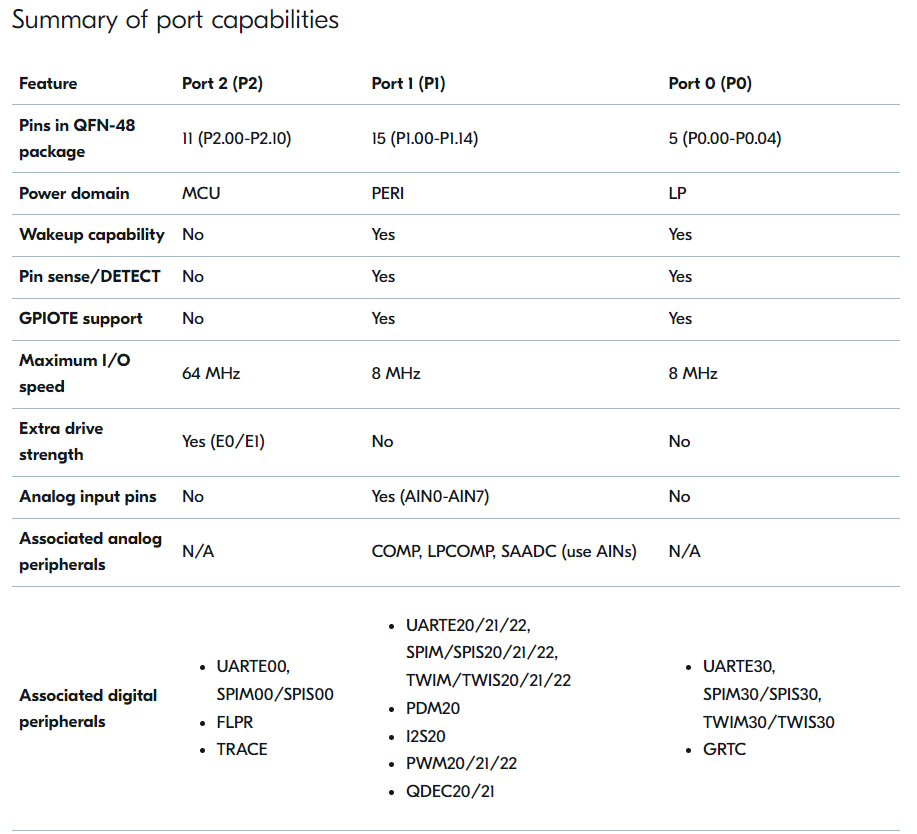

三个电源域,MCU、PERI 和 LP,各自拥有自己的 GPIO 端口(分别为 P2、P1 和 P0),而 RADIO 域则没有。P1 和 P0 有许多相似之处,而 P2 则差异显著

GPIO 端口 2(P2):此端口与微控制器域相关联

该端口上的引脚数量取决于所使用的封装。对于 QFN-48 封装,有 11 个引脚:P2.00 至 P2.10。

该端口上的引脚是芯片上速度最快的引脚,用于高速信号,如走线或快速串行通信。

P2 上信号的最大速度为 64 MHz。

支持标准、高驱动和超高驱动。

P2 引脚无法唤醒系统从睡眠状态,并且不包含 GPIO SENSE 或 DETECT 机制或 GPIOTE 功能。这意味着当 P2 引脚配置为通用 GPIO 时,它们不可用中断支持。

位于 MCU 域的外设,如 SPIM00 和 UARTE00,使用 P2 上的专用引脚。

用于 TRACE 和 FLPR(用于模拟外设如 QSPI)的专用引脚也在 P2 上。

P2 上的选定引脚也可以被外围域中某些串行接口(SPIM、SPIS、UARTE)使用,尽管这种配置被认为不太节能

GPIO 端口 1(P1):此端口与外围设备域相关联

这个端口的引脚数量取决于所使用的封装。对于 QFN-48 封装,有 15 个引脚:P1.00-P1.14。

P1 上信号的最大速度为 8 MHz。

仅支持标准和高速驱动。

P1 引脚可以从系统开启或系统关闭的睡眠状态唤醒系统。

包含模拟输入引脚(AIN0-AIN7),这些引脚在低功耗域中由 ADC(SAADC)和 COMP/LPCOMP 共享。

PWM 外设仅在 P1 引脚上可用。

P1 支持引脚感应机制,并与 GPIOTE20 相关联。

当使用篡改检测时,TAMPC 的专用引脚。

当使用方向寻找或信道探测多天线时,专用 RADIO 引脚位于 P1。

P1 上的专用 NFC 天线引脚在复位后配置为 NFC 天线引脚。这些可以更改为通用 GPIO

GPIO 端口 0(P0):此端口与 LP 域相关联

这个端口的引脚数量取决于所使用的封装。对于 QFN-48 封装,有 5 个引脚:P0.00-P0.04

P0 上信号的最大速度为 8 MHz。

仅支持标准和高速驱动。

P0 引脚可以从系统开启(System ON)或系统关闭(System OFF)的睡眠状态唤醒。

P0 支持引脚感应机制,并与 GPIOTE30 相关联。

用于 GRTC 的专用引脚,当使用其时钟和 PWM 输出时。

下图描述了 QFN-48 封装中每个电源域的 peripherals 以及它们对应的 GPIO 端口

浙公网安备 33010602011771号

浙公网安备 33010602011771号