E203存储器

一、存储器概述

1、关于缓存cache

蜂鸟E203的处理器中没有配备缓存,处理器外则分别配备了ITCM和DTCM用于存储指令和数据

虽然在常见的PC的CPU大都配备了缓存,甚至有一二三级不同缓存用来提高内核执行效率,但实际上大部分的低功耗中低性能处理器并没有配备缓存,主要原因在于以下几点:

-

缓存无法保证实时性

缓存利用软件程序的时间局部性和空间局部性,将存储器数据动态映射到容量很小的缓存中,这样减小了访问存储器的平均延迟。但是正因如此,访问缓存存在着巨大的不确定性,最直观的,一旦缓存不命中就会导致取指或访存时间增加,这就导致实时性不好。针对这一点,大多低功耗中低性能处理器都使用延迟确定的ITCM和DTCM -

嵌入式设备软件规模较小

在嵌入式领域的软件代码一般很小,所需的数据段也很小,所以使用片上SRAM、片内FLASH或者ITCM/DTCM便可以满足其需求,因此缓存的优点就被大大影响,不能说一点用都没有,只能说映射了个寂寞 -

缓存面积功耗大

蜂鸟E203采用的是哈佛架构,主要特点如下:

- 程序和数据单独存储

- 每个存储器独立编址、独立访问

- 使用数据总线和指令总线独立连接两个存储器到内核

- 取址和执行并行处理

ITCM和DTCM:

- 能够保证实时性,映射到不同的地址区间,不存在不命中的情况

- 规模小,但可满足软件需求

- 设计简单,面积小,功耗小

二、RISC-V的存储器访问

1、RISC-V架构对于存储器也进行了一定简化

- 仅支持小端格式

- 没有地址自增自减,自增自减有利于访问连续存储器地址区间,但增加了处理器的硬件实现难度

- 没有一次读/写多个数据的指令

- 专用存储器读写指令:使用Load进行存储器读;使用Store进行存储器写;RISC-V还定义了7条存储器读指令和存储器写指令用来进行字节、半字、单字的读写操作

- 松散存储器模型:RISC-V使用松散存储器模型,对不同地址访存的顺序不做要求,使用Fence和Fence.I指令来强行界定访存的顺序

- 扩展指令,用于支持多线程状态下访问存储器的原子操作或同步操作;包括Atomic Memory Operation(AMO)指令、Load-Reserved指令、Store-Conditional指令

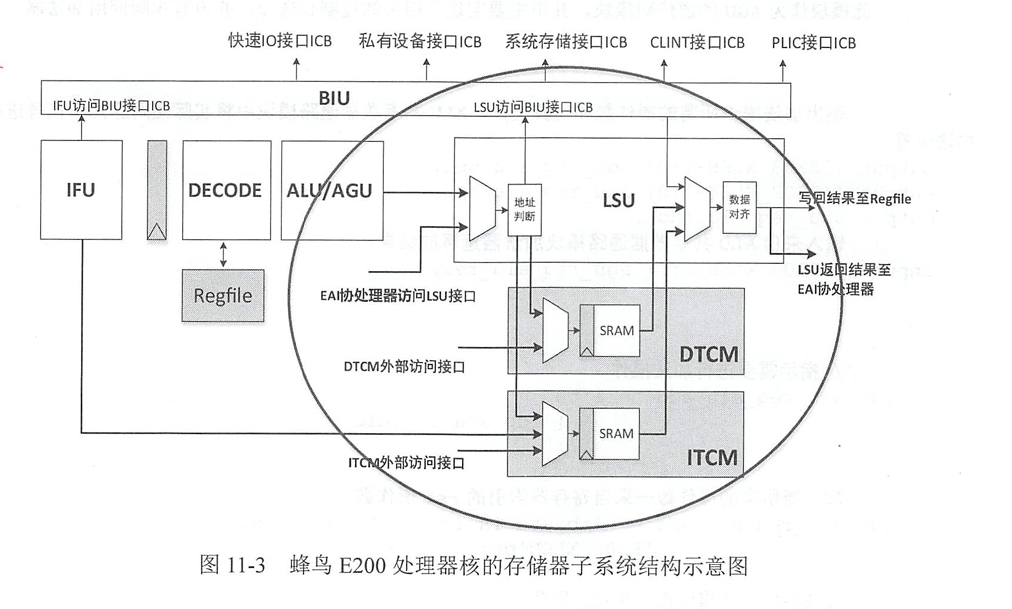

三、蜂鸟E203处理器核的存储器子系统硬件实现

1、总体结构

存储器子系统主要包括4个组件:

- 地址生成单元AGU

- LSU:存储器访问的控制模块

- 指令紧耦合存储器ITCM

- 数据紧耦合存储器DTCM

以上DTCM和ITCM并联到LSU的地址判断和数据对齐控制器之间,AGU则旁挂在LSU上,LSU通过BIU与ICB总线相连

2、AGU

功能:产生读/写指令以及A扩展指令集的访存地址

因为AGU需要将第一个寄存器索引的源操作数和符号位扩展的立即数相加来得到读写指令最终的方寸地址,所以需要用到加法器

因此蜂鸟E203中将AGU和ALU放在一起,复用ALU的加法器来节省面积

其代码保存在/rtl/e203/core/e203_exu_alu.v、e203_exu_dpath.v、e203_exu_lsuagu.v文件中,很明显和ALU放在了一起

lsuagu为AGU的源代码模块,实现相关控制和选择;对于地址不对齐的读写指令,产生异常标志,通过ALU将异常标志传给交付模块,交给软件处理。无异常通过AGU的ICB接口发送给LSU模块

点击查看代码

//获取当前读写指令访问内存时的操作尺寸

//将ALU的加法器计算结果作为读写指令访存的地址

//判断当前访问的地址是否和操作尺寸对齐

//为交付接口产生不对齐指示信号

//为交付接口产生load指令指示信号,用于产生读存储器地址不对齐异常

//为交付接口产生store,AMO指令指示信号,用于产生写存储器或AMO地址不对齐异常

LSU有2组输入ICB总线接口,分别接入AGU和NICE协处理器的接口;3组输出ICB接口,分别分发给BIU、DTCM和ITCM;LSU还配备了一个写回接口。2组输入总线通过一个ICB汇合模块合成一组ICB总线,采用优先级仲裁的逻辑,NICE总线具有更高的优先级,经过汇合之后的ICB总线通过命令通道的地址进行判断,通过其访问的地址区间产生分发信息,随后接入的ICB分发模块会将其分发给不同存储器组件的ICB接口

如果NICE需要访问存储器,就需要在LSU这里进行配置

特别地,LSU使用的ICB汇合和ICB分发模块的FIFO深度均为1,也就是LSU默认只支持1个滞外传输

最终的返回数据需要经过尺寸对齐后经过LSU写回接口写回。对于可能出现的存储器访问错误,LSU预留了一条反馈通道信号线用于返回标志信号,异常标志会通过LSU的写回接口传送给内核的交付模块,交付模块会据此产生异常

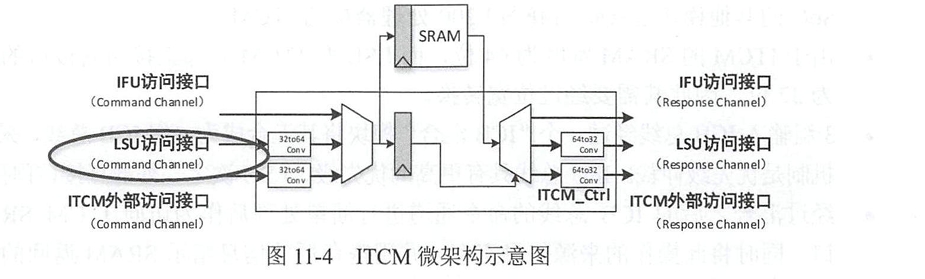

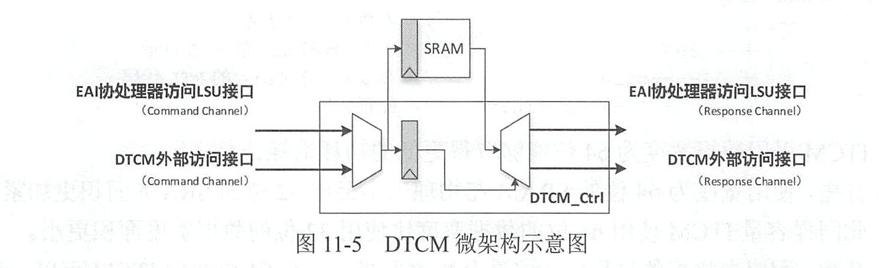

4、ITCM和DTCM

蜂鸟E200系列处理器使用专用总线分别访问ITCM和DTCM,ITCM位宽为64位,DTCM位宽为32位

ITCM有一组输入ICB接口来自LSU,即ITCM所在的地址空间同样可通过LSU被读和写指令访问,用于存储数据

ITCM主体是一块数据宽度为64位的单口SRAM,大小和基地址可在config.v中配置

ITCM也有一组输入ICB总线接口来自LSU的访问,所以ITCM所在的地址区间同样能够通过LSU被读写指令访问到用于存储数据;另外有一组64位宽ICB总线接入到IFU,有一组32位宽的外部直接访问接口用于SoC中的外设能够直接访问ITCM。三组输入的ICB总线会经过一个ICB汇合模块汇成一组ICB总线,模块依旧采用优先级仲裁,IFU总线优先级>LSU优先级>外部直接访问接口。操作的来源信息会被寄存,SRAM返回的数据会根据寄存结果分发回三个总线之一

DTCM主体是一块数据宽度为32位的单口SRAM,大小和基地址可在config.v中配置

DTCM则拥有2组输入ICB总线接口,分别来自LSU和外部直接访问接口,具体实现和ITCM大同小异

ITCM的实现代码为e203_itcm_ctrl.v,DTCM的实现代码为e203_dtcm_ctrl.v

可根据片上的资源选择使用ITCM和DTCM

点击查看代码

`ifdef E203_HAS_DTCM //{

module e203_dtcm_ram(

input sd,

input ds,

input ls,

input cs,

input we,

input [`E203_DTCM_RAM_AW-1:0] addr,

input [`E203_DTCM_RAM_MW-1:0] wem,

input [`E203_DTCM_RAM_DW-1:0] din,

output [`E203_DTCM_RAM_DW-1:0] dout,

input rst_n,

input clk

);

sirv_gnrl_ram #(

.FORCE_X2ZERO(1),//Always force X to zeros

.DP(`E203_DTCM_RAM_DP),

.DW(`E203_DTCM_RAM_DW),

.MW(`E203_DTCM_RAM_MW),

.AW(`E203_DTCM_RAM_AW)

) u_e203_dtcm_gnrl_ram(

.sd (sd ),

.ds (ds ),

.ls (ls ),

.rst_n (rst_n ),

.clk (clk ),

.cs (cs ),

.we (we ),

.addr(addr),

.din (din ),

.wem (wem ),

.dout(dout)

);

endmodule

`endif//}

`ifdef E203_HAS_ITCM //{

module e203_itcm_ram(

input sd,

input ds,

input ls,

input cs,

input we,

input [`E203_ITCM_RAM_AW-1:0] addr,

input [`E203_ITCM_RAM_MW-1:0] wem,

input [`E203_ITCM_RAM_DW-1:0] din,

output [`E203_ITCM_RAM_DW-1:0] dout,

input rst_n,

input clk

);

sirv_gnrl_ram #(

`ifndef E203_HAS_ECC//{

.FORCE_X2ZERO(0),

`endif//}

.DP(`E203_ITCM_RAM_DP),

.DW(`E203_ITCM_RAM_DW),

.MW(`E203_ITCM_RAM_MW),

.AW(`E203_ITCM_RAM_AW)

) u_e203_itcm_gnrl_ram(

.sd (sd ),

.ds (ds ),

.ls (ls ),

.rst_n (rst_n ),

.clk (clk ),

.cs (cs ),

.we (we ),

.addr(addr),

.din (din ),

.wem (wem ),

.dout(dout)

);

endmodule

`endif//}

5、A扩展指令集的硬件实现

https://blog.csdn.net/New_Horizon_/article/details/90519010

6、fence和fence.i指令的硬件实现

fence和fence.i指令:在流水线的派遣点,派遣fence和fence.i指令前等待所有已经滞外的指令执行完毕,即等待OITF为空,OITF记录了所有的滞外指令,为空说明滞外指令已执行完毕

fence.i指令:需要保证fence.i之后执行的取指令操作一定能观测到该指令之前执行的指令访存结果。

相当于一种特殊的流水线冲刷指令,使用fence.i指令接下来的一条指令的PC作为冲刷请求的PC,意味着fence.i之后的指令会被取出重新执行一遍

(没明白怎么冲刷的)

7、BIU

除了ITCM和DTCM外,蜂鸟E203还能通过总线接口单元(BIU,bus interface unit)访问外部的存储器

8、ECC

浙公网安备 33010602011771号

浙公网安备 33010602011771号