课程设计——数字时钟

一、技术指标要求

1.具有时、分、秒计时及显示;

计时范围:00时00分00秒 ---- 23时59分59秒

2.具有手动校时、校分功能;

3.能整点报时;从59分51秒开始,逢单响一下( 持续1秒 ),前4响频率为500Hz,最后1响频率为1000Hz。也可逢双响。

4.脉冲信号发生(1Hz、512Hz、1024Hz)。

二、总体方案设计

1.模块功能划分

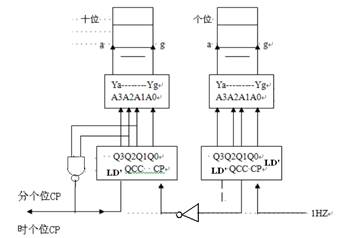

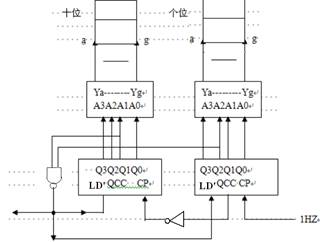

如图1所示,本方案分六个模块,分别是“秒”模块、“分”模块、“时”模块、“校分模块”、“校时模块”和“报时模块”。其中,“秒”、“分”、“时”模块由各自的计数器、译码器、显示器组成;“校分模块”、“校时模块”各由校分、校时按钮和逻辑单元组成;“报时模块”由逻辑单元与蜂鸣器组成。

其中,“时”、“分”、“秒”三个模块具有时、分、秒计时及显示功能;校时模块与校分模块中,每按下一次校时、分按钮,时或分计数一次,秒维持不变。

2.面包板上集成电路布局

如图,实验箱上的面包板左半区域里是时钟模块,右半区域是报时模块。时钟模块从上至下依次是数码管、译码器、计数器。根据元件连接的就近原则,计数器的逻辑模块布置在各位之间。报时模块中,由于逻辑模块直接与计数器连接,而选择器再与逻辑模块、触发器连接,因此逻辑模块布置在该区域的右侧,更接近时钟模块的位置。

3.十进制、六进制显示设计

十进制、六进制显示部分分别由数码管、译码器、计数器组成。计数器将BCD码输出给译码器,译码器将信号输出给数码管。六进制计数器是通过与非门控制十进制计数器的LD管脚实现的。

十进制计数器:

六进制计数器:

4.六十进制、二十四进制计数器设计

如图所示,六十进制、二十四进制计数器分别由两个计数器和多个与非门组成。其中,个位与十位计数器采用并行进位的方法级联,且同时置“0”。

六十进制计数器:

二十四进制计数器:

5.校时校分电路设计

校时、校分电路各由CP脉冲和多个与非门组成。当校时按钮按下或一分钟、一小时走完时分别向分、时计数器输出一个周期的脉冲时钟信号。

6.报时模块

报时模块由数据选择器、D触发器和逻辑电路组成。在59分51、53、55、57秒时给蜂鸣器输出500Hz信号,在59分59秒时给蜂鸣器输出1000Hz信号。

三、各部分单元电路设计

1.“秒”模块

“秒”模块设计的本质是一个带显示的六十进制计数器,由一个数码管、一个计数器、一个译码器和一个集成与非门组成。

A.单个个位与单个十位

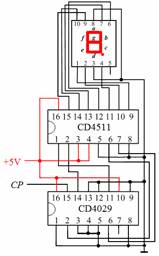

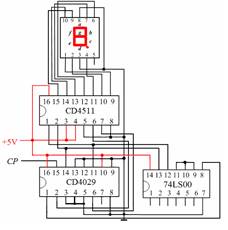

CD4029芯片是同步置数的4位二进制或BCD码十进制加减计数器,其管脚如图所示。

引脚功能:

1: 当LD为高电平时,计数器同步将Qn置为Dn;

2:输出第三位;

3:置数第三位;

4:置数第零位;

5:进位输入;

6:输出第零位;

7:进位输出;

8:电源负极;

9:当B/D’为低电平时,以十进制计数,反之为二进制计数;

10:当U/D’为高电平时,为加计数,反之为减计数。

11:输出第一位;

12:置数第一位;

13:置数第二位;

14:输出第二位;

15:脉冲信号输入;

16:电源正极;

要实现要求的功能,则需将计数器芯片的VDD与VSS端分别与电源正负极相连,给芯片供电;将U/D’与接高电平,B/D’接低电平,使其工作在十进制加计数工作状态;将芯片置数输入端接低电平,使每次置数为“0”。

芯片的CP、LD、CI’、C0’在秒个位、十位级联时再进行连接。

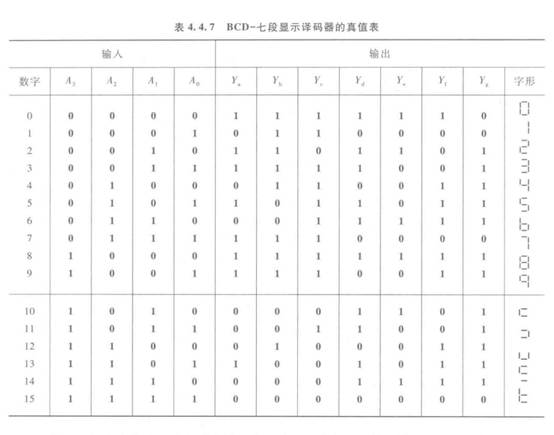

本方案采用CD4511作为译码器,CD4511是一个用于驱动共阴数码管的 BCD 码—七段译码器,它能将输入的四位BCD码A3A2A1A0译为七段数码管特殊的7位编码YaYbYcYdYeYfYg。

芯片引脚图如下:

其中,7、1、2、6脚分别是译码器BCD码由低位到高位的输入端;

9-15脚为译码器的8位输出端;

3、4脚分别是测试输入端与消隐端,接高电平时正常工作。

16脚和8脚分别是电源正负极。

BCD—七段显示译码器真值表如下表:

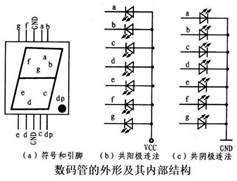

接下来对数码管的工作原理和使用方法进行详细介绍。

LED数码管按段数可分为七段数码管和八段数码管,八段数码管比七段数码管多一个发光二极管单元(多一个小数点显示);按能显示多少个“8”可分为1位、2位、3位、4位、5位、6位、7位等数码管。本方案采用多个1位数码管实现多位数字的显示的解决方案。

此外,数码管按单元连接方式可划分为共阳数码管和共阴数码管。如图,共阳数码管将所有发光二极管的阳极接到一起形成公共阳极(COM)的数码管,共阳数码管在使用时应将公共极COM接到+5V,当某一字段发光二极管的阴极为低电平时,相应字段就点亮,当某一字段的阴极为高电平时,相应字段就不亮。而共阴数码管将所有发光二极管的阴极接到一起形成公共阴极(COM)的数码管,共阴数码管在使用时应将公共极COM接到地线GND上,当某一字段发光二极管的阳极为高电平时,相应字段就点亮,当某一字段的阳极为低电平时,相应字段就不亮。

本方案采用的是BS207共阴数码管。由于CD4511正是用于驱动共阴数码管的 BCD 码—七段译码器,因此可以将CD4511译码器输出直接送给BS207共阴数码管。

将译码器电源正负分别接电源正负、LT’与BI’接低电平,使之能正常工作,将共阴数码管的输入与CD4511译码器的对应的输出相连,使译码器能将输出信号传输给数码管,并将数码管共阴极接电源负极,使数码管能被点亮,这样就完成了数码管与译码器之间的连接,该部分接线如下图所示。

再将计数器的输出端Q3Q2Q1Q0依次连接译码器的A3A2A1A0,使计数器能将输出信号传输给译码器进行译码,这样就完成了译码器与计数器之间的连接。

B.个位与十位之间的连接

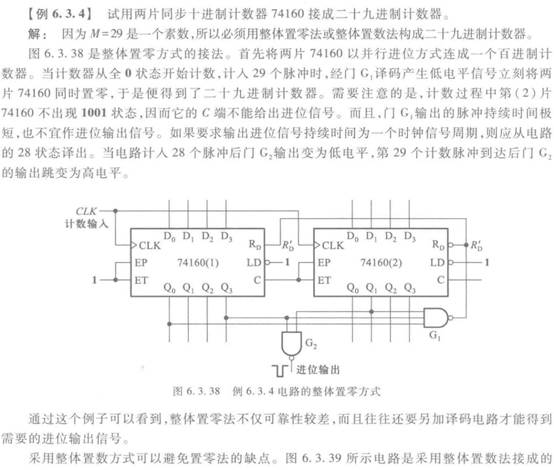

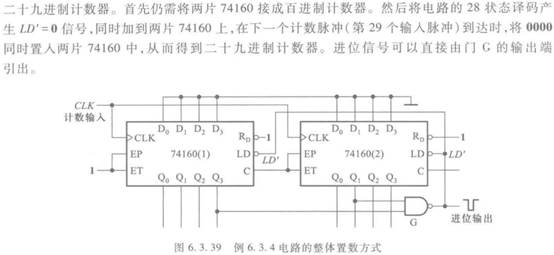

秒的个位与十位组成一个六十进制计数器,要实现本功能,首先应使计数器处于正确的逻辑工作状态。参照《数字电子技术基础》第300页例6.3.4特殊进制的计数器的设计(见附录),采用两个同步十进制计数器并行进位的方式来实现。而本方案选择采用CD4029芯片连接成六十进制计数器,与书中的74160芯片连接成二十九进制计数器略有不同。

由于个位与十位之间的进位关系,须将个位计数器的进位输出端CO’接至十位计数器进位输入端CI’;又因个位计数器是秒的最低位,所以将个位计数器的进位输入端CI’接低电平。由于CD4029是十进制计数器,而此处需要的是六十进制计数器,因此需要逻辑门电路作为逻辑模块,使在计数器满足一定输出时通过控制LD为高电平,将Q3Q2Q1Q0置为D3D2D1D0(0000)。值得注意的是,个位与十位应同时置数“0”,须将个位与十位计数器的LD相连;同时并行进位要求多位计数器同时接入相同CP脉冲,须将个位与十位计数器的CP相连。

本方案采用74LS00四2输入与非门组成逻辑门电路,74LS00芯片的逻辑功能与管脚如图所示。

由于CD4029是同步计数器,要实现六十进制计数器功能,须在“秒”十位输出“6”(即0110)时控制LD为有效,将其置数为“0”,LD逻辑表达式为:

LD=Q2(十位)·Q1(十位)

但由于74LS00为与非门,因此需要两次与非实现上述表达式,即:

1Y=(Q2(十位)·Q1(十位))’

2Y=(1Y·1)’= Q2(十位)·Q1(十位)

完成74LS00部分的接线,可将秒个位或十位接入1Hz时钟信号,打开电源进行测试和验证。

2.“分”模块

“分”模块设计的本质与“秒”模块类似,也是一个带显示的六十进制计数器,由一个数码管、一个计数器、一个译码器和一个集成与非门组成。其连接与“秒”模块基本相同,仅CP时钟不同。

从逻辑上讲,秒每置零一次,分计数一次。因此“分”模块的两个计数器的CP应同时接入“秒”模块的LD,使“分”CP信号的周期为“秒”CP信号周期的六十分之一。

完成此部分连接,可打开电源进行测试和验证。

3.“时”模块

“时”模块设计的本质是一个带显示的二十四进制计数器,由一个数码管、一个计数器、一个译码器和一个集成与非门组成。其连接与“分”“秒”模块类似,但CP时钟与进位逻辑不同。

由于CD4029是同步计数器,要实现二十四进制计数器功能,须在“时”十位输出“2”(即0010)且“时”个位输出“4”(即0100)时控制LD为有效,将其置数“0”,LD逻辑表达式为:

LD= Q1(十位)·Q2(个位)

但由于74LS00为与非门,因此需要两次与非实现上述表达式,即:

1Y=( Q1(十位)·Q2(个位))’

2Y=(1Y·1)’= Q1(十位)·Q2(个位)

从逻辑上讲,分每置零一次,时计数一次。因此“时”模块的两个计数器的CP应同时接入“分”模块的LD,使“时”CP信号的周期为“分”CP信号周期的六十分之一。

完成此部分连接,可打开电源进行测试和验证。

4.校分模块

一个功能完整的电子钟需要校时与校分功能。在之前的电路中,秒每置零一次,分计数一次,而校分电路要求在每次按下CP脉冲时,分也能进行一次计数,本方案通过一个74LS00与非门来实现该功能。校分逻辑表达式为:

CP(分)=LD(秒)+P2

但由于74LS00为与非门,因此需要两次与非实现上述表达式,即:

Y1=(LD(秒)·1)’=LD(秒)’

Y2=(Y1·P2’) =LD(秒)+P2

该部分74LS00电路连接如下所示:

值得注意的是,在接完此部分电路后,须移除原来“秒”模块的LD与“分”模块的CP之间的连接线,否则会导致校分功能不正常。

5.校时模块

校时模块与校分模块类似。在之前的电路中,分每置零一次,时计数一次,而校时电路要求在每次按下CP脉冲时,时也能进行一次计数,本方案通过一个74LS00集成与非门来实现该功能。校分逻辑表达式为:

CP(时)=LD(分)+P1

但由于74LS00为与非门,因此需要两次与非实现上述表达式,即:

Y1=(LD(分)·1)’=LD(分)’

Y2=(Y1·P1’) =LD(分)+P1

该部分74LS00电路图如下所示:

与校分模块相同,在接完此部分电路后,须移除原来“分”模块的LD与“时”模块的CP之间的连接线,否则会导致校时功能不正常。

6.报时模块

报时模块的功能是,每个小时的59分51秒到57秒逢单数秒响500Hz,59秒响1000Hz。为实现此功能,需要用到一个数据选择器,59分51、53、55、57秒选通500Hz频率,59分59秒选通1000Hz频率,输出给蜂鸣器。

实验箱上只有1000Hz的函数信号发生器,因此需要通过触发器来分频,这里本方案采用74LS74双D上升沿触发器芯片。首先将D触发器的Q’与D相连,组成一个T’触发器(见《数字电子技术基础》第226页),其表达式为:

Q*=Q’

再将1000Hz接入D触发器时钟信号输入端CP。由于74LS74是上升沿D触发器,因此D触发器输出Q会在时钟信号由0变为1时进行翻转,即每两个周期翻转一次。因此D触发器输出500Hz的方波信号。

注:参照《数字电子技术基础》第278页,此处也可以用计数器来实现。

如上图所示,本方案采用74LS153作为数据选择器;采用74LS20作为四2输入与非门;采用74LS04作为反相器;采用74LS74作为D触发器。各芯片管脚及功能如下图所示。

其中74LS153是双4选1数据选择器,其输出表达式为:

Y=(A1’A0’)D0+(A1’A0)D1+(A1A0’)D2+(A1A0)D3

我们将500Hz输入D0,1000Hz输入D1,因此在59分51、53、55、57秒时,A1A0=0(即A1=0且A0=0),选通D0;在59分59秒时A1’A0=0(即A1=1且A0=0),选通D1。

59分时,分十位计数器输出为:0101,分个位计数器输出为:1001;

50秒以后的奇数秒时,秒十位计数器输出为:0101,秒个位计数器输出为:0001。

可参照下表:

| 分 | 秒 | 奇偶 | 分十位 | 分个位 | 秒十位 | 秒个位 | A0 | A1 | 选通 |

|---|---|---|---|---|---|---|---|---|---|

| 59分 | 50秒之前 | 奇数秒 | 0101 | 1001 | Q2Q0不为1 | XXX1 | 1 | X | |

| 偶数秒 | 0101 | 1001 | Q2Q0不为1 | XXX0 | 1 | X | |||

| 50秒之后,58秒之前 | 奇数秒 | 0101 | 1001 | 0101 | XXX1 | 0 | 0 | 选通D0 | |

| 偶数秒 | 0101 | 1001 | 0101 | XXX0 | 1 | 1 | |||

| 59秒 | 奇数秒 | 0101 | 1001 | 0101 | 1001 | 0 | 1 | 选通D1 |

因此A1的输入表达式应为:

A1=Q2(分十位)Q0(分十位)Q3(分个位)Q0(分个位)Q2(秒十位)Q0(秒十位)Q0(秒个位)

由于仅有双四输入的与非门74LS20和74LS04六反相器,因此须将表达式改成:

A1=((Q2(分十位)Q0(分十位)Q3(分个位)Q0(分个位))’)’·((Q2(秒十位)Q0(秒十位)Q0(秒个位)·1)’)’

该式可以拆分为:

Y1=(Q2(分十位)Q0(分十位)Q3(分个位)Q0(分个位))’ 74LS20实现

Y2=(Q2(秒十位)Q0(秒十位)Q0(秒个位)·1)’ 74LS20实现

Y3=Y1’= Q2(分十位)Q0(分十位)Q3(分个位)Q0(分个位) 74LS04实现

Y4=Y2’= Q2(秒十位)Q0(秒十位)Q0(秒个位) 74LS04实现

Y5=(Y3·Y4)’=(Q2(分十位)Q0(分十位)Q3(分个位)Q0(分个位)Q2(秒十位)Q0(秒十位)Q0(秒个位))’ 74LS00实现

Y6=Y5’=Q2(分十位)Q0(分十位)Q3(分个位)Q0(分个位)Q2(秒十位)Q0(秒十位)Q0(秒个位) 74LS04实现

59秒时,秒个位计数器的输出为:1001,因此A0的输入表达式为:

A0= Q3(秒个位)Q0(秒个位)

由于仅有双四输入的与非门74LS20和74LS04六反相器,因此需通过一次与非再一次非实现:

Y1=(Q3(秒个位)Q0(秒个位))’ 74LS00实现

Y2=Y1’=Q3(秒个位)Q0(秒个位) 74LS04实现

将此部分电路接好,即可测试整个电路。

四、安装、布线、调试注意事项

1.电子技术实验箱的接插安装与布线

目前,在实验室中常用的各类电子技术实验箱上通常有数块多孔插座板(或称面包板)。利用这些多孔插座板可以直接接插安装和连接实验电路而无需焊接。然而,正确和整齐的布线在这里显得极为重要。这不仅是为了检查、测量的方便,更重要的是可以确保线路稳定可靠地工作,因而是实验顺利进行的基础。实践证明,草率的和杂乱无章的接线往往会使线路中出现难以排除的故障,以致最后不得不重新接插和安装全部实验电路,浪费很多时间。为此,在多孔插座板上接插安装时应注意做到以下几点:

(1)首先要弄清楚多孔插座板和实验箱的结构,然后根据实验箱的结构特点来安排元器件位置和电路的布线。一般应以集成电路为中心,并根据输入、输出分离的原则,所有器件按照就近布局、缺口朝左、跨槽放置的原则布局好,匀称分布。最好先画出实物布置图和布线图,以免发生差错。

(2)接插元器件和导线时要非常细心。接插前,必须先用钳子或镊子把待插元器件和导线的插脚弄平直,弯管脚拨直后用,断管脚的不用。接插时,应小心地用力插入,以保证插脚与插座间接触良好。实验结束时,应用镊子一一轻轻拔下元器件和导线,切不可用力太猛。注意接插用的元器件插脚和连接导线均不能太粗或太细,一般以线径0.5mm左右为宜,导线的剥线头长度约5mm。

(3)布线的顺序一般是先布电源线与地线,然后按布线图布线。在布电源线与地线时应将所有IC的电源端串接在一起,接数字箱上的Vcc(+)端; 将所有IC的地端串接在一起,接数字箱上的GND(-)端;确保数字箱上电源和地不短路,(如果指示灯不亮,数字箱上电源和地可能短路),确保所有IC接上电源和地、数字箱上电源不短路,再依次连接好各元器件和接线。在可能条件下应尽量做到接线短、接点少,但同时又要考虑到测量的方便。

(4)在接通电源之前,要仔细检查所有的连接线。特别应注意检查各电源的连线和公共地线是否接得正确.查线时仍以集成电路的引脚为出发点,逐一检查与之相连接的元件和连线,在确认正确无误后方可接通电源。

2.正确的接线规则

仪器和实验板间的接线要用颜色加以区别,以便于检查,如电源线(正极)常用红色,公共地线(负极)常用黑色。接线头要拧紧或夹牢,以防因接触不良或脱落而引起短路。应接高电平的管脚就近接其Vcc端,应接低电平的管脚就近接其GND端。

3.测试前的准备

在线路按要求安装完毕后即将通电测试前,应做好以下准备工作:

(1)先检查各种仪器面板上的旋钮,使之处于所需的待用位置。切勿在调整电压前随意与实验电路板接通。

(2)对照实验电路图,对实验电路板中的元件和接线进行仔细的寻迹检查,检查各引线

有无接错,并注意防止碰线短路等问题。经过认真仔细检查,确认安装无差错后,方可按前述的接线原则,将实验电路板与电源和测试仪器接通。

4.调试的方法与步骤

调试前,应先用数字电压表检查实验箱电源正负极是否正常输出5v电压;用小灯泡和示波器检查脉冲输出是否能输出所标频率的脉冲。若实验箱部分功能故障则需要用直流电源、函数信号发生器等仪器替代。

调试的时候要注意分模块调试、试验,做完一部分电路立刻进行该部分电路的调试。这样不仅可以缩小故障与错误的范围,也能一定程度上避免相同故障或错误的再次发生。而将电路一口气连完后再调试是不现实的,这样很难找出故障与错误的位置,最终只能将电路重新连接,浪费许多时间。

当故障或错误发生时,应先检查线路的连接是否正确,尤其是电源正负极是否正确连接、芯片是否与面包板接触良好。若仍不能排除错误,则可以利用实验箱上的小灯泡,依次对各芯片进行输入输出逻辑验证。值得注意的是,有的实验箱的部分小灯泡可能断路或短路,应先将小灯泡接电源正测试是否能正常点亮和熄灭。若测试结果不符合设计,则可能是导线接触不良或是芯片故障,此时需要更换导线或者芯片进行故障排除。

五、调试中遇到的问题和故障分析

1.进制错误故障

a) 十进制出现在不应是十进制(应是二进制、四进制、六进制)处

i. 控制进位的74LS00芯片未接电源正负极

ii. LD接地

iii. 未连接控制进位的74LSOO芯片

iv. 74LSOO输出Y与计数器LD间断路

b) X十进制出现在不应是X进制(应是二进制、四进制、六进制)处

i. 74LSOO输入端未正确接至计数器的输出端

2.数码管不亮

数码管共阴极未接地

3.报时故障

a) 报时只响59秒一声

i. 74LS74芯片未正常工作,输出端Q未输出500Hz信号。

ii. 报时逻辑出现故障

b) 报时最后一声不响

i. 报时逻辑出现故障

c) 报时不响

i. 实验箱上的1000Hz信号故障

ii. 蜂鸣器接触不良

4.某个位不计数

i. 该位CP未正确连接

ii. 计数器电源正极负极未正确连接、CI’没有接地

六、设计结果情况

能完成课程设计要求的时分秒计时、时分校时、整点报时功能,且功能稳定。

七、心得体会

此次课程设计进展比较顺利,由于在做课设前进行了充分的预习,因此电路的连接比较快。在连接时,我们小组两位成员分工明确,按部就班地进行测试与验收,及时发现并修正了电路中的错误。在修正错误中,我意识到了懂得电路原理的重要性。懂得原理,则可以在电路出现错误时快速地确定错误所处地位置,即使错误隐藏的比较深,也可以通过逻辑推理找出。其次,一台好的实验箱也是十分重要的,有一些箱子的脉冲、灯泡都坏了,给后期的调试带来了一些困难与阻碍。

在电路的布局上,我们提前设计好芯片的排布,使其疏密合理且不需要用到很多的长导线。在接线的细节上,我们统一用红线接电源正极、黑线接电源负极,这样比较好检查错误。每块面包板上下都可以接电源的正负极,我们充分利用面包板上的正负极,就近接线,避免导线跨越芯片给以后检查故障时替换芯片造成不便。

面包板上电路的连接需要细心与耐心,接线看图不能心急,最好能分模块调试功能,确保已经连的电路能正常工作再连接下一部分,按部就班地进行工作。但即使细心认真地连线,电路依然可能出现故障、错误。这时不应慌乱手脚,应根据“五、调试中遇到的问题和故障分析”中的方法对故障、错误进行排除。

附录

器件清单

74LS00 ×3 四 2输入与非门

74LS04 六反相器

74LS20 双4输入与非门

CD4029 ×6 二/十进制同步计数器

CD4511 ×6 译码器

74LS74 双上升沿D触发器

74LS153 双4选1数据选择器

BS207 ×6 数码管

参考资料

参考文献

[1] 阎石,王红. 数字电子技术基础. 北京:高等教育出版社,2016

[2] 张丽,赵淑范,董鹏中. 电子技术实验与课程设计(第二版). 北京:清华大学出版社,2010

[3] 吕思忠. 数字电路实验与课程设计. 哈尔滨:哈尔滨工程大学出版社,2008

[4] 周文良. 电子电路设计与实践. 北京:国防工业出版社,2011

[5] 彭介华. 电子技术课程设计指导. 北京:清华大学出版社,2008

[6] 高吉祥. 电子技术基础实验与课程设计. 北京:电子工业出版社,2006

浙公网安备 33010602011771号

浙公网安备 33010602011771号