脉冲过滤电路

某公司的笔试题,题目的大概描述如下:

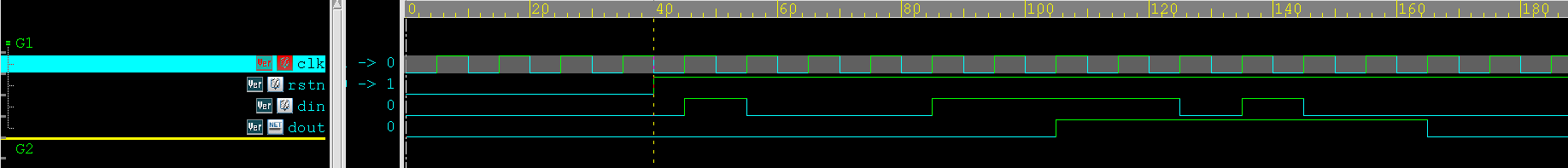

设计一个脉冲检测电路,功能为过滤掉长度小于两个时钟周期的脉冲信号,示例的输入波形如下

分析一下题目,要实现的功能就是这样:当连续两个输入为相同的数时,输出变为这个数,否则输出保持不变。理解了这一点就很容易实现了。相应的代码如下

module pulse_remove(

input clk,

input rstn,

input din,

output detect

);

reg r0,r1;

always@(posedge clk, negedge rstn)begin

if(~rstn)

r0 <= 1'b0;

else

r0 <= din;

end

always@(posedge clk, negedge rstn)begin

if(~rstn)

r1 <= 1'b0;

else if(r0==din)

r1 <= r0;

else

r1 <= r1;

end

assign detect = r1;

endmodule

写个简单的testbench测一下

这个问题可以进一步延申一下,如果题目变成过滤掉长度小于N的脉冲,应该怎么实现呢?方法是类似的,现在需要暂存N-1个输入然后检测这些输入是否相同,不同的地方是检测的方法可能需要有一些变化,检测的目的是检测N-1个寄存器的值是否为全0或者全1,方法我想的是有两种,一种是采用按位或和按位与的方法,另一种是用加法器。先写第一种

module pulse_remove #(

parameter REMOVE_WIDTH = 8

)(

input clk,

input rstn,

input din,

output dout

);

wire is_all_zero;

wire is_all_one;

reg [REMOVE_WIDTH-2:0] din_r;

reg detect;

always@(posedge clk, negedge rstn)begin

if(~rstn)

din_r <= 0;

else

din_r <= {din_r[REMOVE_WIDTH-3:0],din};

end

assign is_all_zero = ~(|din_r);

assign is_all_one = &din_r;

always@(posedge clk, negedge rstn)begin

if(~rstn)

detect <= 1'b0;

else if(din==1'b1&&is_all_one)

detect <= 1'b1;

else if(din==1'b0&&is_all_zero)

detect <= 1'b0;

else

detect <= detect;

end

assign dout = detect;

endmodule

第二种采用加法器的方法是,将N-1个寄存器的值加1,如果结果为0则代表原先寄存器的值全为1,如果结果为1则代表原先寄存器的值全为0,其他的检测步骤和上面的一样,不再多写。

浙公网安备 33010602011771号

浙公网安备 33010602011771号