STA -- Setup time & Hold time 详细解读

Setup time & Hold time

一般来说,setup可以通过时钟频率来调整,而hold time是不行的,是一定要满足的。

-

对于某个DFF来说,建立时间和保持时间可以认为是此器件固有的属性。

-

在理想情况下,只要在时钟沿来临时,有效数据也来临(时钟沿之前或同时),则能够正确采集到数据;而在时钟沿之后(或同时),即使数据发生变化,也不会影响DFF的输出了。然而在实际中,上升沿打开开关需要时间,逻辑门的状态改变(电容充放电等)都需要时间,因此数据的采集是需要一定时间的,在这个时间内数据不能发生变化。上升沿时候开关关闭也需要时间,如果在这个时间段内数据有变化的话,那么新数据就有可能被传递到下一级,进而发生错误,所以数据必须保持一定时间不变。

-

在clk上升沿来之前,数据必须提前一个最小时间量“预先准备好”,这个最小时间量就是建立时间;

在clk上升沿来之后,数据必须保持一个最小时间量“不能变化”,这个最小时间量就是保持时间。

Setup time 检查

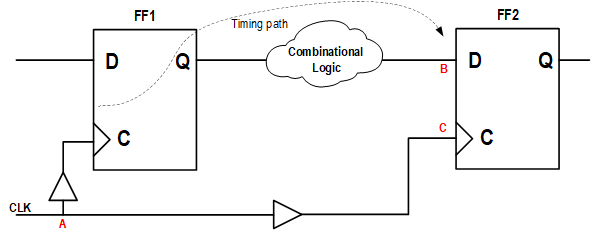

对于上面的两级DFF,setup time检查就是要确保DFF1的Clk到DFF2的D端满足时序要求。

简单来说,就是检查从DFF1的Clk到DFF2的D端这条path上,数据是否传得太慢导致FF2的建立时间不能满足。

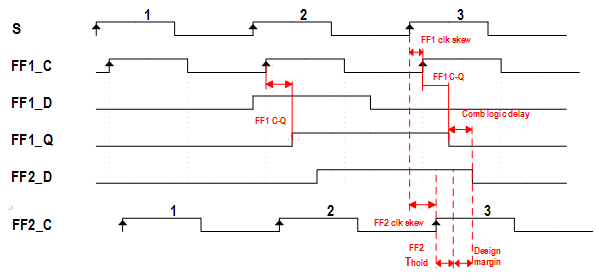

完整的setup time检查时序如下图:

\[T_{clk\_delay}^{FF1} + T_{c->q}^{FF1} + T_{comb\_logic} + T_{setup}<= T_{clk\_delay}^{FF2} + T_{period}

\]

不满足此公式的即为setup violation。

Hold time 检查

相对与setup的检查,hold的检查与时钟周期无关,它实际上检查的是当前上升沿,本级DFF在采样数据时会不会出错。

简单来说,就是查看上图中DFF2在当前上升沿,会不会因为接到DFF2的D端上的数据变化太快导致无法满足保持时间的要求。

时序分析图如下:

根据时序图可以得到:

\[T^{FF2}_{clk\_delay} + T^{FF2}_{Hold}+T_{Design\_margin} = T^{FF1}_{clk\_delay}+T^{FF1}_{C->Q}+ T_{Comb\_logic}

\]

STA要求上面式中的design margin>=0,即:

\[T^{FF1}_{clk\_delay}+T^{FF1}_{C->Q}+ T_{Comb\_logic}-T^{FF2}_{Hold} \ge T^{FF2}_{clk\_delay}

\]

违反此式子就是hold violation.

浙公网安备 33010602011771号

浙公网安备 33010602011771号