STA学习笔记-0

如今的逻辑设计复杂度和工作频率要求越来越高。为了保证设计稳定可靠,必须对设计附加时序约束,对综合实现结果进行时序分析。

导言

时序约束:主要用于规范设计的时序行为,表达设计者期望满足的时序条件,指导综合和布局布线阶段的优化算法等。

时序约束的作用:1、提高设计的工作频率。 2、获得正确的时序分析报告。

静态时序分析(英语:Static Timing Analysis, STA),或称静态时序验证,是电子工程中,对数字电路的时序进行计算、预计的工作流程,该流程不需要通过输入激励的方式进行仿真。

静态时序分析是相对于“动态时序仿真”而言,动态时序仿真占用的时间非常长,效率低下。因此STA成为最常用的分析、调试时序性能的方法和工具。分析每个时序路径的延迟,计算出设计的最高频率,发现时序违规。

STA的目的仅聚焦于时序性能的分析,并不涉及设计的逻辑功能。

本文将介绍STA的理论和方法,后期配合相关时序分析题目检验所学的知识。

下面将介绍时序概念:周期、最大时钟频率、时钟建立时间、时钟保持时间、时钟到输出的延时、管脚到管脚的延时、Slack和时钟偏斜。

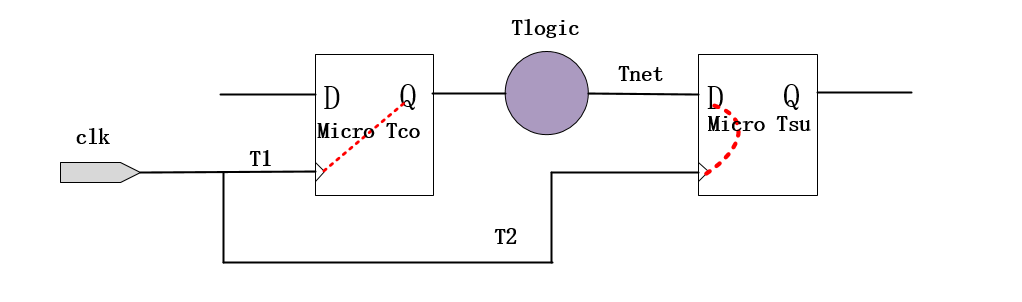

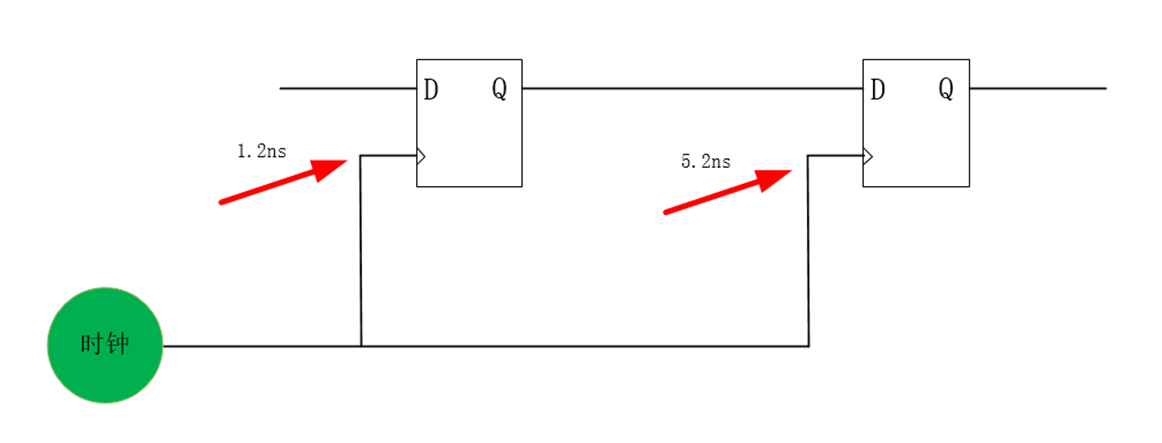

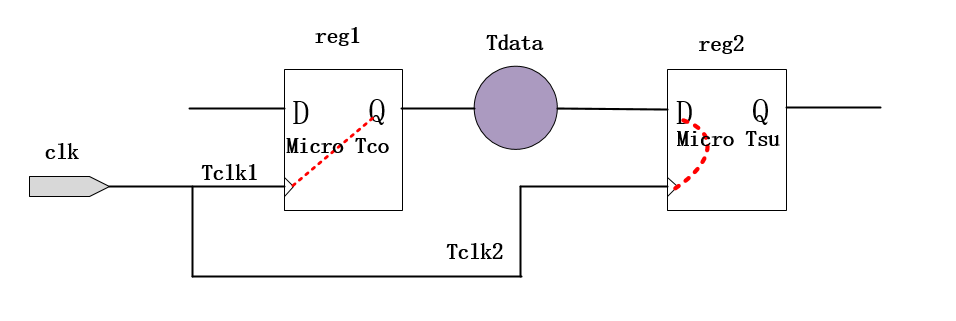

图中Tclk是时钟的最小周期。Micro Tco 是寄存器固有的时钟输出延时,Tlogic 是同步元件之间的组合逻辑延时,Tnet是网线延迟,Micro Tsu 是寄存器固有的时钟建立时间,Tclk_skew 是时钟偏斜。

最小周期和最高频率计算如下:

fmax能综合体现设计的时序性能,是最重要的时序指标之一。

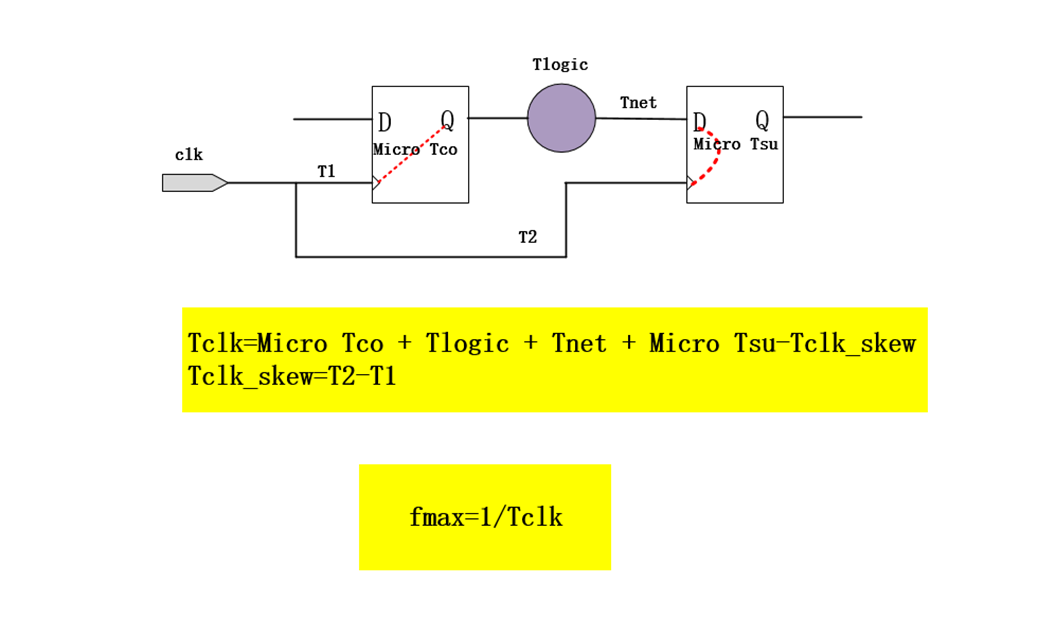

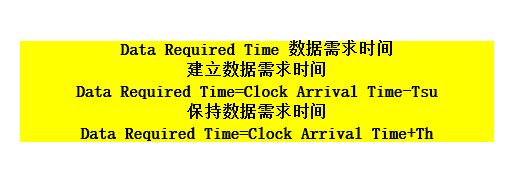

建立时间:输入信号应该提前时钟上升沿(如上升沿有效)T时间到达芯片,这个T就是建立时间:Setup time.如果不满足Setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器。

举个例子:坐火车时需要提前到站检票安检,而不是一到火车站就可以乘坐。必须的提前到站的时间就是建立时间。

保持时间:保持时间是测试芯片对输入信号和时钟信号之间的时间要求。保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间(数据保持不变以便能够稳定读取)。

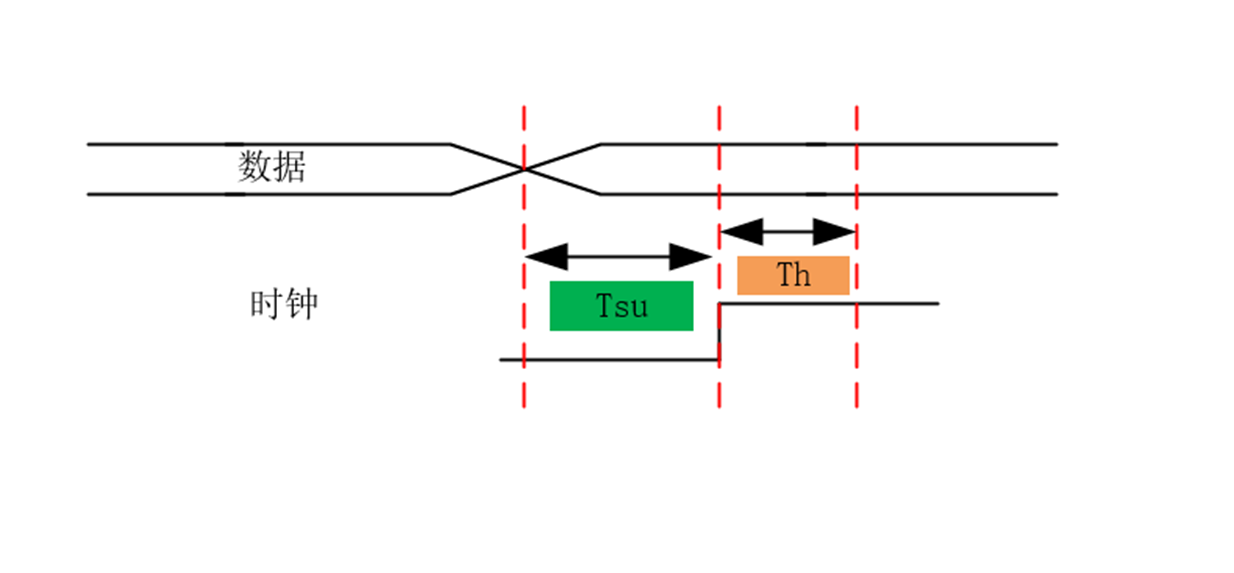

时钟建立时间 Clock Setup Time

Micro Tsu 是寄存器固有的时钟建立时间,触发器固有属性,通常小于1ns。

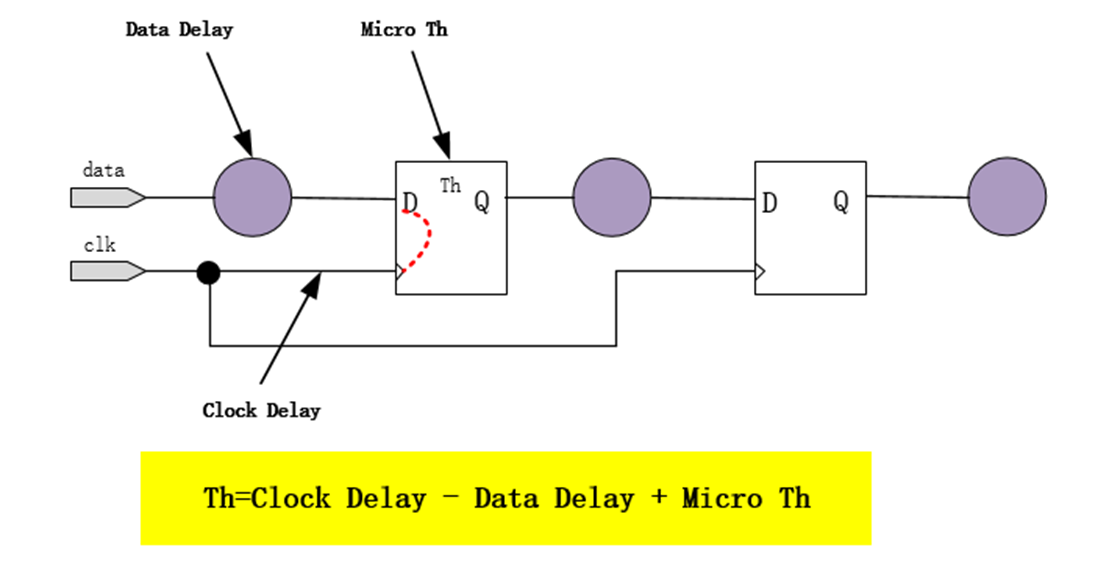

时钟保持时间 Clock Hold Time

Micro Th 是寄存器固有的时钟保持时间,触发器固有属性,通常小于1ns。

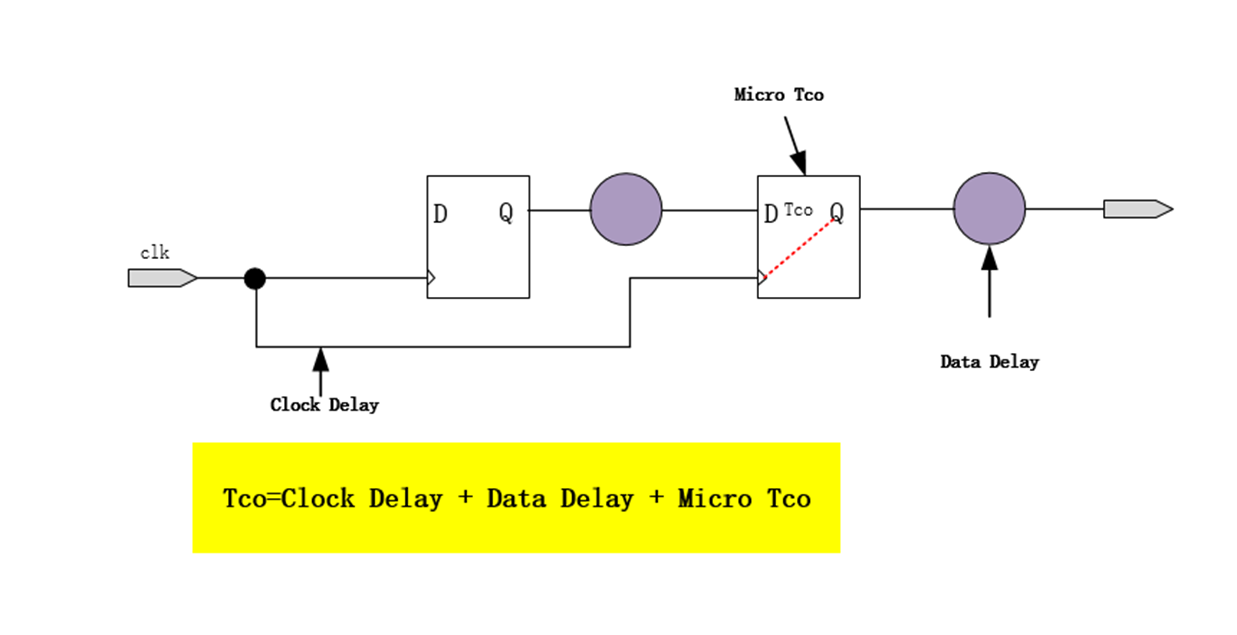

时钟输出延时 Clock Output Delay

定义:指的是在时钟有效沿到数据有效的最大时间间隔。

Micro Tco 是寄存器内部延时参数,触发器固有属性,通常小于1ns。

引脚到引脚的延时 Pin to Pin Delay

时钟偏斜 Clock Skew

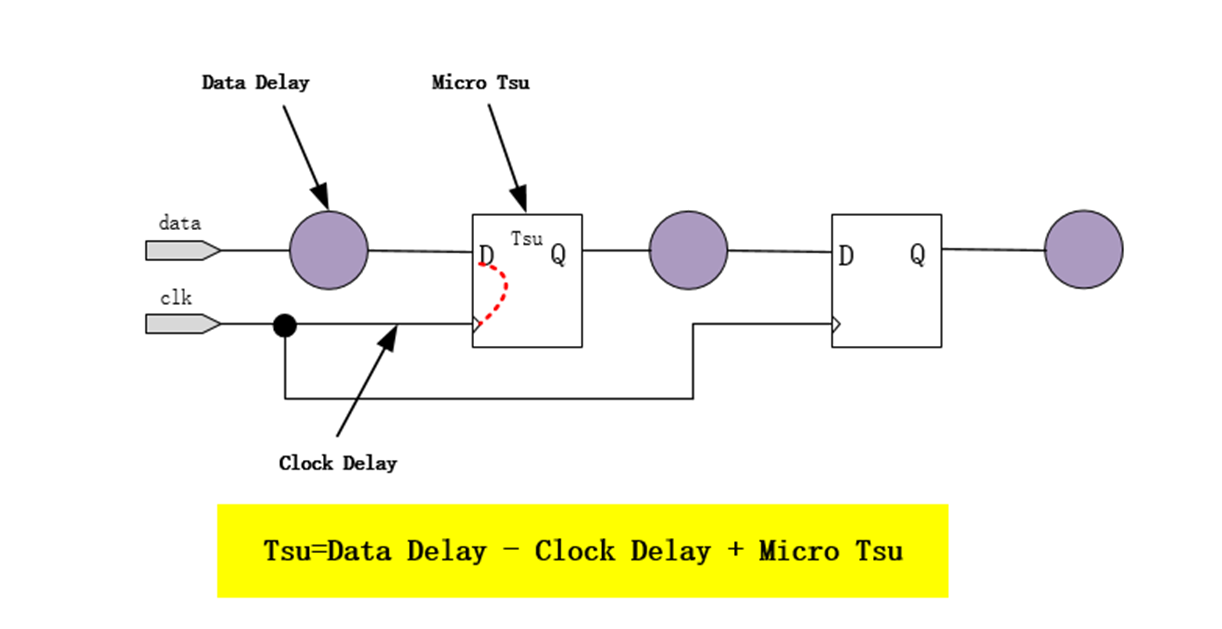

以下面为例,静态时序分析:

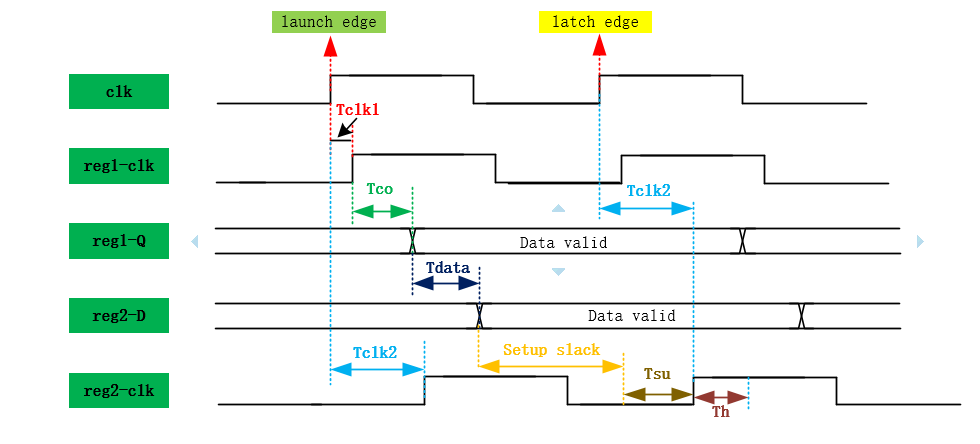

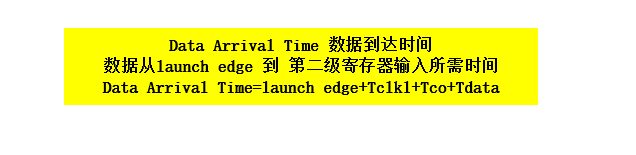

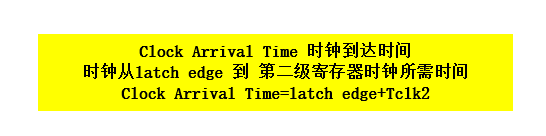

launch edge : 时钟源第一个上升沿对应时刻,数据发送沿。STA以该时刻为0时刻。

latch edge : 时钟源第二个上升沿对应时刻,数据接收沿。STA以该时刻为结束时刻。

Tsu :建立时间。 Th :保持时间。 Tco : 时钟输出延时。 Tdata : 两个REG中组合逻辑延时。 Tskew: 时钟偏斜。

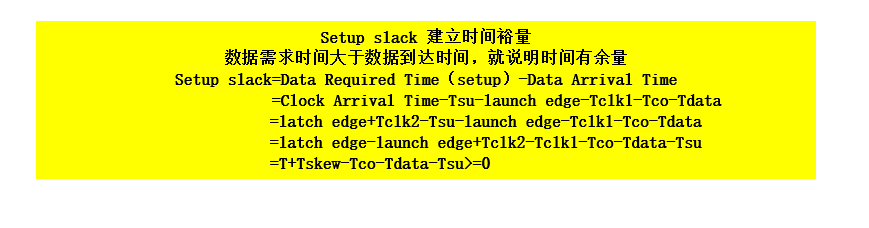

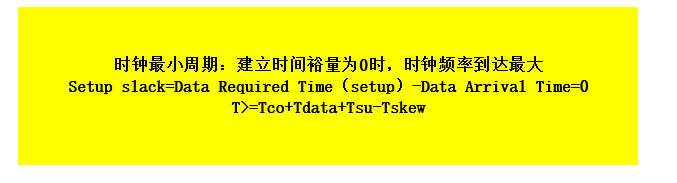

STA分析核心公式:T+Tskew-Tco-Tdata-Tsu>=0 满足此不等式,即可判断是否满足建立时间裕量,即满足时序要求。

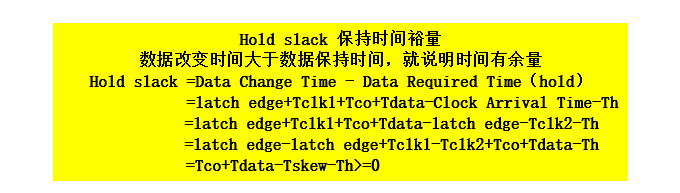

保持时间约束条件:Tco+Tdata-Tskew-Th>=0

参考资料:1、建立时间_百度百科 (baidu.com)

3、Intel FPGA/CPLD设计

4、(105条消息) 静态时序分析(STA)概念 例题_昨日傍晚的博客-CSDN博客_静态时序分析题目

浙公网安备 33010602011771号

浙公网安备 33010602011771号