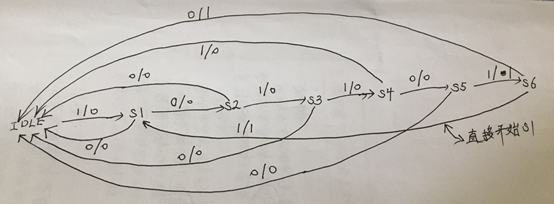

画出可以检测10010串的状态图

状态转换图:

module det( input clk, input rst_n, input d, //数据输入 output reg y //检测结果输出 ); /* 检测101101 */ //状态编码 parameter idle=3'b000; //空闲状态 parameter s1=3'b001; //检测到1 parameter s2=3'b010; //检测到10 parameter s3=3'b011; //检测到101 parameter s4=3'b100; //检测到1011 parameter s5=3'b101; //检测到10110 parameter s6=3'b110; //检测到101101 reg[2:0]cur_state,nxt_state; always@(posedge clk or negedge rst_n) if(!rst_n) cur_state<=idle; else cur_state<=nxt_state; always@(cur_state,d) begin case(cur_state) idle: begin if(d==1'b1) nxt_state<=s1; else nxt_state<=idle; end s1: begin if(d==1'b0) nxt_state<=s2; else nxt_state<=idle; end s2: begin if(d==1'b1) nxt_state<=s3; else nxt_state<=idle; end s3: begin if(d==1'b1) nxt_state<=s4; else nxt_state<=idle; end s4: begin if(d==1'b0) nxt_state<=s5; else nxt_state<=idle; end s5: begin if(d==1'b1) nxt_state<=s6; else nxt_state<=idle; end s6: begin if(d==1'b1) nxt_state<=s1; else nxt_state<=idle; end default:; endcase end always@(posedge clk or negedge rst_n) if(~rst_n) y<=1'b0; else if(nxt_state==s6) y<=1'b1; else y<=1'b0; endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号