详细介绍:考研复习-计算机组成原理-第五章-CPU

本文章仅供本人自己学习使用,仅仅补充书上没有的内容

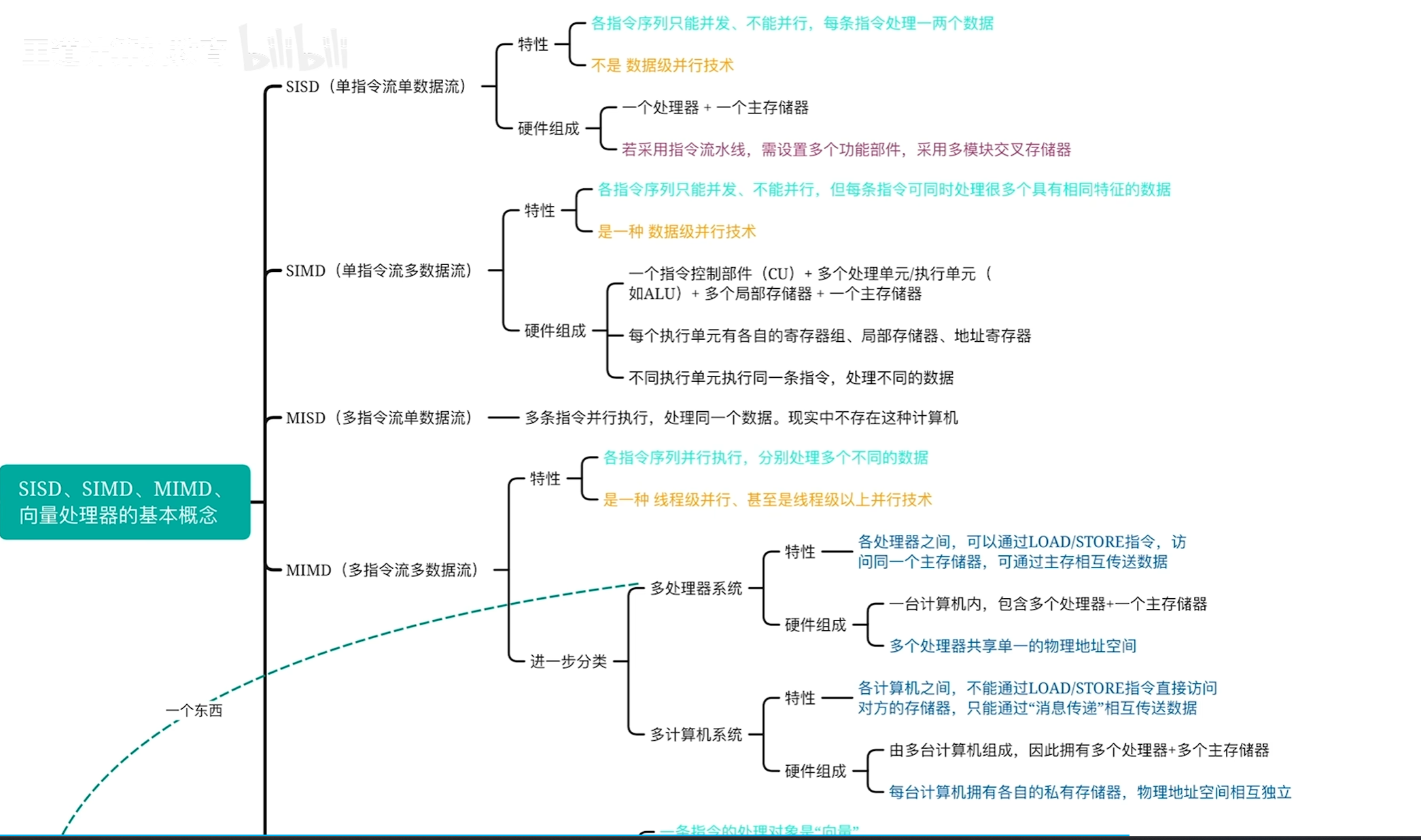

多处理器基本概念

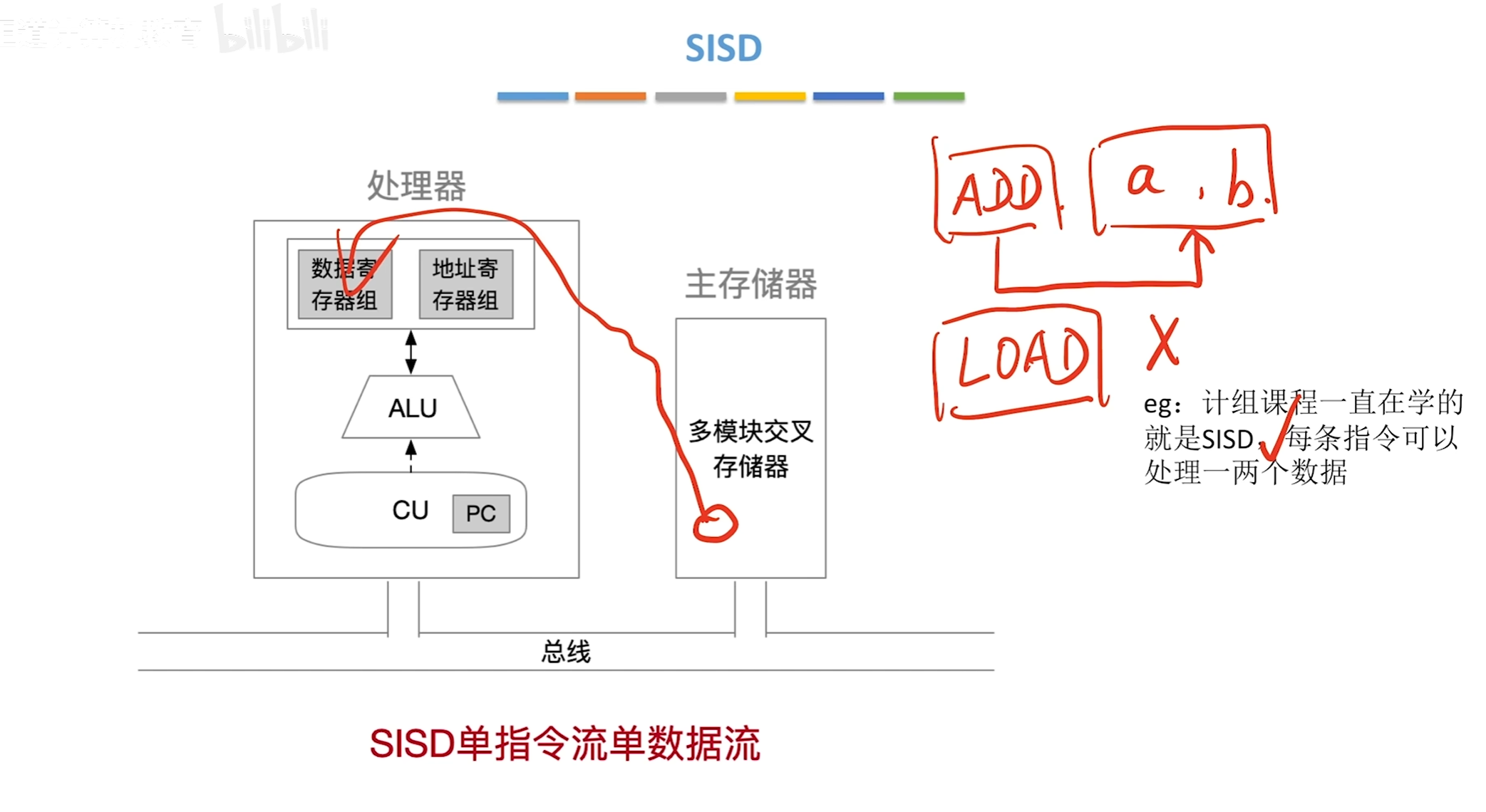

SISD

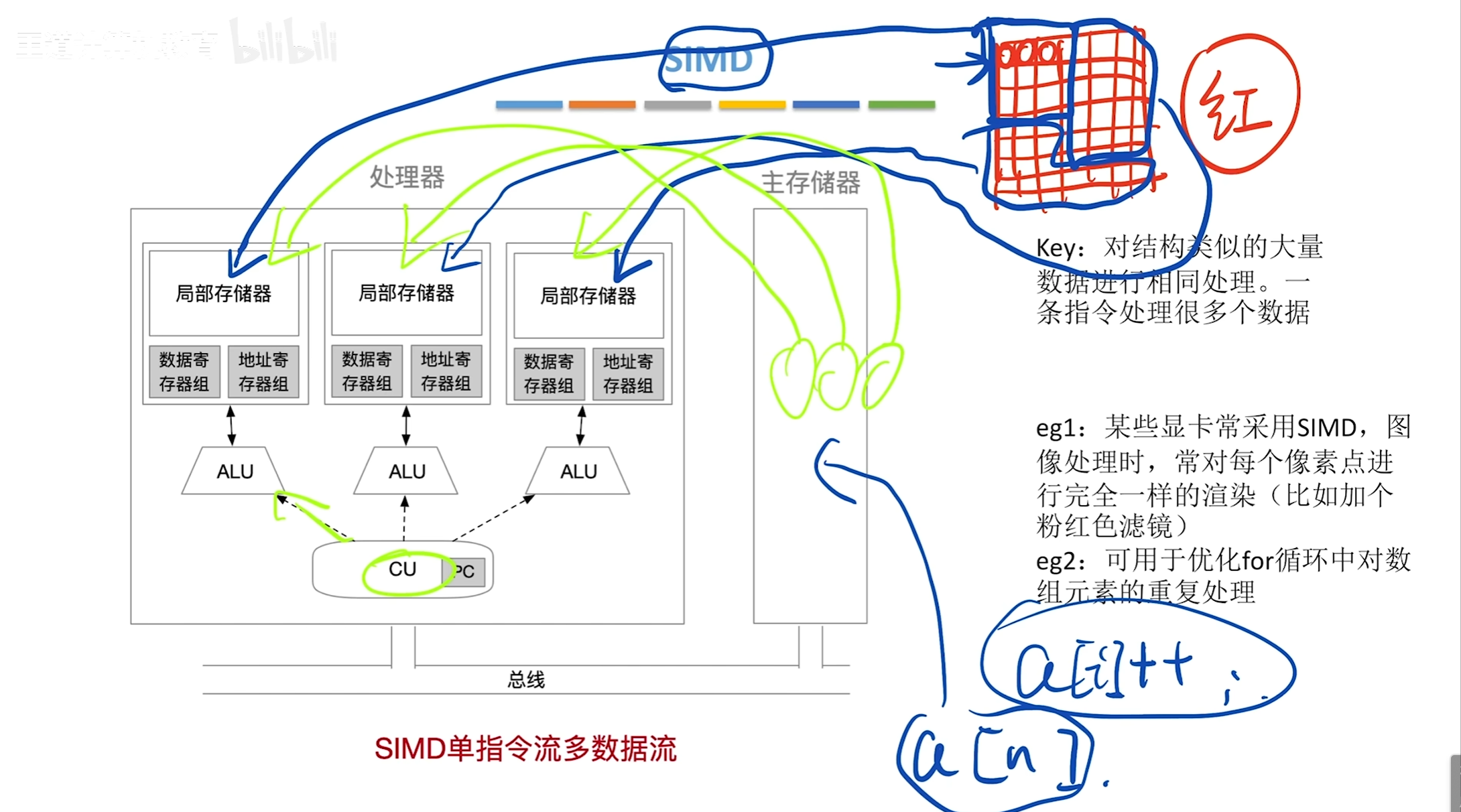

SIMD

可对批量重复性操作特征相同数据快速处理

每条指令可以调用多个运算器

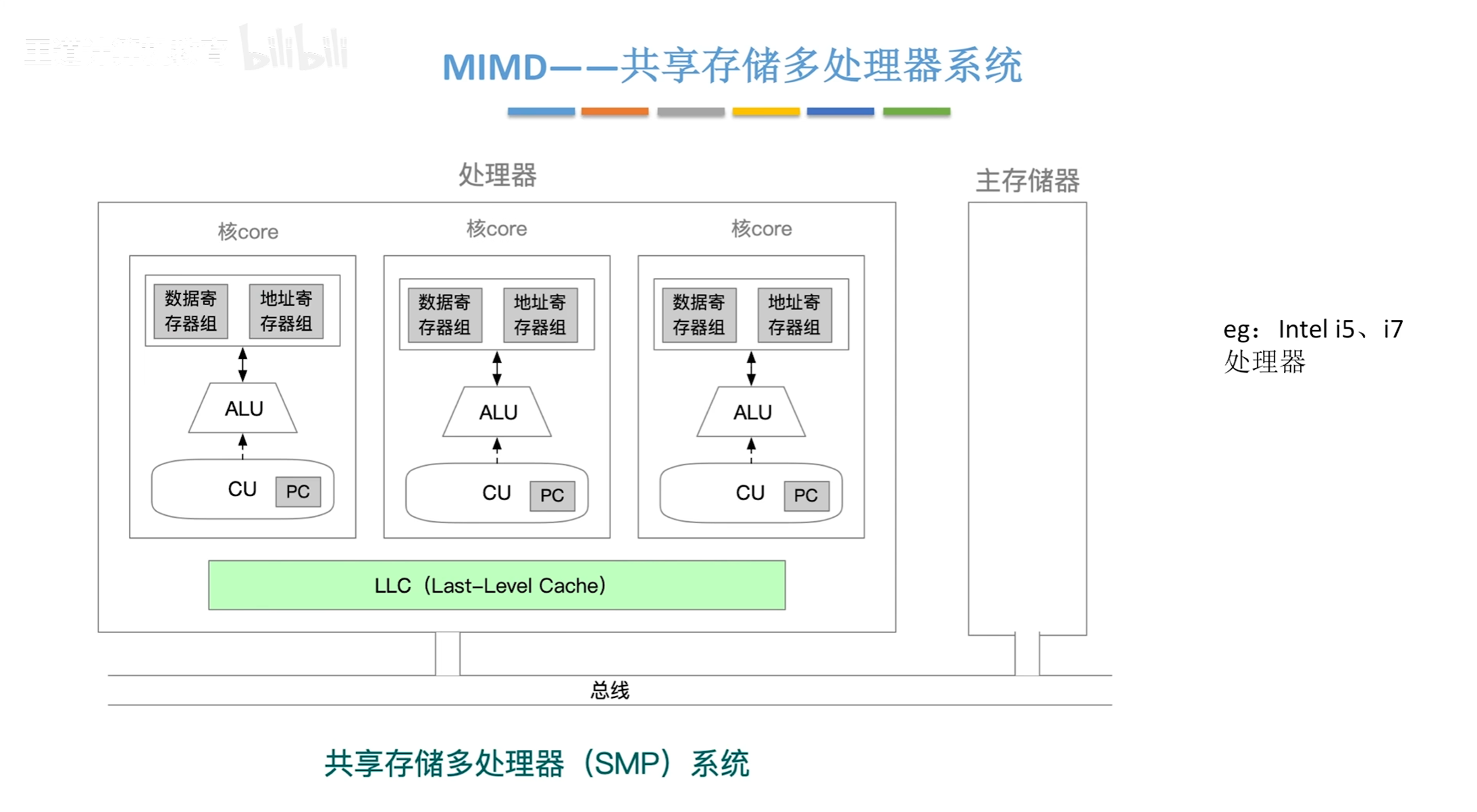

MIMD

总结

相近知识点统一颜色

总线定时

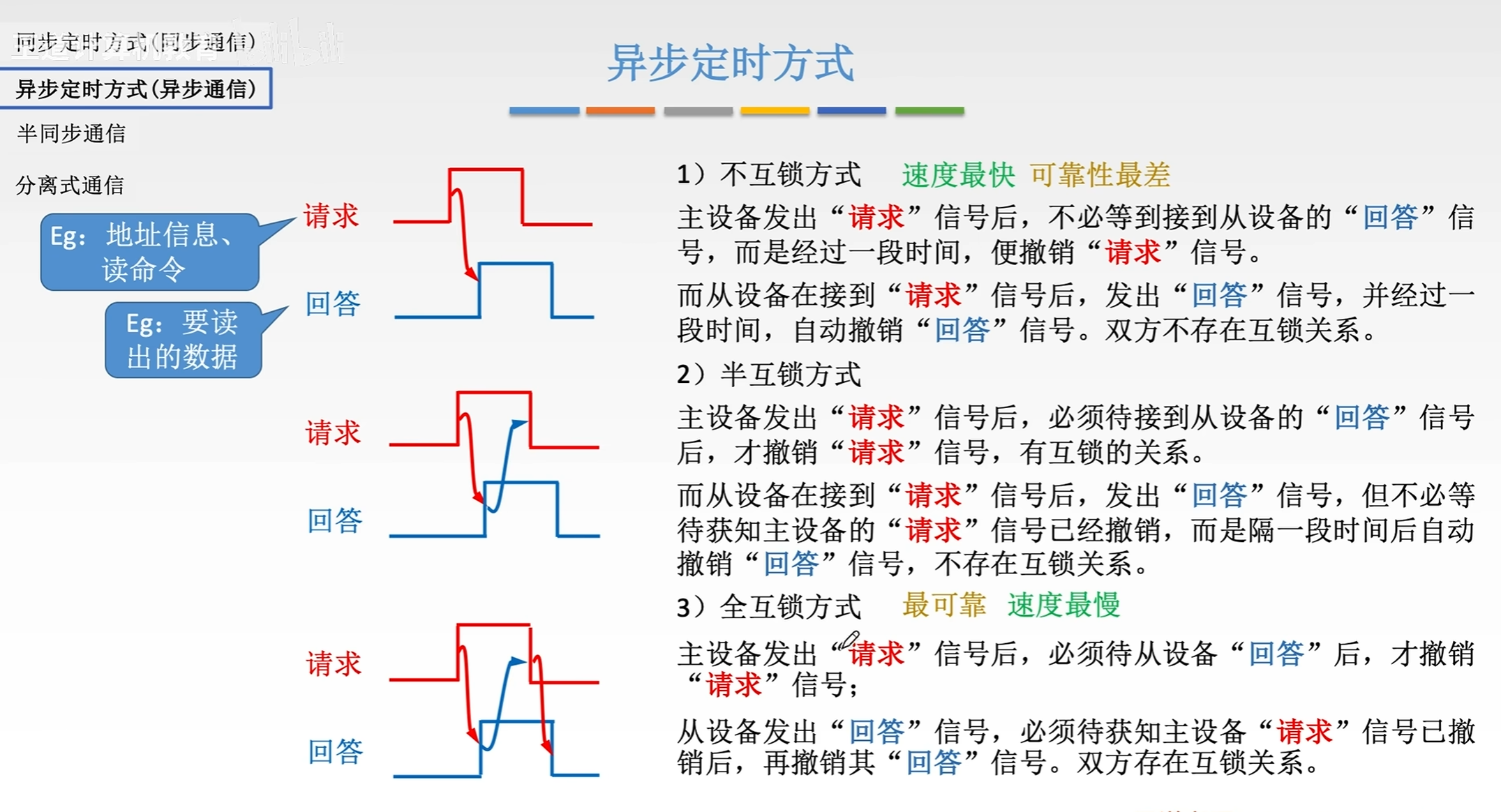

异步定时

如下所示的图示解释了二者之间的关系

半互锁:主设备请求信号必须从设备回应才能撤销,但从设备可直接撤销回答信号而不等主设备

通过全互锁:双方都需要等待对方的信号,即从设备应该听到主设备的“我已经收到了你的回答”之后他才能够撤销答信号

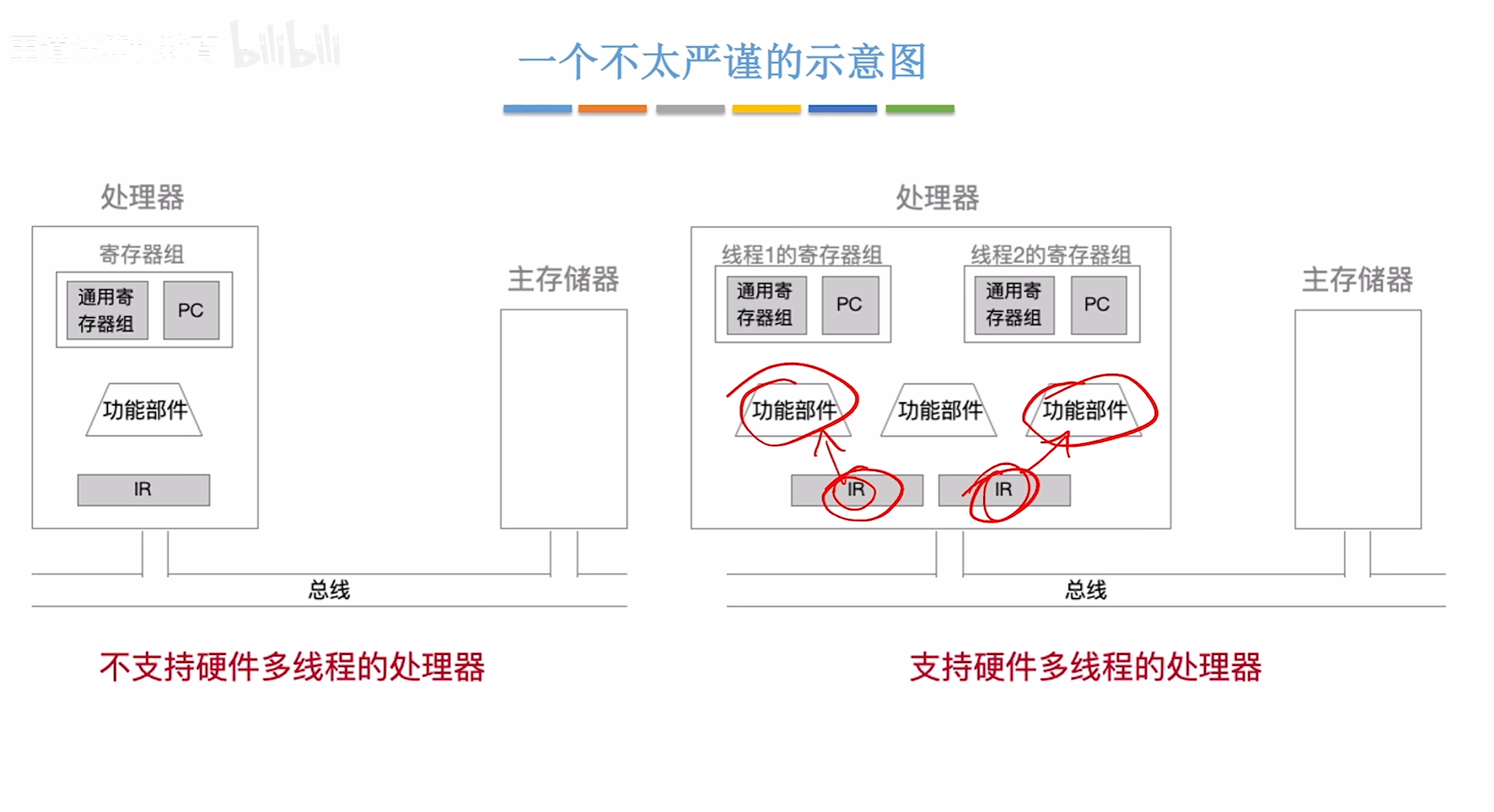

硬件多线程

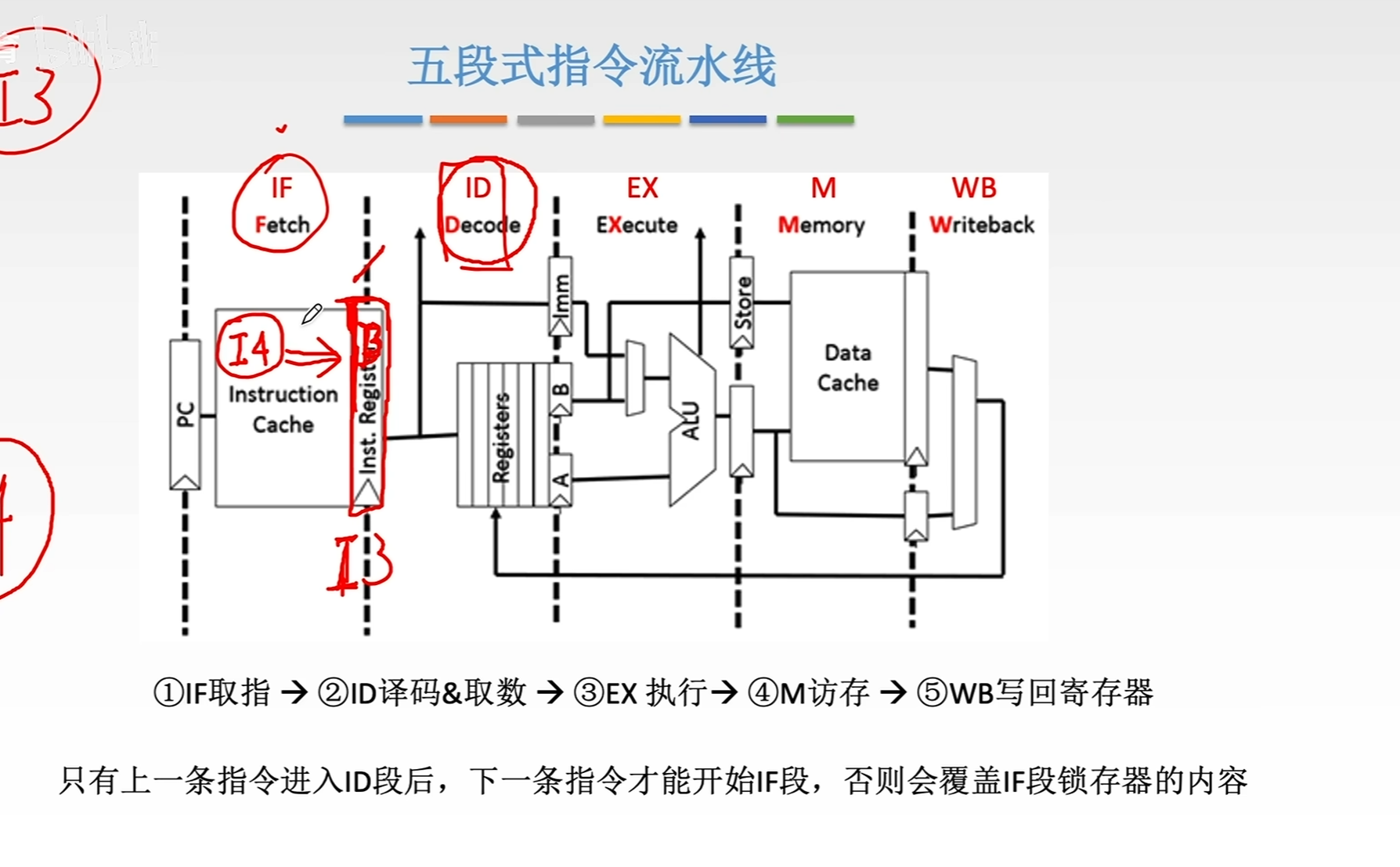

五段式指令流水线

其结构如下

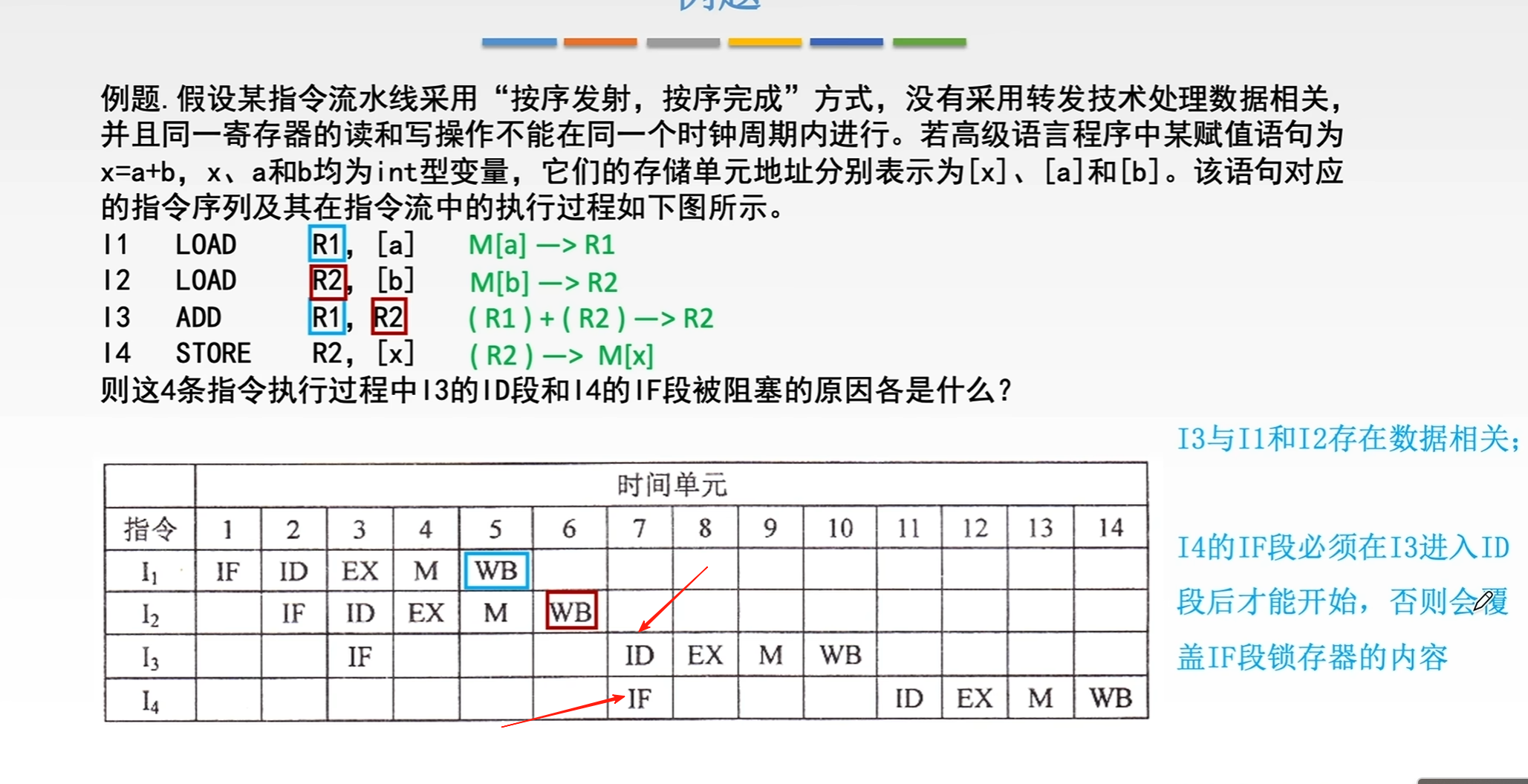

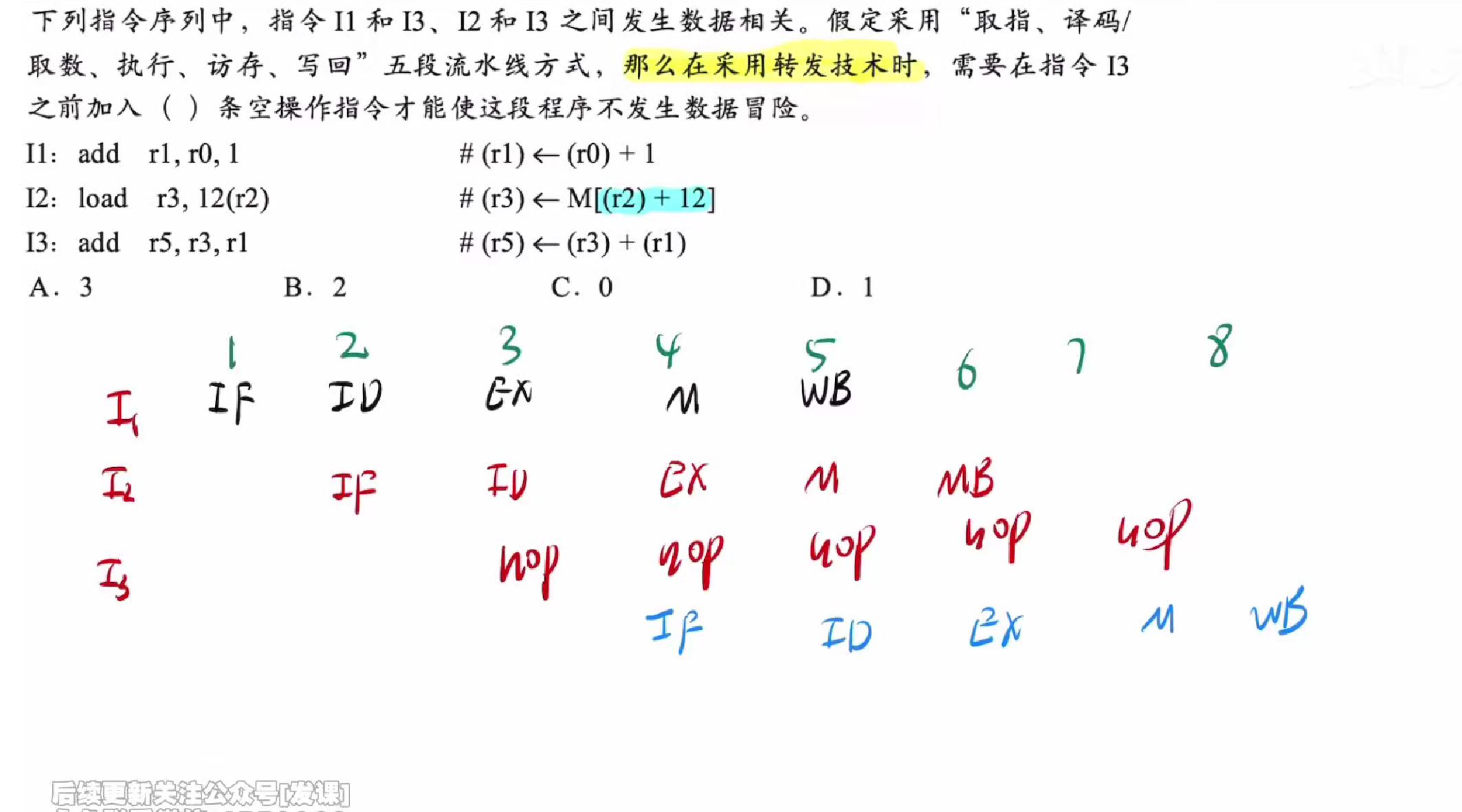

对于题目中的I3来说,为什么ID(译码/读寄存器)阶段为什么会放在7?

我们可以发现,前面两条指令都是取数指令,将取出来的数放到I3指令所需要的寄存器当中

所以I3在数据完全放回的时候才能够进行读寄存器的操控

而数据写回寄存器的操控是在WB阶段才会写回

所以ID最早只能在7开始

那么I4为什么会位于I3后面执行呢,即7这个时间段

他是一个存数指令,当I3再等待I1I2写回的时候,其指令位于IF阶段的Instruction Register(指令寄存器)当中,于是你要是取出I4的指令那么会造成覆盖掉I3的指令,只有当I3进入ID阶段后即不再需要指令提供信息那么就可以执行I4的操作

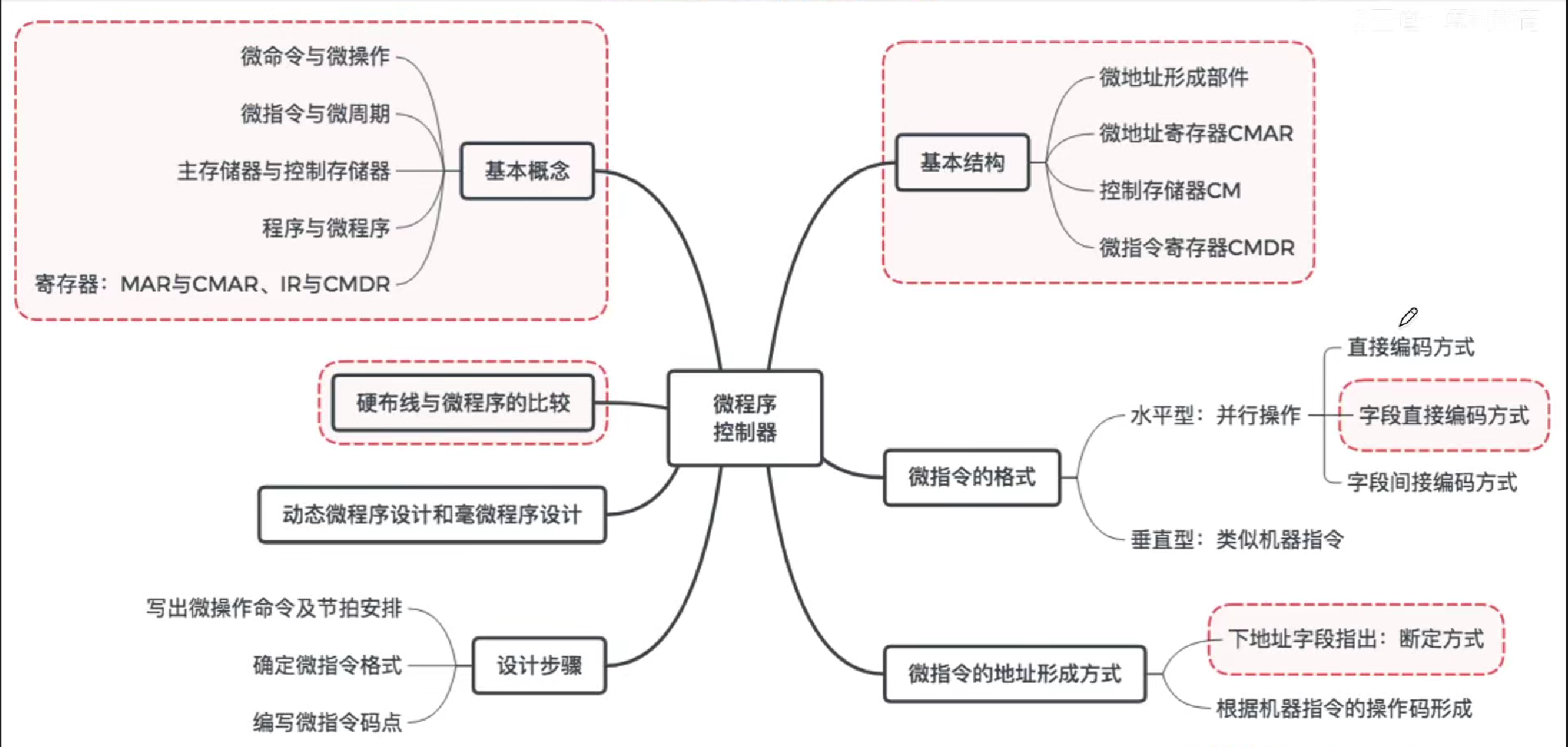

控制器的功能及其工作原理

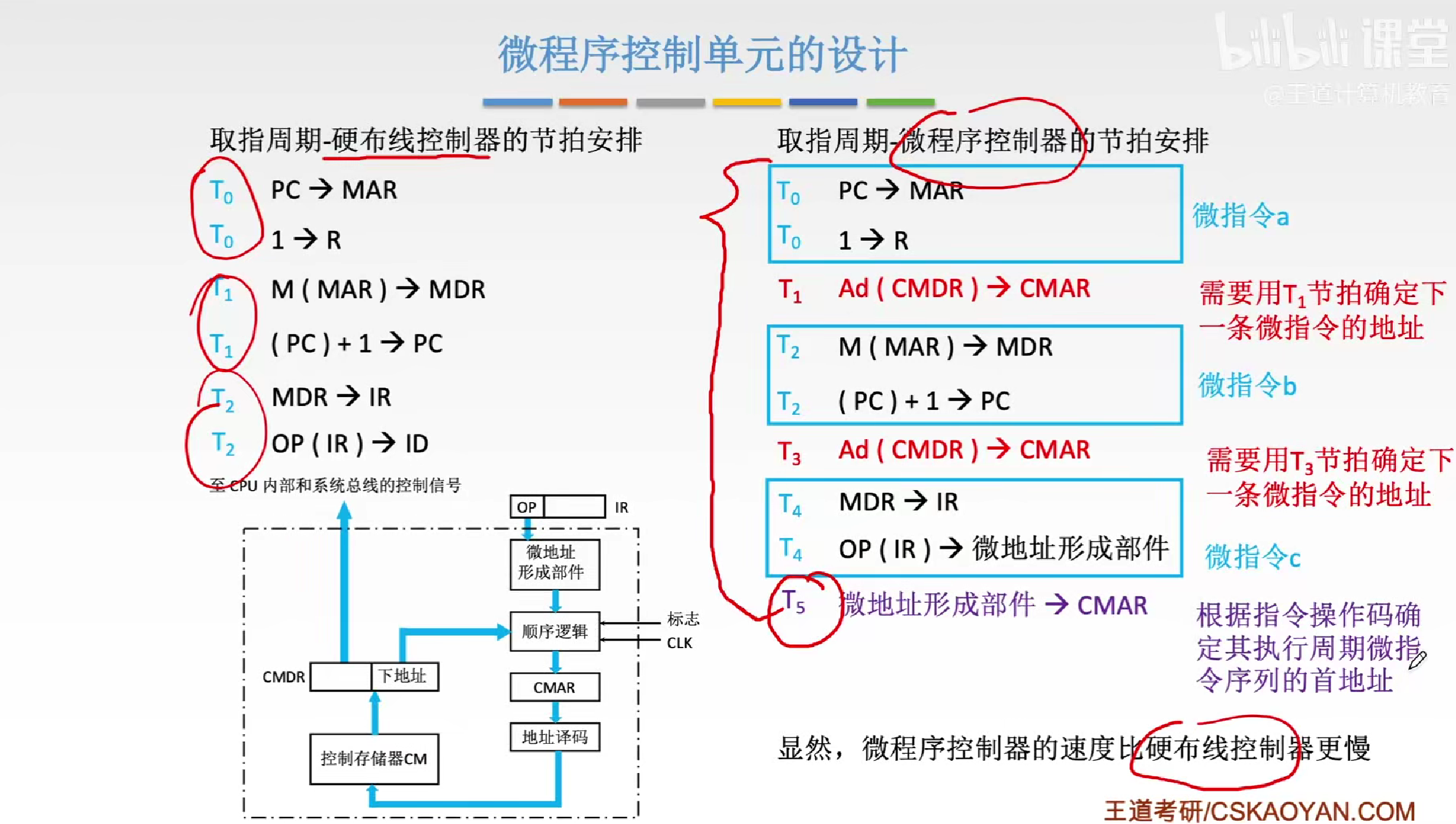

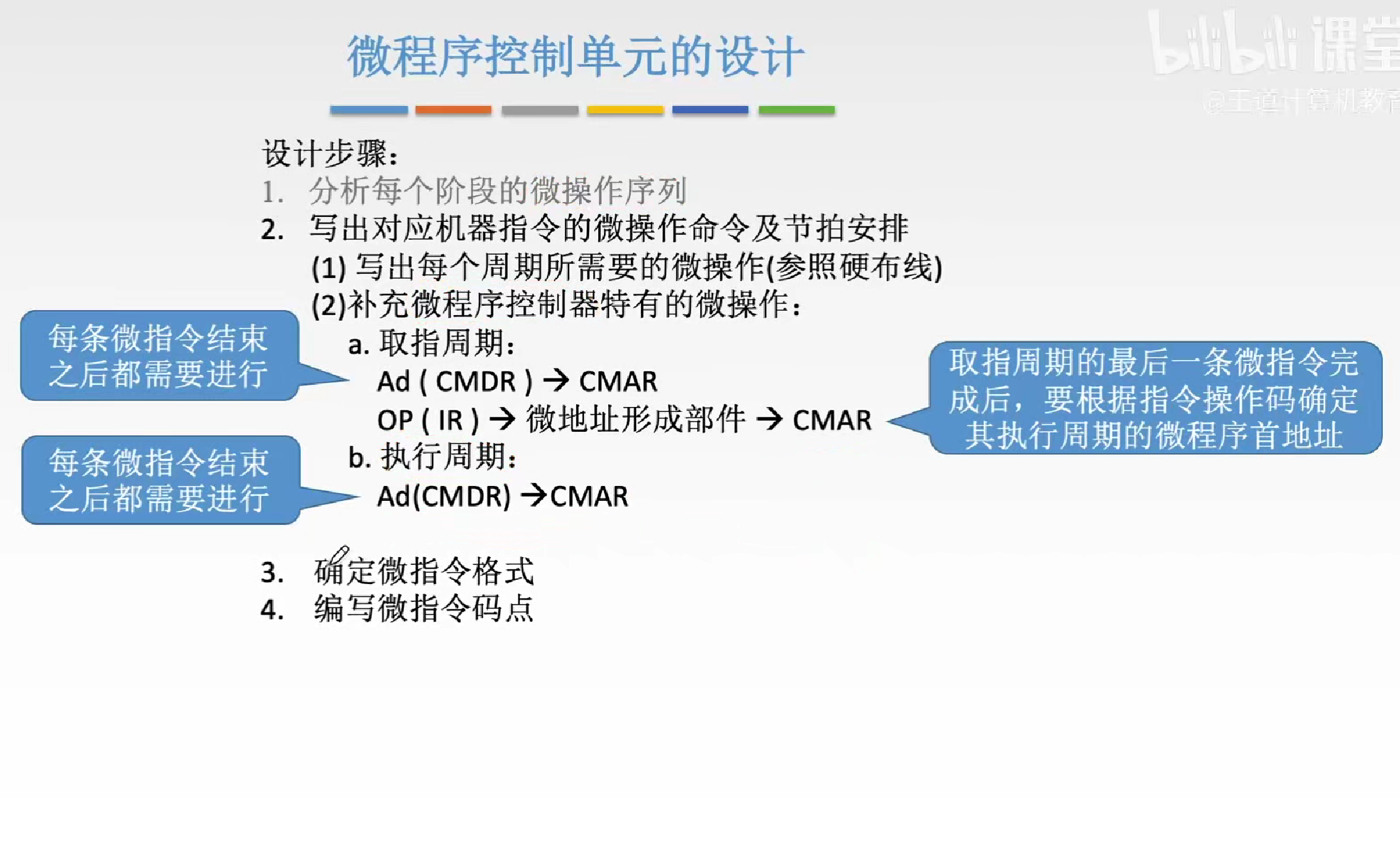

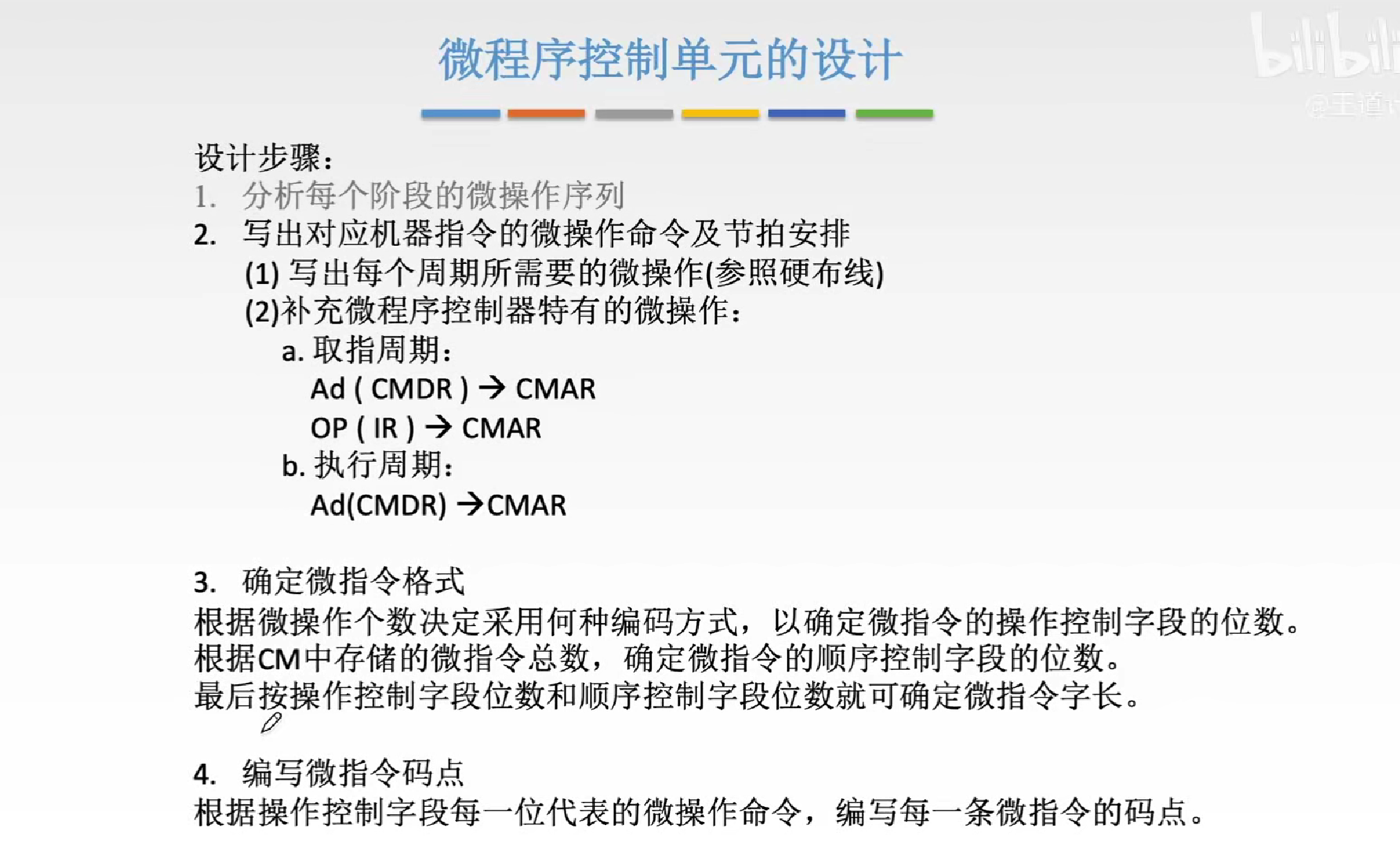

微程序控制单元设计

因为需要额外的传入CU里面的微指令信息

于是必须花费更多的时间

其中T4阶段的微地址形成是出于当前指令的执行阶段,而前面的是公共部分

其中Ad(CMDR)->CMAR是指定下一条微指令的地址

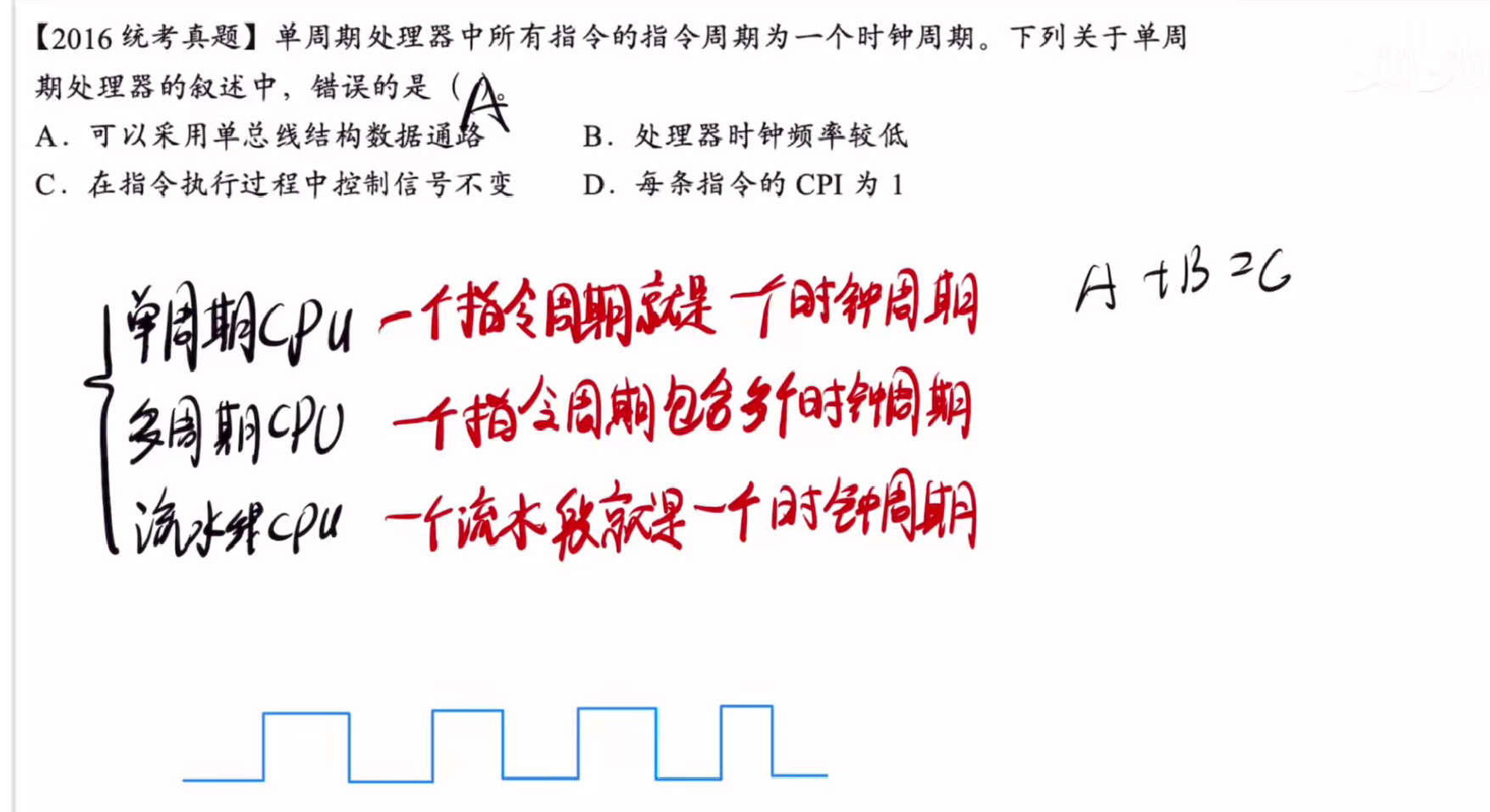

错题

5.6.13

写回阶段可以是M到ex阶段,之后就是如下所示的时序图

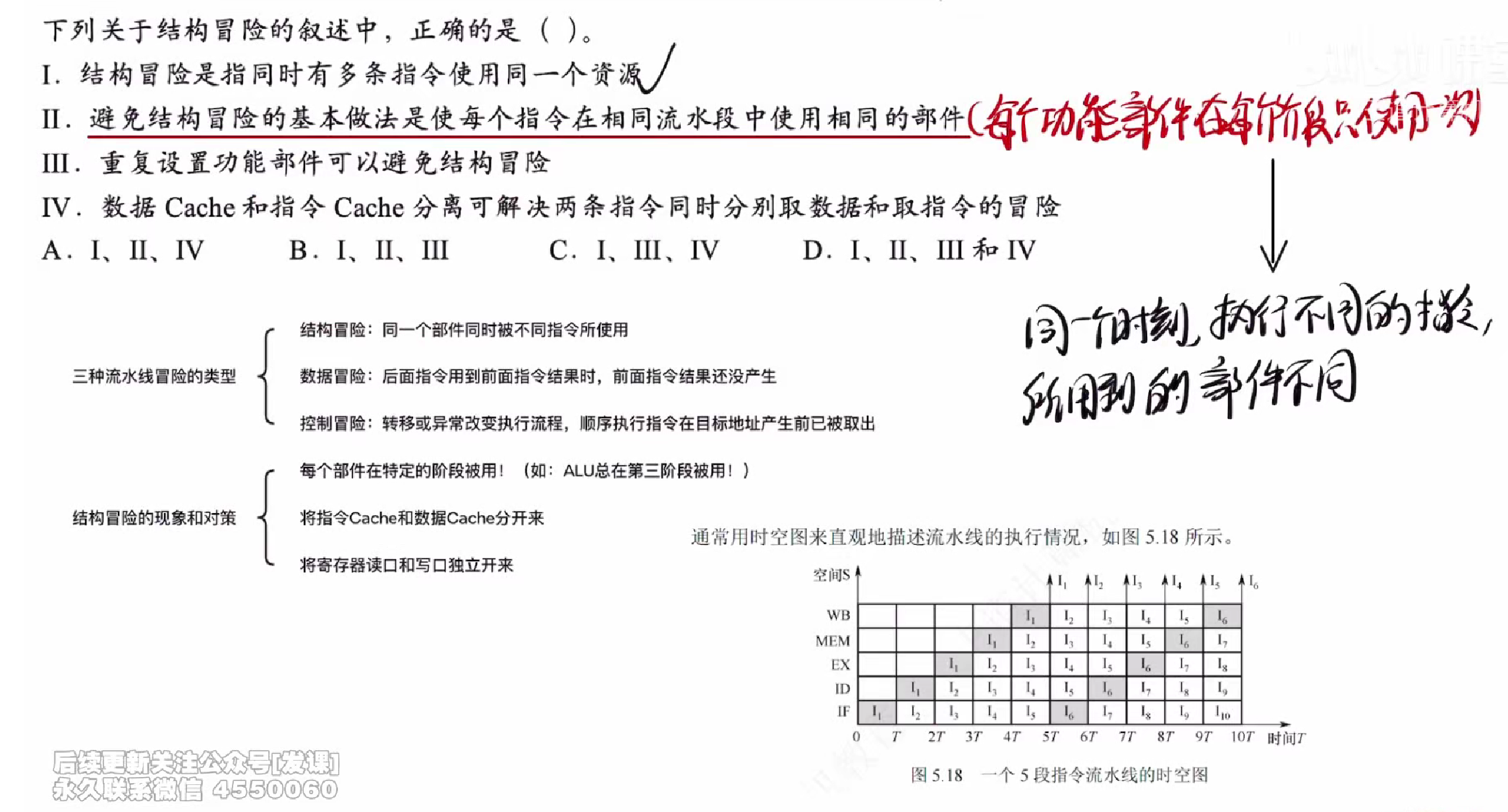

5.6.09

Ⅱ为什么对主要是因为有一个前提那就是每个功能部件在每个阶段只能被使用一次,因而说流水线技术每一个时间段的各个任务都是不同的阶段,所使用的部件都只能被应用一次不会发生抢占冲突,因为一定需要等待别人使用完毕

所以答案:D

5.6.08

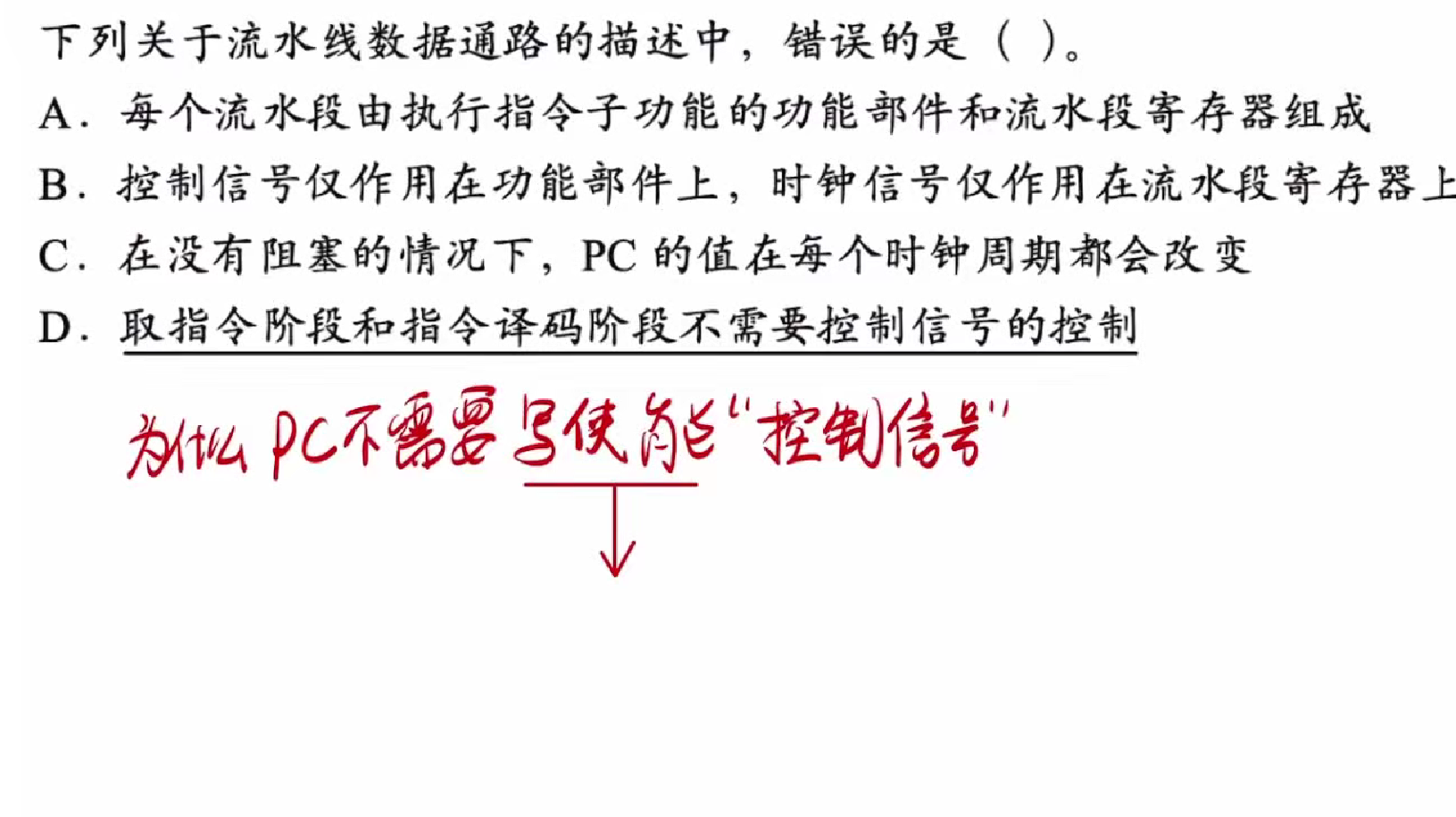

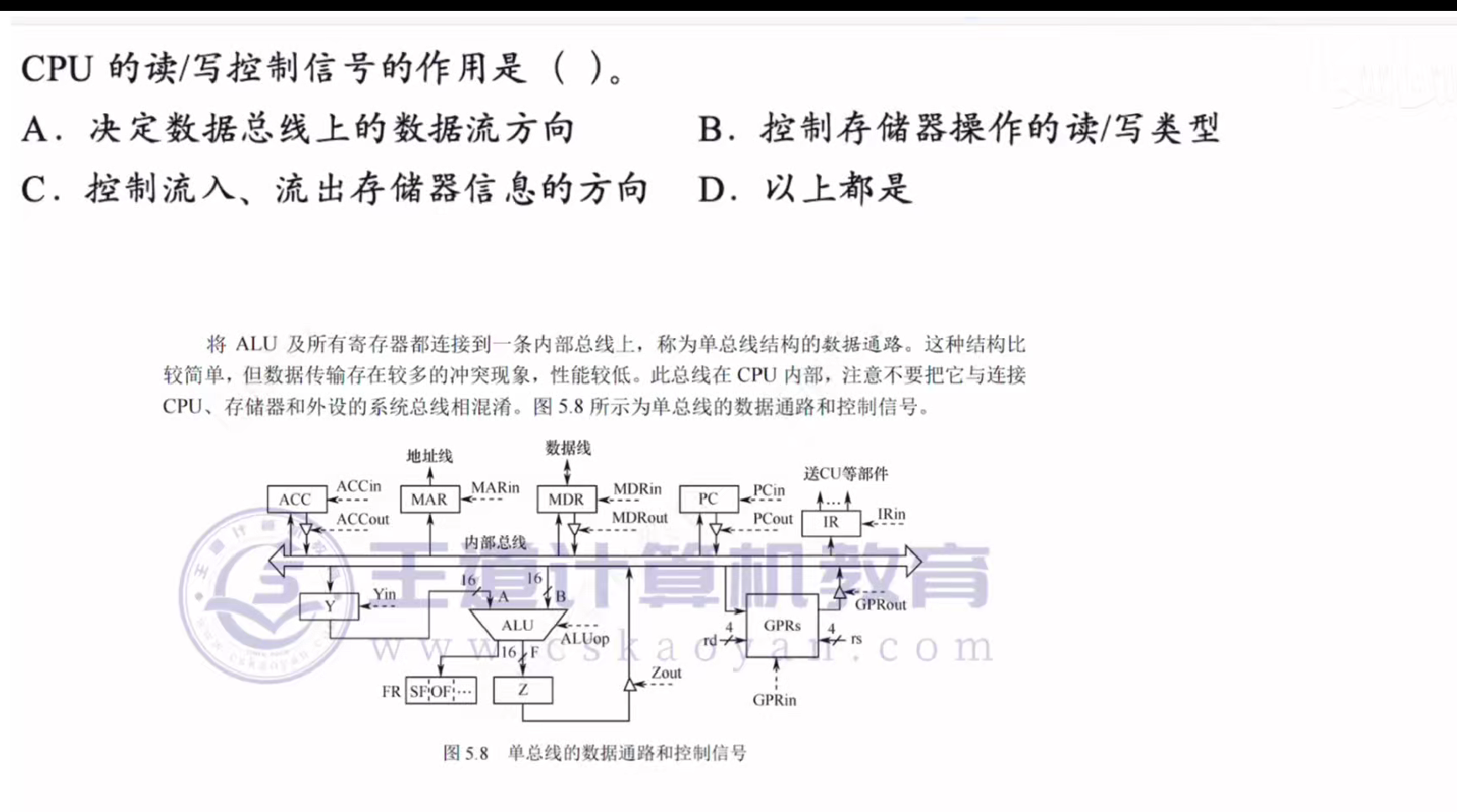

如图所示流水线数据通路如下所示(注意和先前提到的单总线数据通路区分开)

一个时钟信号就是在现代的流水线cpu中,每一个阶段就

通过而流水线的过程中,每一个时期都会进行一个取指令和析指令的过程,所以他们是每个阶段都要做的,能够采用时钟信号控制,于是由此选择B

一个公共的部分,不应该专门的控制信号来进行控制,只要求根据时钟信号刺激电子元件让它读写数据即可就是而取指令和指令译码阶段如我所说都

5.6.02

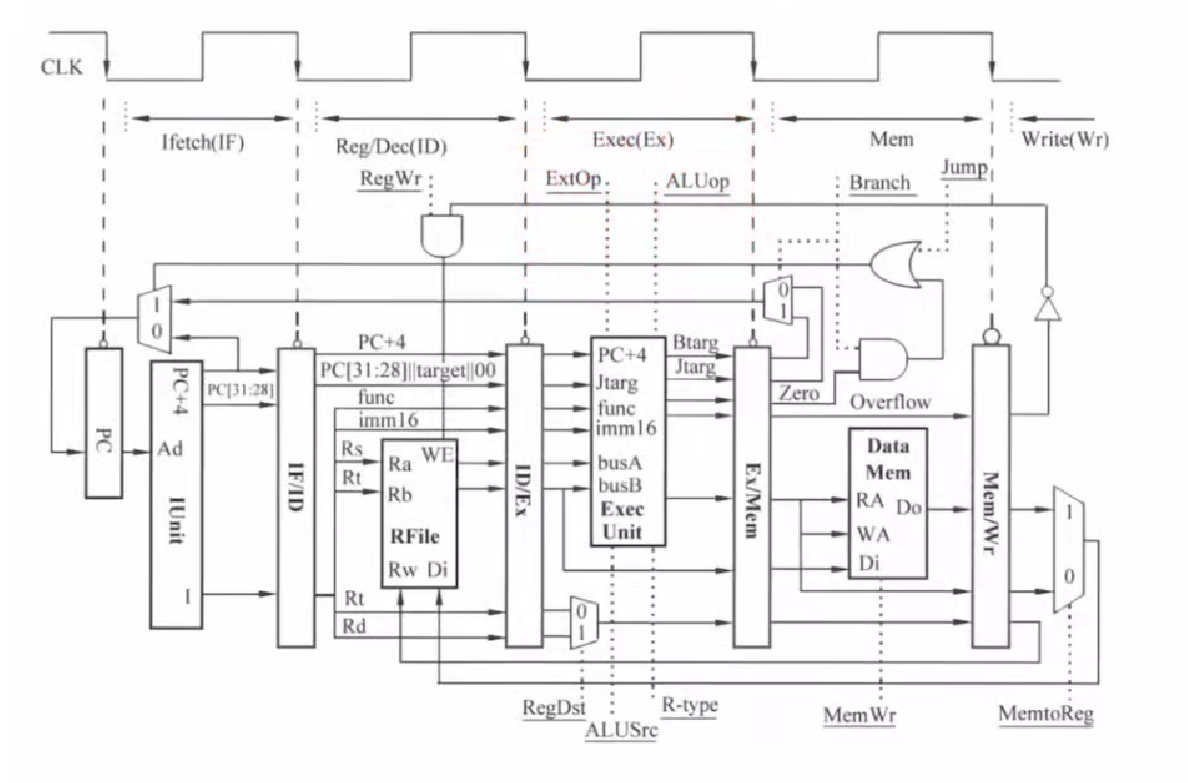

如图所示,吞吐率指的是任务数/流水线执行时间

举例子说明

所有指令的取指令阶段结束然后我们发现图中每隔一个时段就会执行一条指令就是而稳定时指的

所以是1/1的比例

其依旧需要五个阶段,即五个时间内完成五条指令就是而并行指的是所有指令可同时执行,但

5/5=1/1

所以吞吐能力相等

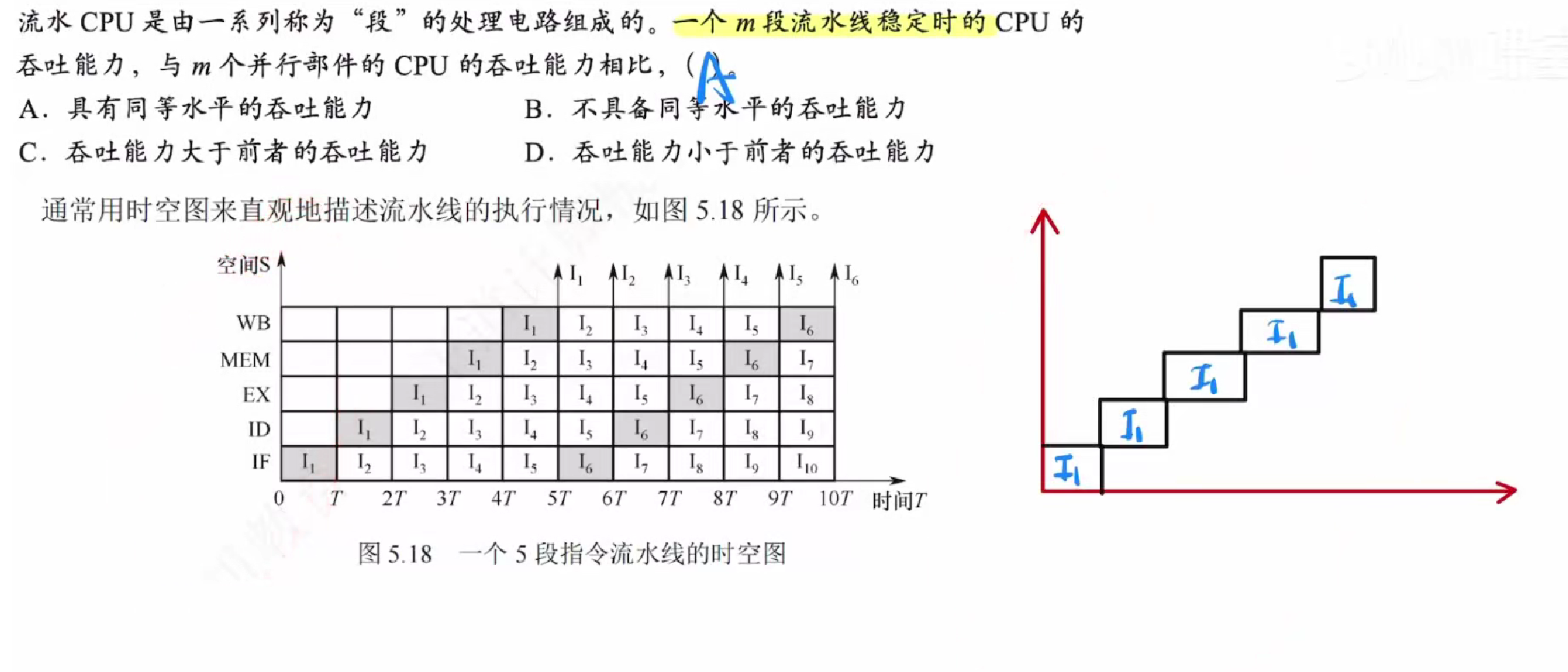

5.6.01

答案:D

空间并行性指的是利用额外空间来处理的并行性

流水线指的是时间并行性

答案:A

因为ALU只有一端链接总线另一端链接暂存寄存器,那么当执行加法指令时一个指令需要在一个时钟周期内完成就不能是单总线。

答案:D

记住就行

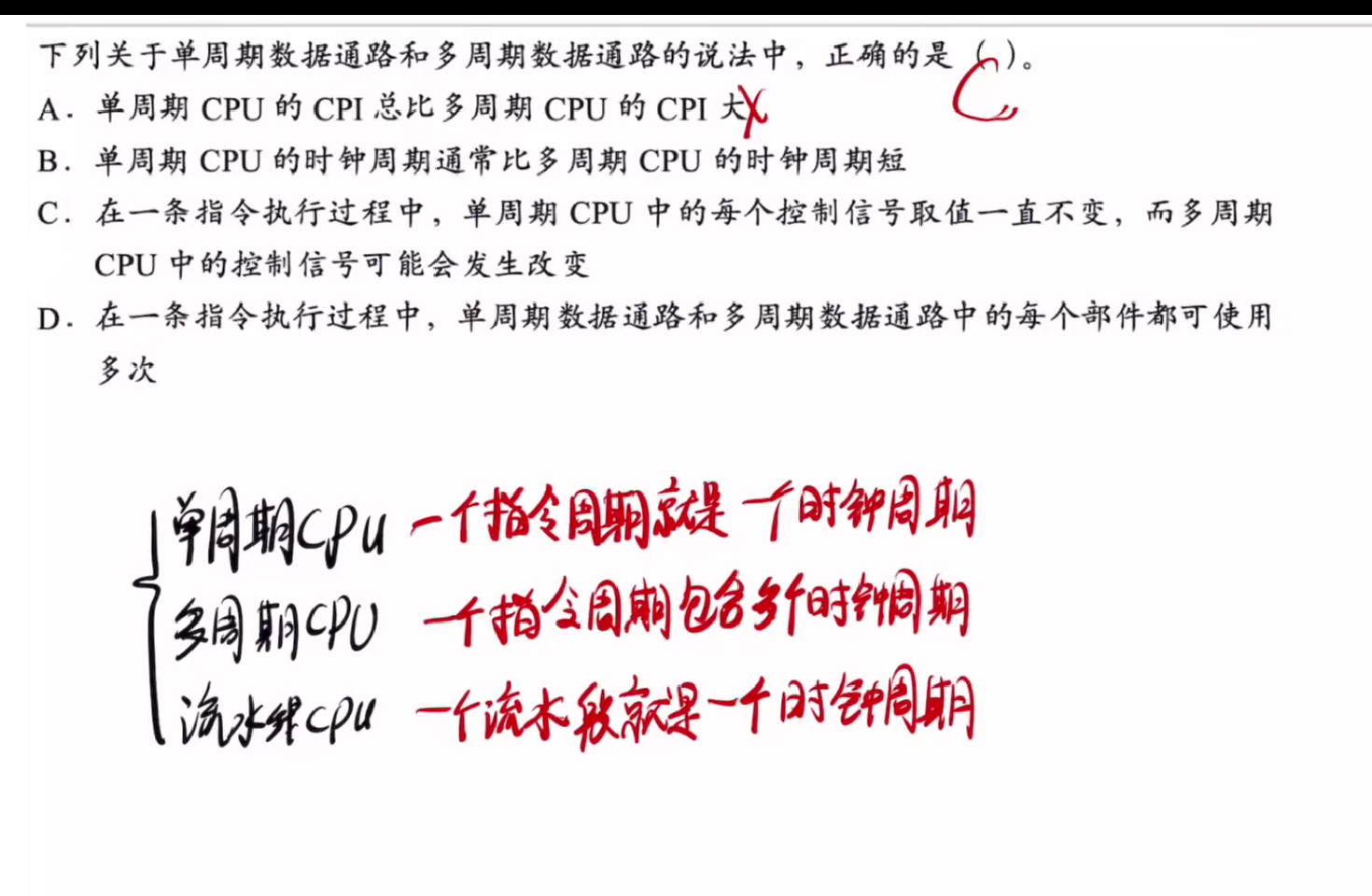

每个部件再单时钟周期内只能被改变一次,

答案:C

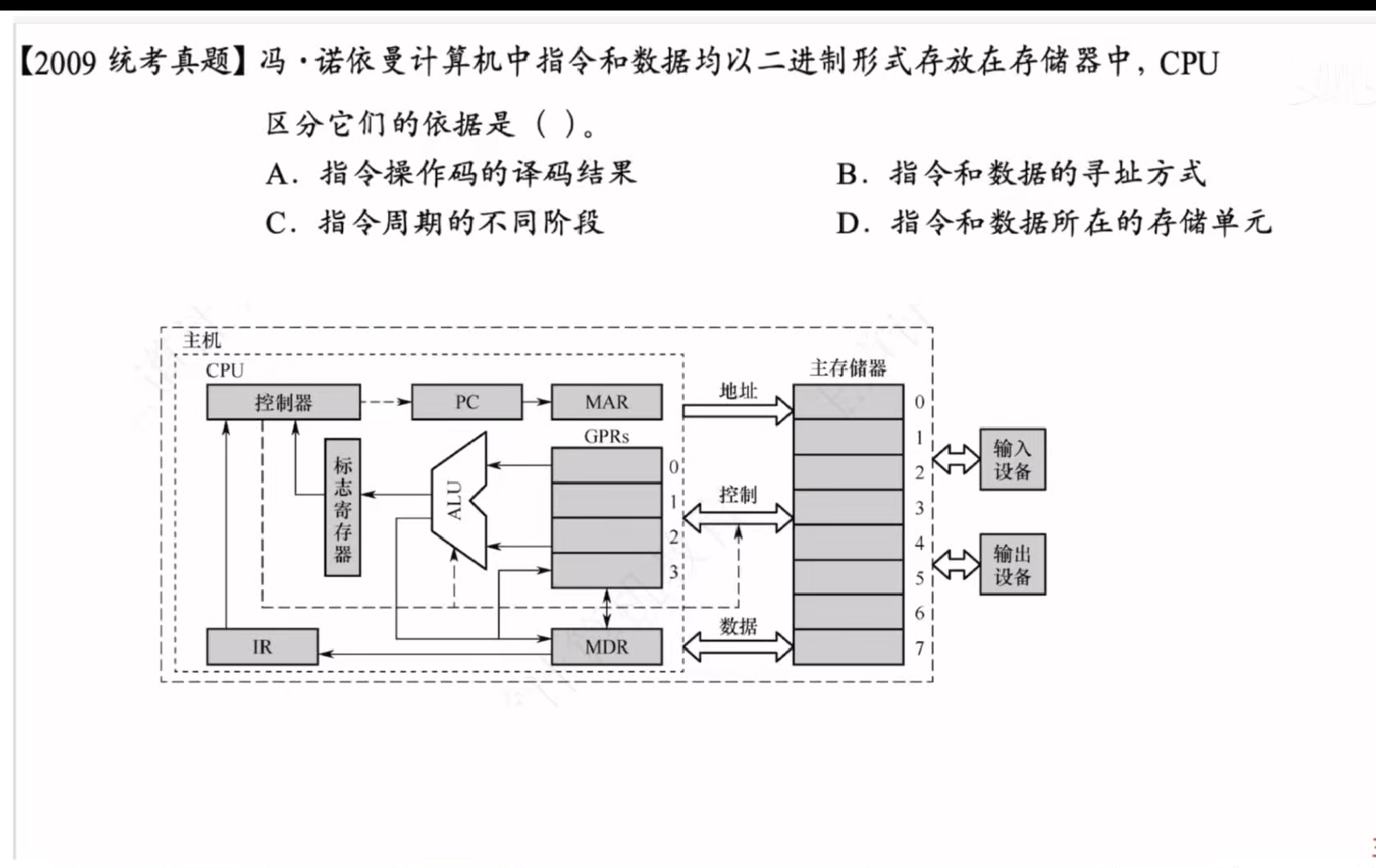

指令周期地不同阶段是指的是cu取出一个主存的存储材料后,在mdr当中进行分析选择送入ir还是寄存器

答案:B

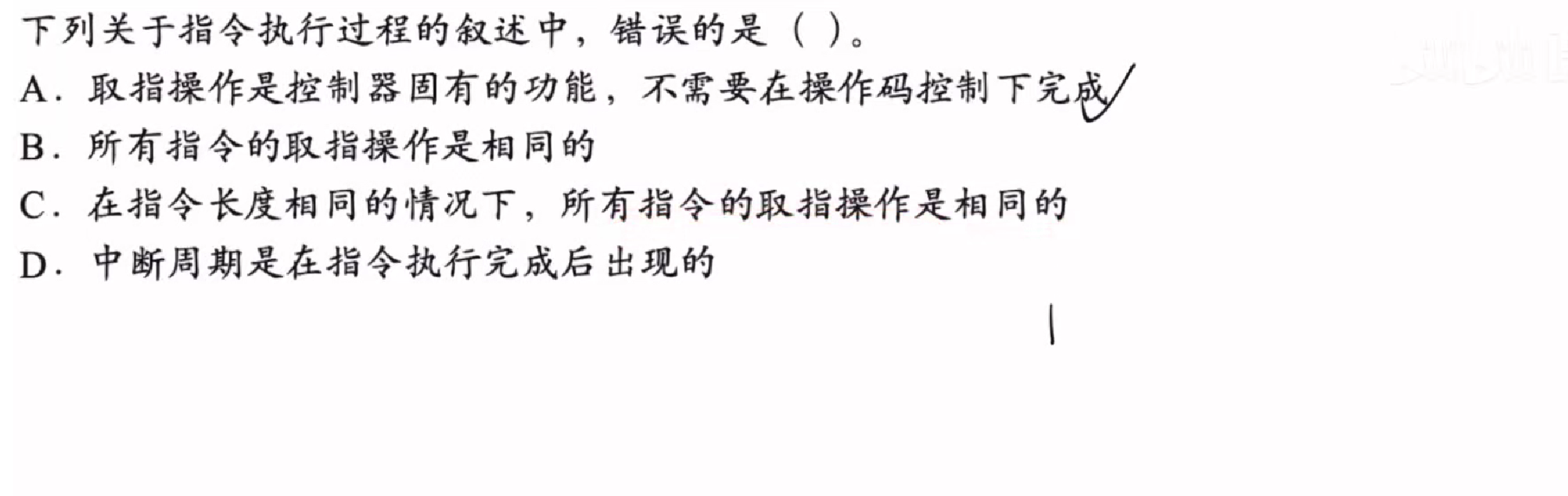

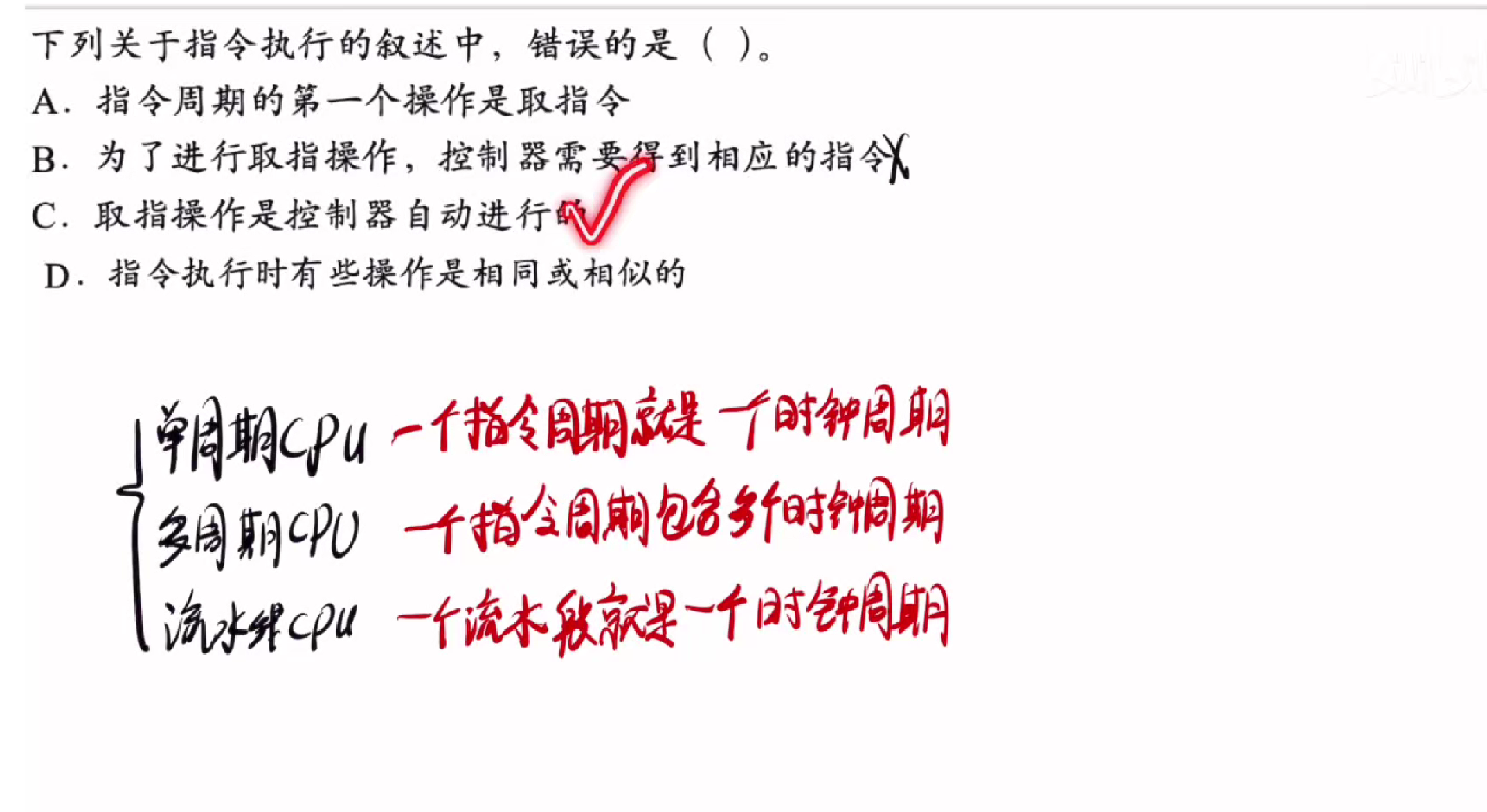

指令长度可能不同,有些指令可能只占用一个字节,有些两个

答案:C

取指令不需要得到相应的指令

答案:B

即如下所示的控制器等等部件

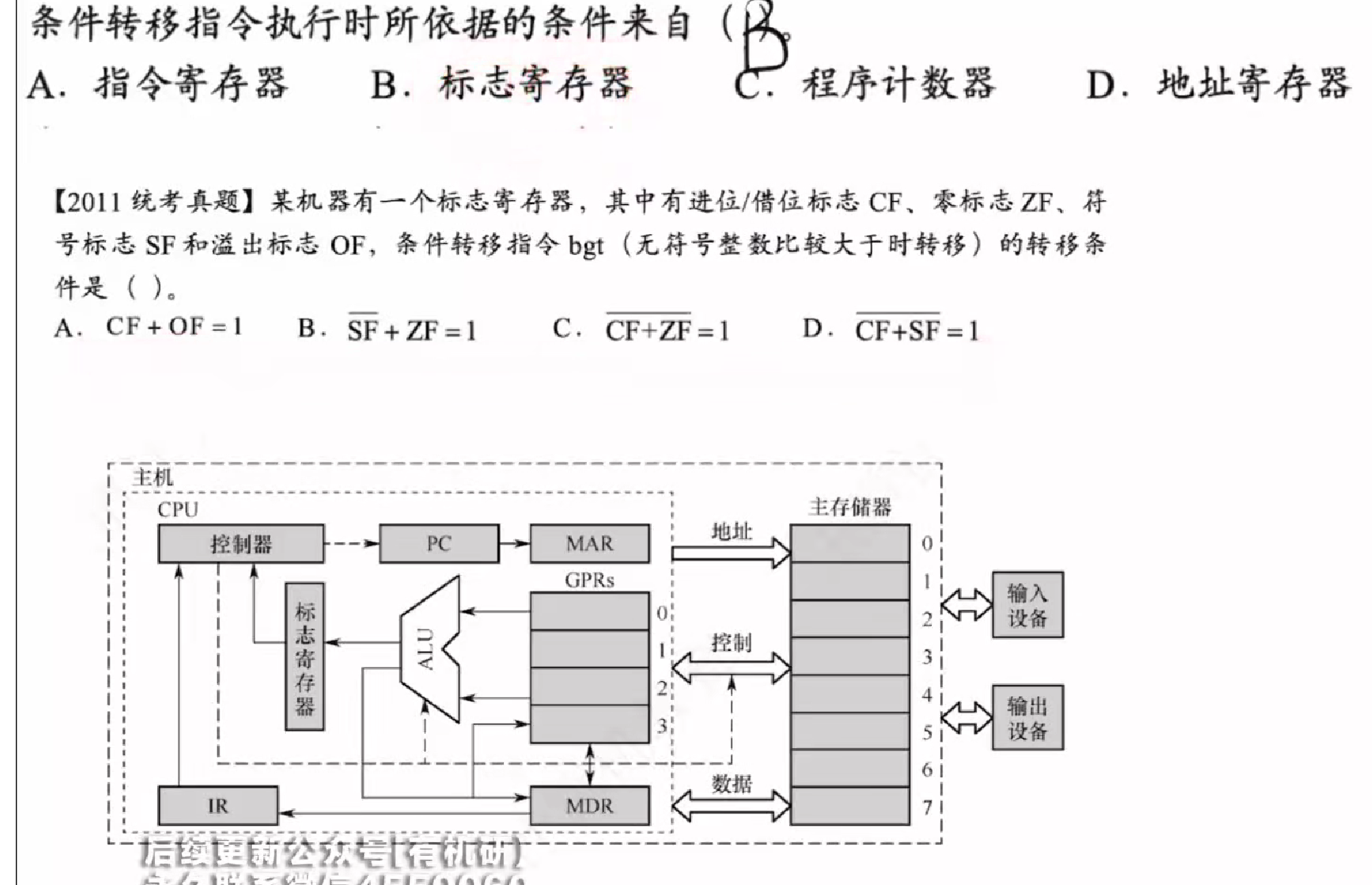

其中标志寄存器代表的是运算结果,可能就是比大小然后进行条件转移指令的前提条件

答案:C

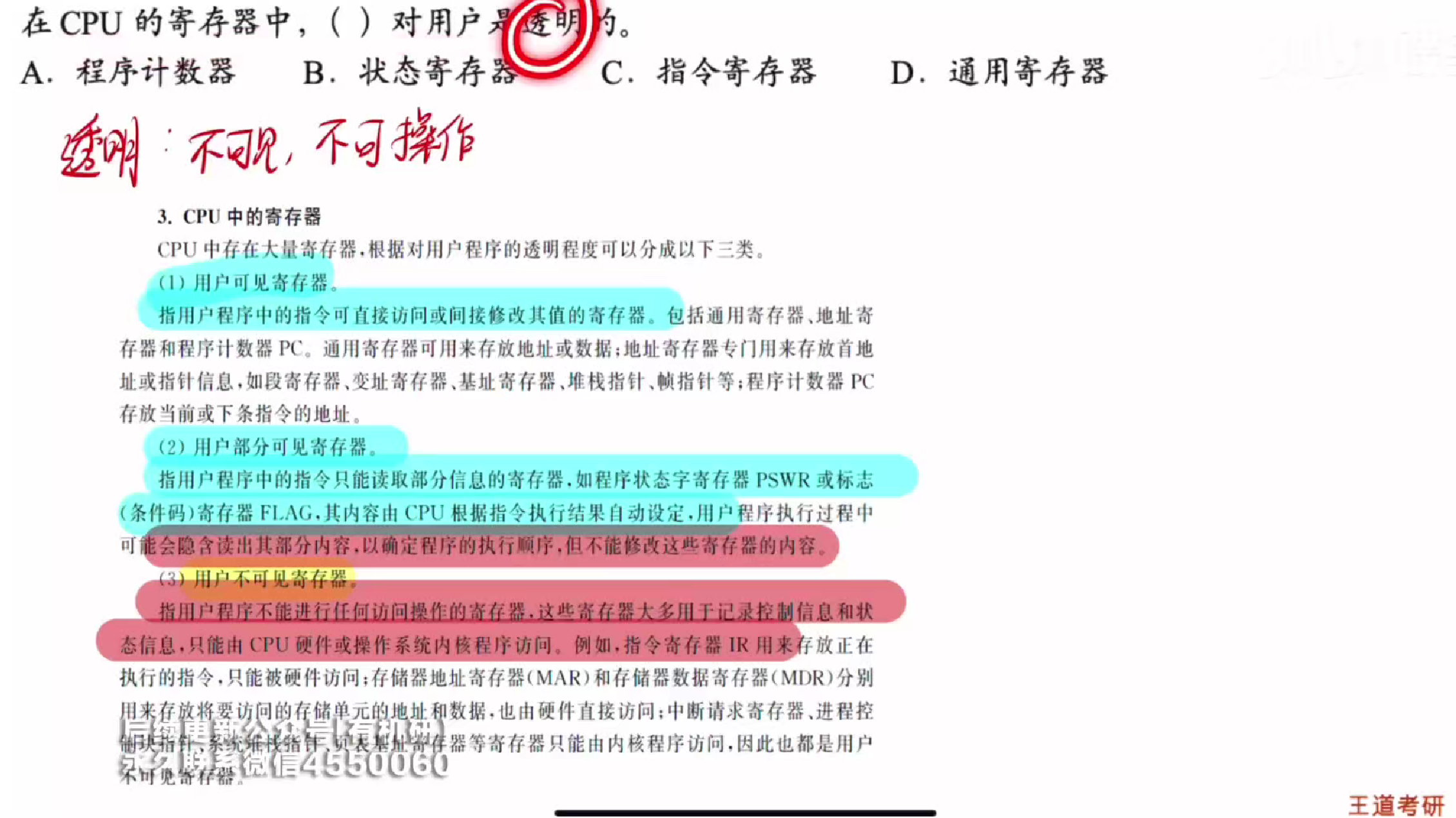

各个寄存器的透明性如下所示

浙公网安备 33010602011771号

浙公网安备 33010602011771号