芯片Layout中的Guard Ring

最后修改日期:2023/10/25

1. 简介

在CMOS模拟版图中,常常用Guard Ring将若干个MOS管(一般来说,一个Gurad Ring内部的MOS管都是同型的,即都是PMOS/NMOS)包围起来,起到保护作用。在芯片layout设计时,在面积允许的情况下要多放置一些Guard Ring,以提高芯片的性能。

2. Guard Ring在layout中的形式

2.1. 一般CMOS工艺的特点

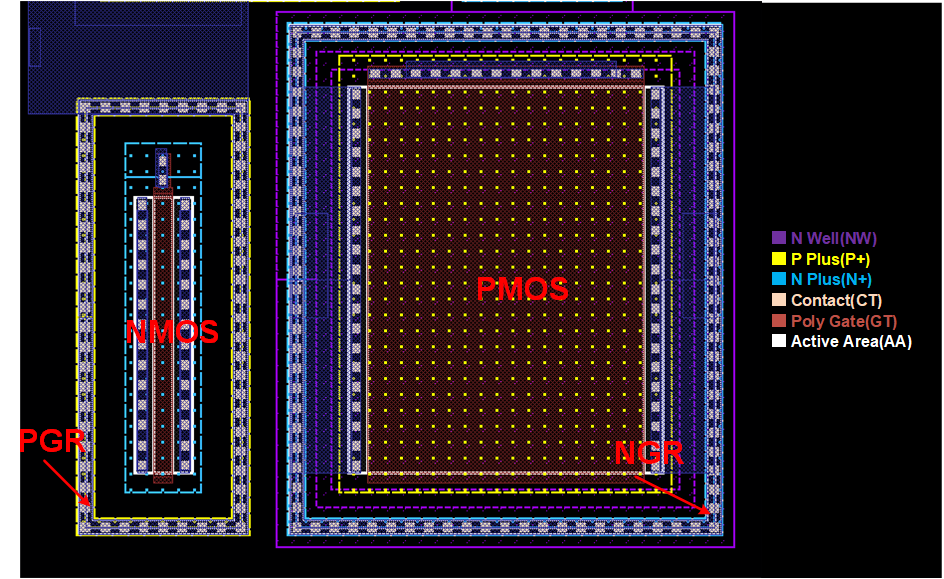

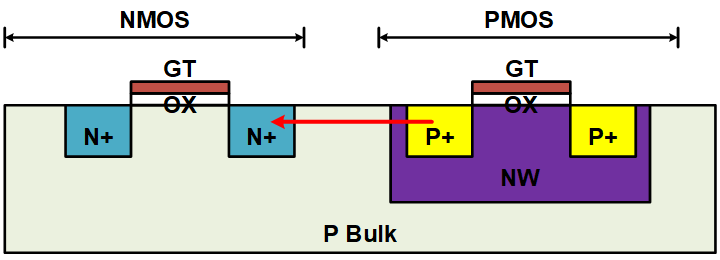

在一般的CMOS工艺中,整个基底都是P型半导体,所以制作NMOS直接在基底上制作。而PMOS的基底是N型的,因此需要先在巨大的P型基底上先制作N阱(N Well),再在N阱中制作PMOS。

-

Active Area就是会生成MOS的区域。AA与GT相交就构成一个MOS。但是实际上在工艺中AA代指什么还不确定,因为不确定工艺的隔离工艺是什么。我的推测是:MOS的硅区与上方的Metal之间总是有氧化层的,而AA位置对应的氧化层较薄,因此GT能对AA区的硅形成控制。这个做法类似于STI或者LOCOS工艺。

从GF180(singapore)的User Manual中能看出使用的隔离工艺就是STI。 -

Contact是接触孔,可以理解为连接Active Area和Metal 1,也即通过Contact可以控制一块Active Area的电平。

2.2. P Gurad Ring(PGR)

P Guard Ring用来保护NMOS器件。PGR本身由P+中的AA组成,CT是用来控制PGR的电平的(一般为VSS)。

2.3. N Gurad Ring(NGR)

又称Well Guard Ring,因为其由N+中的AA组成,而N+必须存在于NW中。CT作用同理,电平一般为VDD。

3. 闩锁效应/可控硅效应/晶闸效应(Latch-up)

Guard Ring的一个重要作用就是抑制闩锁效应。

3.1. Layout中的闩锁模型

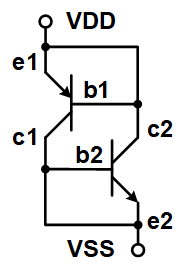

如上图展示了直接制作一对靠近的PMOS和NMOS的工艺截面。注意红色箭头,其依次经过了P+、N、P、N+区域,即可以简化为如下的模型[1]:

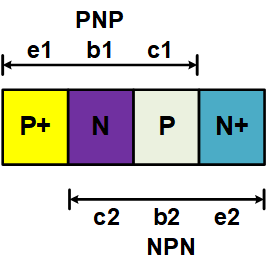

BJT器件有三个端子,分别是:基极(b)、集电极(c)、发射极(e)。PNP管的ebc分别由P++、N、P+制作,而NPN管的ebc分别由N++、P、N+制作。类比BJT的结构,可以发现其实际上等效于一个PNP和一个NPN。

在区分好e、b、c之后,上图可以转化为以下的电路图。不妨认为e1、e2接的电压分别是VDD、VSS。

已知BJT的特点是:e、b、c的流经电流之比是\((\beta+1):1:\beta\)。不需要严格计算,可以进行如下分析:

假设电路中出现了一个偶然的噪声电流\(i_{b2}\),那么\(i_{c2}=i_{b1}\)增大,那么\(i_{b2}\)也会增大。至此已经形成正向反馈,电流会越来越大。当然,这个正向反馈不可能是无穷大的,肯定有一个终止状态,我们不关心什么时候终止,只需要知道终止状态有以下的特点:

- 电流非常大

- 这个状态不可能自动解除,唯一的办法是关闭电源,即断开VDD

- 极大的电流会影响电路的性能、功耗表现,甚至导致烧毁

这就是闩锁效应/可控硅效应/晶闸效应,对应的器件称为可控硅器件/晶闸管。

这个效应并非一无是处。一个典型的正面应用例子就是触摸开关:当人触摸开关时提供了一个极小的电流,这个极小的电流通过可控硅效应将整个电路启动,并在松手后依然能维持在工作状态。

3.2. 闩锁效应对芯片的危害

闩锁在芯片电路中自然是有害的,因为它导致了很大的且并不必要的电流。更要命的是,在芯片中我们不可能断开VDD,因此无法中止闩锁效应。因此最重要的就是避免产生闩锁效应的可能性。

4. Guard Ring对闩锁效应的抑制

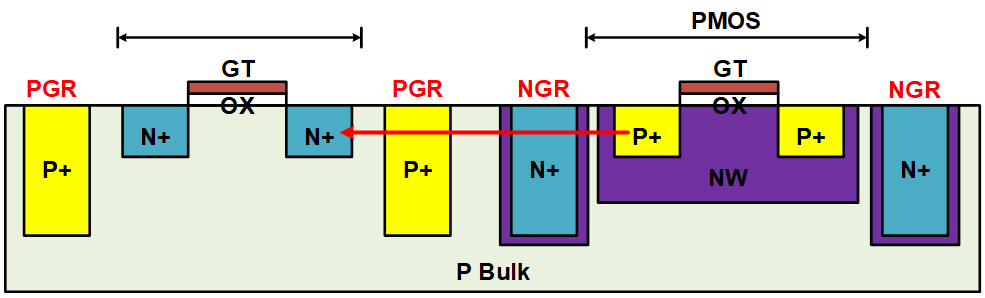

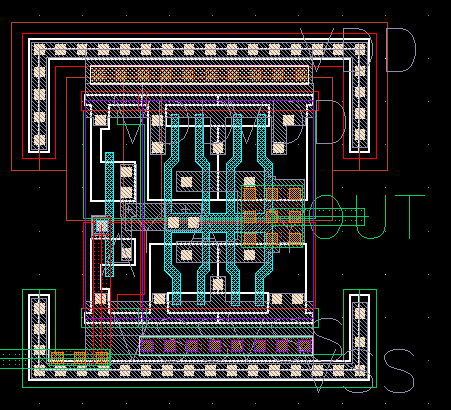

前面已经分析过PGR、NGR的结构。上图展示了加上了PGR、NGR之后的截面。

首先需要解释图中因PGR导致的P\(\to\)P+和因NGR导致的N\(\to\)N+欧姆接触。

4.1. 欧姆接触

这里不做太多的解释,只是简单提一下。

在半导体中,半导体的电平都是通过过孔打到金属上,再最终引出控制的,因此我们希望金属与半导体的接触是低阻的,不具有半导体效应。

4.1.1. 金属-半导体结接触

关于金半结接触,可能产生两种结果:形成阻挡层、形成反阻挡层[2]。

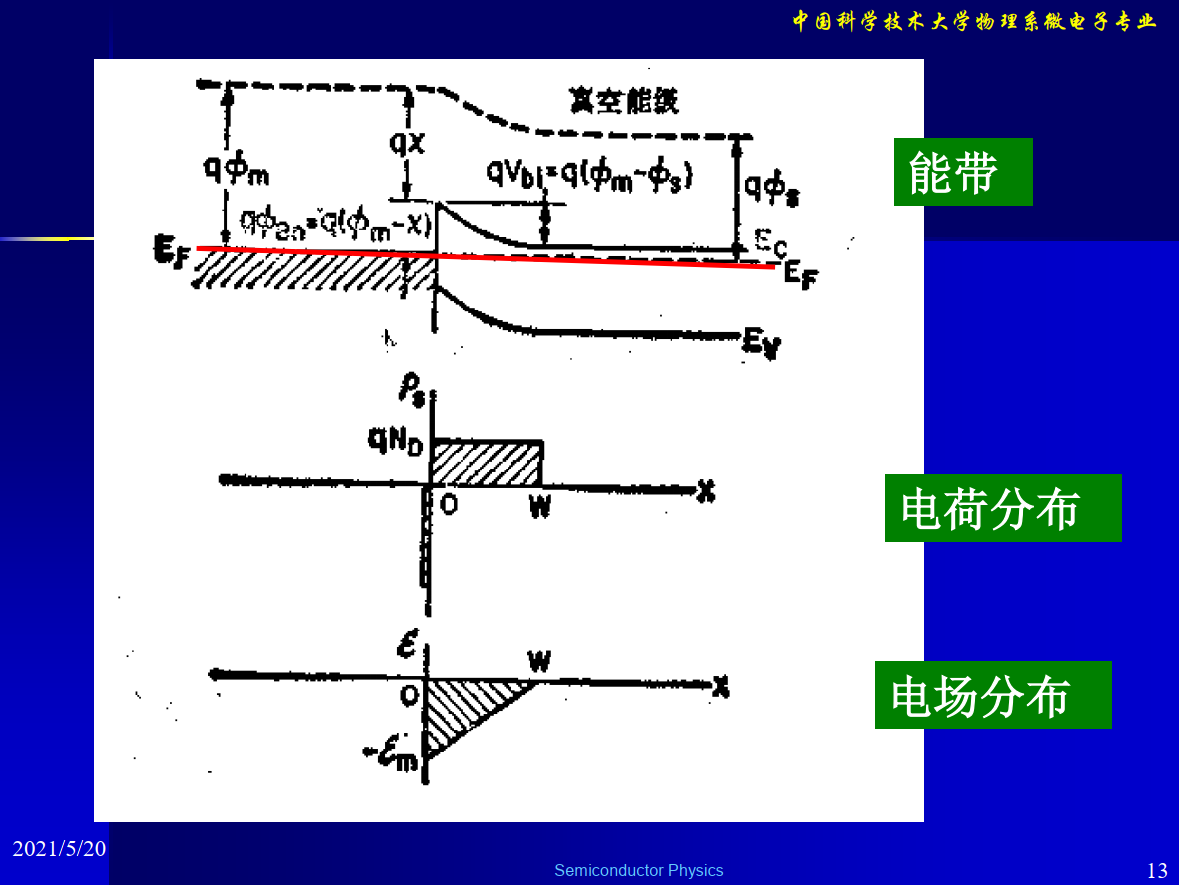

形成阻挡层:

在未接触的情况下,若金属的功函数大于半导体功函数(即金属中的电子需要更大的能量才能逸出),所以金属的Fermi能级小于半导体Fermi能级。当金属与半导体接触时,半导体中的电子将向金属流动(因为Fermi能级趋于一致),因此半导体在接触表面处的正电荷(空间电荷)密度增加,所以产生了从半导体内部指向表面的电场,所以能级从表面到半导体内部是降低的。所以半导体表面能级向上翘,形成了阻挡层。此时在金半结附近是空间电荷区(高阻,且具有类似PN结的特性)。

形成反阻挡层:

在未接触的情况下,若金属的功函数小于半导体功函数(即金属中的电子需要更大的能量才能逸出),所以金属的Fermi能级大于半导体Fermi能级。当金属与半导体接触时,金属中的电子向半导体中流动(因为Fermi能级趋于一致),因此半导体在接触表面处的电子(载流子)密度增加,所以产生了从半导体表面指向内部的电场,所以能级从表面到半导体内部是升高的。所以半导体表面能级向下弯,形成了反阻挡层。此时在金半结附近是载流子区(低电阻,通常可以忽略)。

半导体Fermi能级的表达式为

其中\(E_c, E_v\)是导带底、价带顶的能级;\(k\)是Boltzmann常数;\(m^*_p, m^*_n\)分别是空穴、电子的有效质量。因此,半导体的Fermi能级是较难改变的。即使选择不同种类的半导体,它们的Fermi能级都还是比金属高。因此想要使金半结达到第二种情况而达成低阻接触的目的,是很困难的。

4.1.2. Schottky接触

当半导体与金属接触形成第一种情况时,二者构成Schottky结,对应的器件就是Schottky二极管。

4.1.3. 欧姆接触

前面说到了,金半结很难达到第二种状态。那么为了趋近于低阻状态,常常将半导体的掺杂浓度提高,这样半导体的空间电荷区的电荷密度更大,所以电场更强,能级弯曲得更厉害,也就是说势垒的厚度变小了。而当势垒厚度极小时,量子隧穿效应就占据主导了,金半结的电流主要是较大的隧穿电流,结电流相较而言就较小,因此也体现出低阻的特性。这种做法称为欧姆(Ohmic)接触。

4.1.4. 欧姆接触用于Guard Ring

简单来说,在半导体中,P\(\to\)P+\(\to\)Metal或N\(\to\)N+\(\to\)Metal都是欧姆接触。在上图中PGR、NGR都满足欧姆接触,因此Guard Ring连接的金属与Guard Ring之间只是个小电阻。

一般来说,PGR、NGR连接的电平分别是VSS、VDD,欧姆接触保证了Guard Ring被强拉到对应的电平值,而没有其它的半导体效应。

4.2. 引入Guard Ring后的闩锁电路

看上图中的红色箭头,不能说P+、N、P、N+这条路线不复存在了,只是上面有两个点被Guard Ring欧姆接触拉到了固定电平。由此可以得到电路图:

在以上的电路中,\(v_{e1,b1}=0, v_{b2,e2}=0\),也就是说两个BJT根本不会打开,闩锁效应也就不存在了。

实际上,如果欧姆接触没那么理想,那么b1、b2可能并不是被拉到VDD、VSS,但终归是接近VDD、VSS的值,在一定的范围,BJT的发射结依然是不会打开的,因此也不会有闩锁效应的。

5. Layout中Guard Ring的设计规范

5.1. Guard Ring是否必须封闭

如上图,PGR、NGR都是不完整的环,并不能说这样做一定不行,但肯定不是最好的做法。前面也说了,在面积、版图排布允许的情况下最好多画、画完整的Guard Ring。那么不完整的环会产生多大的影响,就需要自己斟酌了。

一般来说,这种不成环的Guard Ring不会用于大面积模块周围的,不完整Guard Ring的最大目的就是为了节省走线资源,避免过早地使用高层金属。

5.2. Guard Ring的类型

NMOS周围是PGR,PMOS周围是NGR(或称为Well Guard Ring)。当然最好的情况是:不论MOS类型,都在外面套两层Guard Ring,类型不同。

5.3. Guard Ring的包围距离(Enclosure)

DRC允许的情况下,当然是越近越好。Guard Ring更近,意味着欧姆接触更近,所以b1、b2被拉到的电压就越接近VDD、VSS,抑制闩锁效应就越彻底。

EDAboard forum: Why are double guard rings used ↩︎

《半导体物理学(第7版)》,刘恩科等,电子工业出版社 ↩︎

浙公网安备 33010602011771号

浙公网安备 33010602011771号