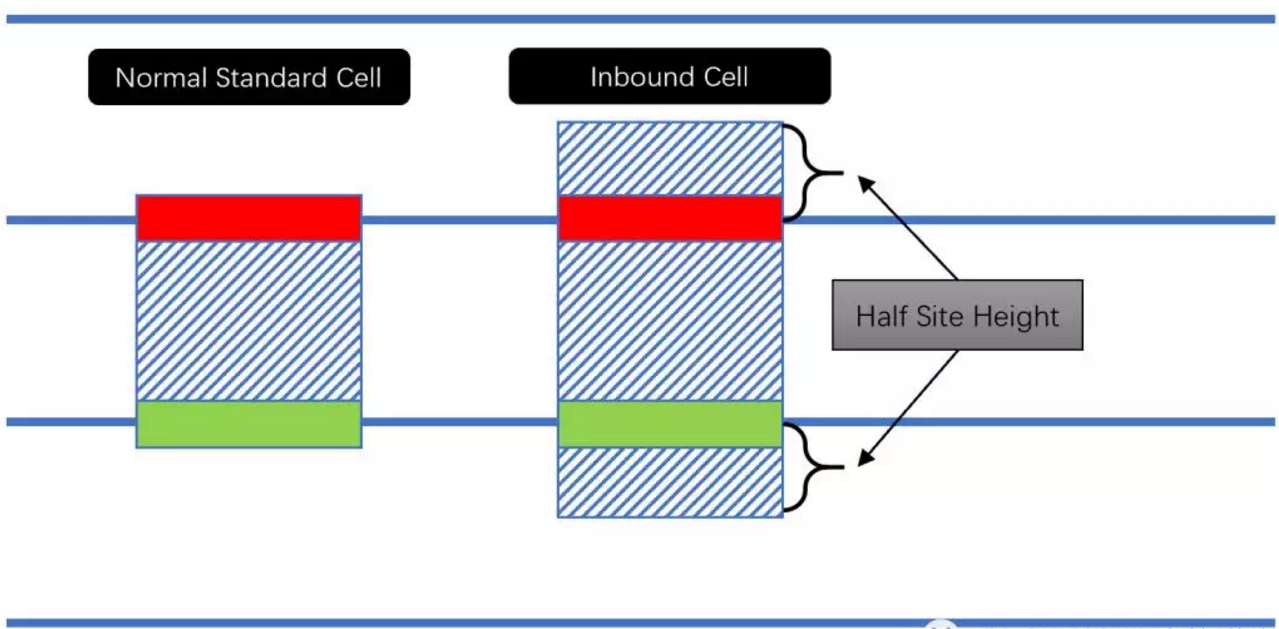

所有cell都被做成宽和高有一定规律的矩形,也就是所谓的标准单元。在一般工艺中,所有的标准单元的高度都和site row的高度相同或者是其整数倍,且上下边缘必定与site row重合,如下面左图所示。但是在某些尖端工艺中,出现了下面右图中的所谓Inbound Cells。

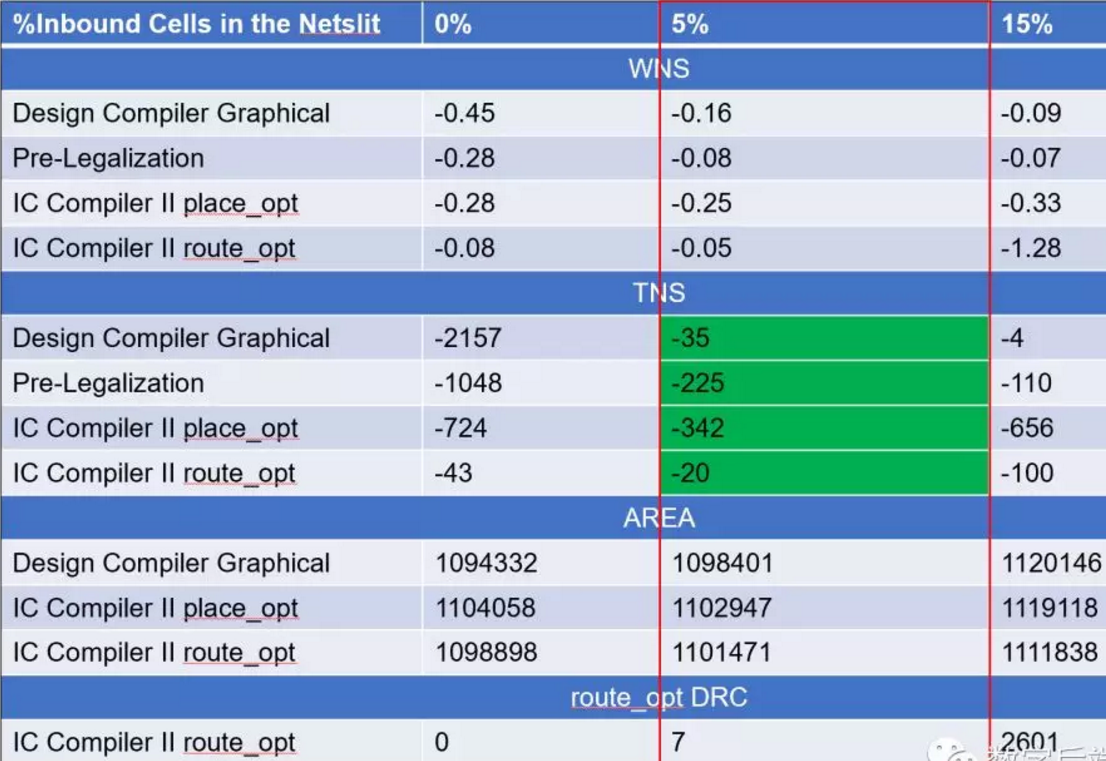

Inbound cells可能会比一般的cell快一些,但是在legalization方面可能会引起一些问题。尽管如此,在design中使用一定数量的inbound cell,可以在不影响芯片其他方面的同时,改善timing结果。下面容我盗图一张,介绍一下Synopsys官方在这方面做出的比较。下图展示了同一个design中inbound cells所占的比例,从左到右依次为0%, 5%和15%。鉴于DCG(Design Compiler Graphical)中inbound cells已经得到支持,我们可以看到,从综合一路到route_opt,当design中的inbound cells比例在5%左右的时候,design的Timing得到了比较好的改善,同时在Area和DRC方面没有明显恶化。

其实个人认为这种cell的出现可能预示这一个趋势,随着工艺的复杂度提升,需要整个芯片设计流程提供更多的变通方法来适应日渐复杂的工艺挑战,甚至包括把曾经的"标准"单元变得不再标准。

目前本人接触到的55nm-7nm工艺中还没有看到在后端中使用inbound cell的design,尚不明确在实际设计中还会遇到哪些问题。但是,可以猜测的是,所谓5%的比例应该并不是一个通用性指标,不同设计中可能需要更多的尝试才能找到比较合适的比例。

浙公网安备 33010602011771号

浙公网安备 33010602011771号