一、计算机系统概述

计算机硬件的基本组成

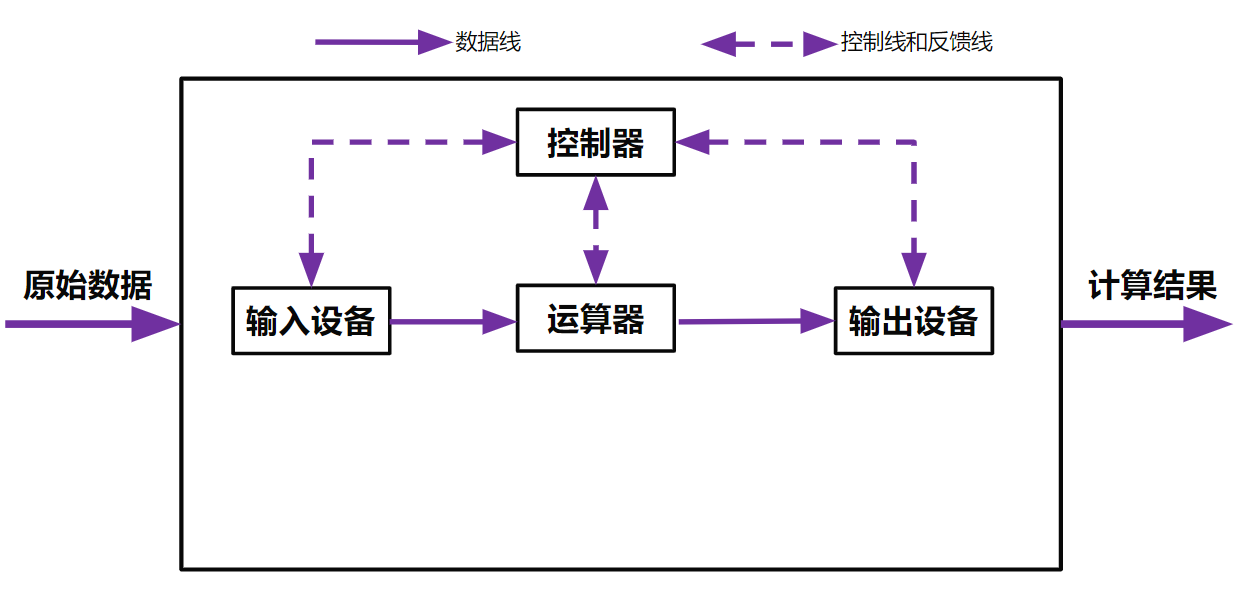

基本计算机

只有以下四个硬件,设备就能正常运行。

- 控制器

- 输入设备

- 运算器

- 输出设备

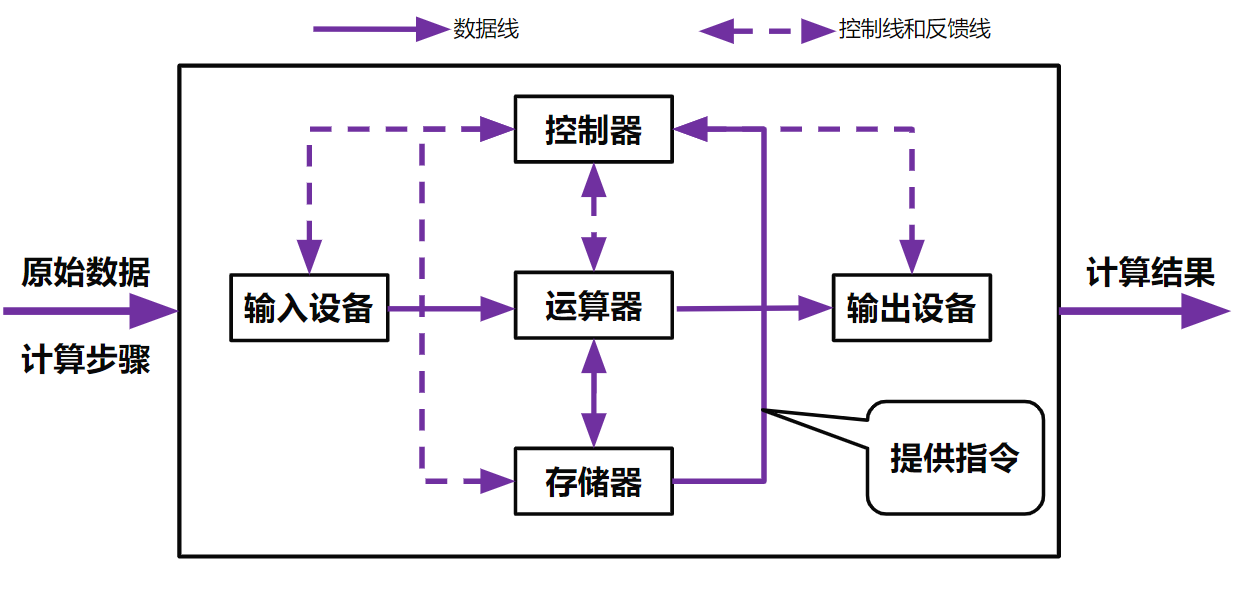

早期冯诺依曼机

缺点: 现在工作模式是:等待输入数据,然后人等待输出数据,然后计算机才能输入数据...

为了避免浪费计算资源, 减少等待,引入存储器,就是典型的早期冯诺依曼机

存储器用于批量处理数据,具体功能如下:

- 把需要的 计算数据+计算步骤 提前放入存储器

- 把运算器的中间结果临时放在存储器

指令和指令

指令

作用:控制控制器的操作

形式:操作码+地址码

例如:

程序就是指令的集合

注意:

冯·诺依曼计算机中指令和数据均以二进制形式存放在存储器中,CPU区分它们的依据是指令周期的不同阶段

有一个问题:由于计算机发展快速,现有一个4位运算器,如何运行8位计算?

方法1: 买8位运算器。

方法2. 利用软件将8位分割为两个4位(人工输入分割指令),然后再进位处理即可。

因此:软件和硬件在逻辑上是等效的。(也就是说一件事情可用软件实现,也可以用硬件实现, 效果是一样的)(不能说是等价的,一般来说硬件实现速度快,但是实现复杂)

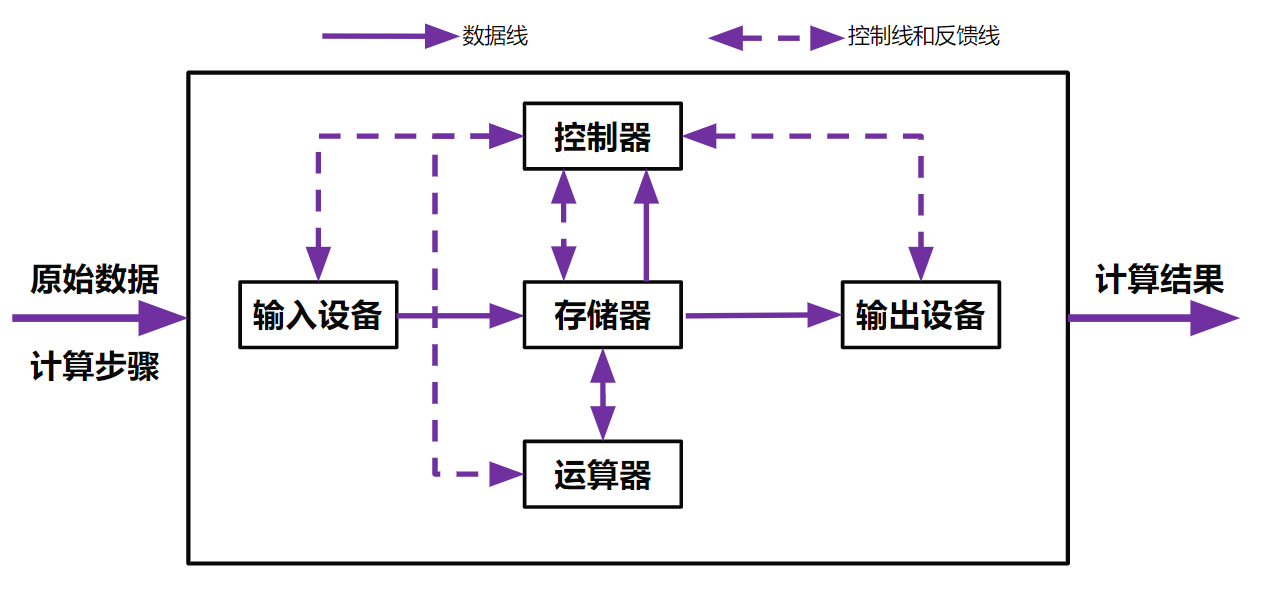

现代的计算机

早期冯诺依曼机问题:当指令提前存放在存储器时,运算器需要暂停,帮助存储器搬运指令,占用了运算器的资源。

因此现代计算机,以存储器为中心,硬件框图如下:

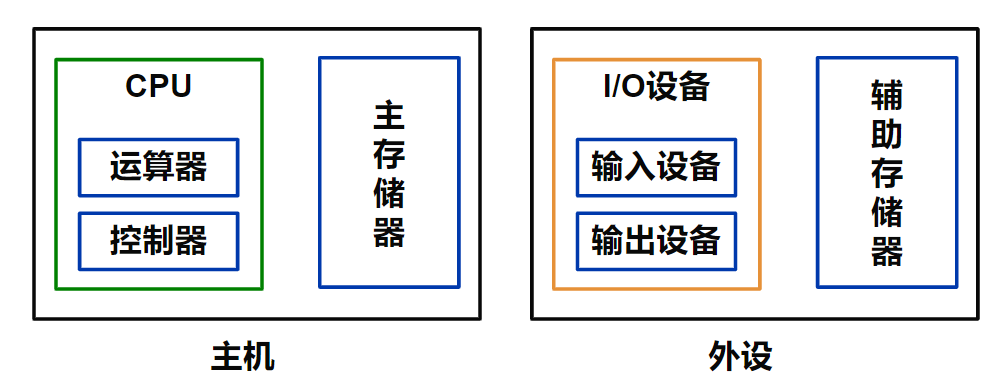

硬件组成要素

设计结构如下:其中运算器和控制器 因为设计相识常被设计在一起,成为CPU。

假设给一个算盘、一张带有横格的纸和一支笔,要求我们计算y=ax+b-c这样一个题目。

算盘----运算器

纸----存储器

笔----IO设备

大脑----控制器

运算器

功能:算术运算和逻辑运算(在计算机中参与运算的数是二进制的)

MQ(Multiple-Quotient Register):乘商寄存器,在乘、除运算时,用于存放操作数或运算结果。

ACC(Accumulator):累加器,用于存放操作数,或运算结果。

ALU(Arithmetic and Logic Unit):算术逻辑单元,通过内部复杂的电路实现算数运算、逻辑运算

通用寄存器:用于存放操作数,X表示当前正在用的操作数。

PSW (Program Status Word):程序状态字寄存器:存放运算产生的初步的结论,例如有没有溢出,有没有错误等等。

控制器

功能: 计算机中发号施令的部件,它控制程序的前后顺序的执行。

CU(Control Unit):分析指令,给出控制信号

IR(Instruction Register):存放当前执行的指令

PC(Program Counter):存放指令地址,有自动加1功能(理解逻辑是可以认为:PC里面永远是下一条指令的位置。)

存储器

功能: 存储数据和程序(指令)

本节主要指 主存储器

存储器的基本结构:

- 存储体:存储数据

- 地址寄存器 MAR(Memory Address Register):定位数据

- 数据寄存器 MDR(Memory Data Register):存储器和外界的缓冲。

适配器与I/O设备

输入设备:

把人们所熟悉的某种信息形式变换为机器内部所能接收和识别的二进制信息形式

输出设备:

把计算机处理的结果变换为人或其他机器设备所能接收和识别的信息形式

适配器:

它使得被连接的外围设备通过系统总线与主机进行联系,以便使主机和外围设备并行协调地工作

因为CPU速度快,IO设备速度慢,因此不能直接相连,需要一个过度。适配器就是起缓冲作用,也相当于一个转换器。

总线:

构成计算机系统的骨架,是多个系统部件之间进行数据传送的公共通路。

计算机的工作过程 – 取数指令

前提: 操作符号的含义

M:主存中某存储单元

ACC、MQ、X、MAR、MDR…:相应寄存器

M(MAR):取存储单元中的数据

(ACC)…:取相应寄存器中的数据

指令=操作码+地址码:操作码告诉我们操作是什么,地址吗告诉我们数据的地址是什么。

- OP(IR):取操作码

- Ad(IR):取地址码

初:(PC)=0,指向第一条指令的存储地址

1. 取指令

1:(PC) \(\to\) MAR,导致(MAR)=0

3:M(MAR) \(\to\) MDR,导致(MDR)=000001 0000000101

4:(MDR) \(\to\) IR,导致(IR)=000001 0000000101

2. 分析指令

1:OP(IR) \(\to\) CU,指令的操作码送到CU,CU分析后得知,这是“取数”指令

2:Ad(IR) \(\to\) MAR,指令的地址码送到MAR,导致(MAR)=5

3. 执行命令

1:M(MAR) \(\to\) MDR,导致(MDR)=0000000000000010=2

2:(MDR) \(\to\) ACC,导致(ACC)=0000000000000010=2

因此:CPU区分指令和数据的依据:指令周期的不同阶段

软件系统

软件系统分为两种:系统软件和应用软件

系统软件:管理整个计算机系统,使系统资源得到合理调度

常见软件:

- 语言处理系统。如汇编程序、编译程序、解释程序等

- 操作系统(OS):管理计算机系统的软硬件资源。

- 服务性程序。如诊断程序、排错程序、练习程序等

- 数据库管理系统(DBMS)

- 网络软件:管理网络相关

应用软件: 完成用户的特定任务,使用系统软件提供的资源接口。

常见软件:QQ、微信、Word、PowerPoint、Excel...

计算机编程语言

机器语言:二进制代码 0000,0000,000000010000

代码,操作

汇编语言:助记符 LOAD A, 16

16号单元数据与17号单元数据相加存回17号单元:

LOAD A, 16

LOAD B, 17

ADD C, A, B

STORE C, 17

汇编程序(汇编器):将汇编语言一一对应的翻译成机器语言。

高级语言:C/C++/Java c = a + b

d = a + b

e = b + c

…

编译程序(编译器):将高级语言转化到汇编语言。

将高级语言转化到机器语言有两种方式:

- 编译程序:一次将代码全部转化为机器语言。(优点:可以做优化,相同的操作可以合并)

- 解释程序:运行哪里,转化哪里的高级语言。(优点:指哪打哪)

注意区分汇编程序 和 用户用汇编语言写的程序。

计算机系统的层次结构

计算机是一个十分复杂的硬、软件结合而成的整体。它通常由五个以上不同的级组成,每一级都能进行程序设计。

层次结构的形成原因是 简化操作 ,通过 封装 来实现。

系统软件通过硬件提供的接口达到一定的功能。

应用软件通过系统软件提供的接口实现一定的功能 。

虚拟机器角度

例如对于编程

操作系统机器:分配资源,虚拟化硬件,减少资源冲突,避免死机。

微指令系统:将机器语言分割化,利于硬件编程。使用微指令控制指令执行的先后顺序,提高并发。

注意:软件和硬件的界限并不绝对,可以相互接管,逻辑上是等价的,因此是条 虚线。

程序设计角度

每一级都能进行程序设计。

第一级是微程序设计级(逻辑电路级)。这是一个实在的硬件级,它由机器硬件直接执行微指令。如果某一个应用程序直接用微指令来编写,那么可在这一级上运行应用程序。

第二级是一般机器级,也称为机器语言级,它由微程序解释机器指令系统。这一级也是硬件级。

第三级是操作系统级,它由操作系统程序实现。这些操作系统由机器指令和广义指令组成,广义指令是操作系统定义和解释的软件指令,所以这一级也称为混合级。

第四级是汇编语言级,它给程序人员提供一种符号形式语言,以减少程序编写的复杂性。这一级由汇编程序支持和执行。如果应用程序采用汇编语言编写时,则机器必须要有这一级的功能;如果应用程序不采用汇编语言编写,则这一级可以不要。

第五级是高级语言级,它是面向用户的,为方便用户编写应用程序而设置的。这一级由各种高级语言编译程序支持和执行。

存储器

功能: 存储数据和程序(指令)

基本结构:

物理存储方式(其中一种实现方式)

这样的存储数据的单元称为:存储元。

包含两部分:

- 电容: 存储数据0/1

- 控制器件: 一个开关器件。

读操作

如果外部传入1(闭合操作)就闭合开关,电容存储的1(数据),就随着电流流出,实现读操作。

写操作

如果外部传入1(闭合操作)就闭合开关,待写数据1,就自动的施加到电容,实现写操作。

存储体

基础定义

一行存储元,组成存储单元。

多个存储单元,组成存储体。

一个存储单元存储的0/1数据,成为一个存储字。

一个存储字的位数,成为存储字长。(单位是bit,Byte)

注意: 每个存储体,最多有一个存储单元的输入信号为1(闭合操作)(如果有多个开关闭合,输出的从存储字就会错误)。

译码器

很容易发现此时的编号01...00很像二进制地址,但还不是,还需要借助译码器,才能得到二进制地址。

很明显,通过n位的译码器就可以操作有\(2^n\)个存储单元的存储体。

也就是:

n位地址\(\to 2^n\)个存储单元。

而且显然 一个存储体的总容量(一个存储体容纳多少二进制位),就是\(长乘宽\)。

即:\(总容量=存储单元个数×存储字长=2^n×存储字长(bit)\)

注意:

MAR和MDR在逻辑上属于主存,但在实际实现时封装到CPU。

计算机 性能指标

容量(存储器)

当存储器加入译码器后,设计图如下:

显然,译码器位数,决定了地址的最大位数,也就是地址的数量。

因此若为n位地址,系统能支持的最大容量 = \(2^n ×存储字长\)

又因为:MDR位数=存储字长=每个存储单元的大小

所以MDR 和 译码器 决定了系统的最大容量

速度(运算器)

机器字长: 计算机进行一次整数运算所能处理的二进制数据的位数

强调一次的原因:硬件和软件在逻辑上时等价的,一个32位cpu,可以通过分割,进位,通过多次运算,计算出64位的数据。

有个有趣的问题:

是不是机器字长越大越好?

基础概念:

cpu通过 统一的时钟信号CLK 协调各个硬件。

其中某一段称为CPU时钟周期,其倒数称为CPU时钟频率(主频)。

再引入一个概念:CPI(Clock cycle Per Instruction):执行一条指令所需的时钟周期数。

这样通过就可以知道某指令耗时= \(CPI × CPU时钟周期\)

分析:

我们知道,每条指令都是耗时的。

假设每次只能处理1个二进制位,可以通过编程完成8位的运算:指令1,指令2 … 指令8

整个程序CPU耗时 = 指令1耗时+指令2耗时+…+指令8耗时

= (指令1的CPI+指令2的CPI+…+指令8的CPI) × CPU时钟周期

\(= 平均CPI ×指令条数×CPU时钟周期\)

因此显然CPU位数越大需要执行的指令就越多,因此 机器字长 不是越大越好。

IPS

IPS(Instructions Per Second),即每秒执行多少条指令。\(IPS= \frac{1}{1条指令耗时}= \frac{1}{CPI × CPU时钟周期}= \frac{主频}{CPI}\)

MIPS(Million Instructions Per Second),即每秒执行多少百万条指令。 \(MIPS=\frac{指令条数}{执行时间×10^6} = \frac{主频}{CPI}\)

MFLOPS(Mega Floating-point Operations Per Second),即每秒执行多少百万次浮点运算。MFLOPS=浮点操作次数/(执行时间× 106)。

GFLOPS(Giga Floating-point Operations Per Second),即每秒执行多少十亿次浮点运算。MFLOPS=浮点操作次数/(执行时间× 109)。

TFLOPS(Tera Floating-point Operations Per Second),即每秒执行多少万亿次浮点运算。MFLOPS=浮点操作次数/(执行时间× 1012)。

带宽、吞吐量和响应时间

数据通路带宽:数据总线一次所能并行传送信息的位数

吞吐量:指系统在单位时间内处理请求的数量。(衡量整个系统批量处理能力)

它取决于信息能多快地输入内存,CPU能多快地取指令,数据能多快地从内存取出或存入,以及所得结果能多快地从内存送给一台外部设备。这些步骤中的每一步都关系到主存,因此,系统吞吐量主要取决于主存的存取周期。

(通过将数据量小的操作向前排列,操作大的操作像后排,可以提高吞吐量,但是会出现饥饿)。

响应时间:指从用户向计算机发送一个请求,到系统对该请求做出响应并获得它所需要的结果的等待时间。(衡量交互性能)

通常包括CPU时间(运行一个程序所花费的时间)与等待时间(用于磁盘访问、存储器访问、I/O操作、操作系统开销等时间)。

浙公网安备 33010602011771号

浙公网安备 33010602011771号